模拟电路中的PLL应用:理论与实践相结合的技巧与策略

发布时间: 2025-01-03 01:10:56 阅读量: 9 订阅数: 15

C2000,28335Matlab Simulink代码生成技术,处理器在环,里面有电力电子常用的GPIO,PWM,ADC,DMA,定时器中断等各种电力电子工程师常用的模块儿,只需要有想法剩下的全部自

# 摘要

本论文深入探讨了锁相环(PLL)技术在模拟电路设计与应用中的原理和实践技巧。首先概述了PLL的基本工作原理和在模拟电路中的设计基础,包括其关键组成部分、相位检测器和压控振荡器(VCO)的工作机制。随后,详细分析了PLL的稳定性,提出了稳定性优化的技术和策略,并探讨了频率合成技术与相位噪声降低方法。在实践技巧章节,本文讨论了PLL模块的搭建与测试,面对环境干扰和设备老化问题的解决方案。最后,文章比较了数字PLL与传统PLL的优劣,并展望了PLL技术在集成电路、低功耗设计和新兴领域的应用前景。

# 关键字

锁相环;相位检测器;压控振荡器;环路稳定性;频率合成;数字PLL

参考资源链接:[PLL锁相环ADS仿真教程](https://wenku.csdn.net/doc/5c1r6avx74?spm=1055.2635.3001.10343)

# 1. PLL基本原理概述

## 1.1 锁相环技术简介

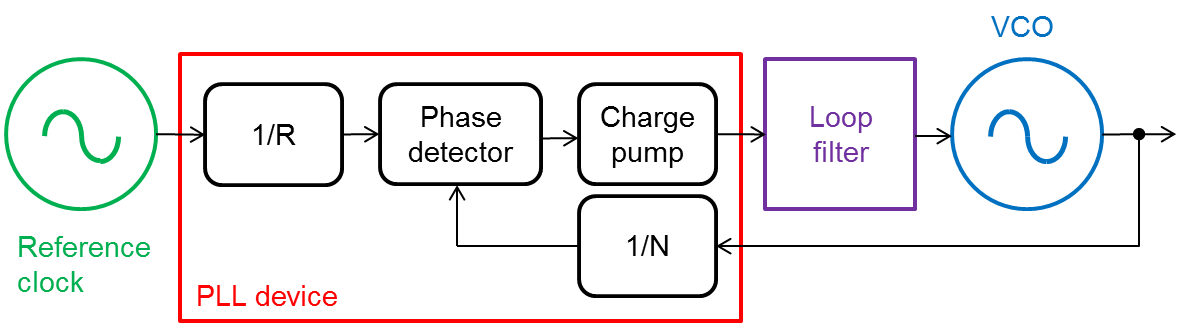

锁相环(PLL)是一种反馈控制电路,它能够使输出频率锁定在输入频率上。PLL广泛应用于通信、电子测量和计算机技术领域。它通过内部环路反馈机制来减少输出频率与参考频率之间的相位差,实现同步。从本质上讲,PLL包括三个基本组成部分:相位检测器(PD)、环路滤波器(LF)和压控振荡器(VCO)。

## 1.2 工作原理

相位检测器PD负责比较输入信号与VCO输出信号的相位,产生一个表示相位差的信号。环路滤波器LF的作用是滤除PD输出信号中的高频噪声和杂波,产生一个平滑的控制电压。VCO根据控制电压调整输出频率,与输入频率达成一致。整个过程是动态的,每当输入频率发生变化时,PLL都能自动调节,以保持频率和相位的锁定状态。

## 1.3 应用背景

PLL的应用范围非常广泛,包括但不限于无线通信、数字信号处理、时钟同步、频率合成和相位调制解调。随着集成电路技术的进步,PLL在系统中的集成度越来越高,其性能直接影响到整个系统的性能,尤其是在高速、高精度的通信系统中。理解PLL的基本原理是进行深入研究和优化设计的前提。

以上内容为第一章的概要性介绍,为读者简明扼要地勾勒出了PLL技术的轮廓,并指明了其在现代电子技术中的重要性和应用背景,为后续章节的深入讲解奠定了基础。

# 2. PLL在模拟电路中的设计与应用

在第二章中,我们将深入探讨PLL(Phase-Locked Loop)在模拟电路设计与应用中的具体细节。PLL技术是现代电子系统中不可或缺的一环,尤其是在需要同步信号、频率合成和噪声抑制的场合。

## 2.1 PLL电路的设计基础

PLL电路的设计涉及到多个关键组成部分,每部分都有其特定的功能和设计考量。

### 2.1.1 PLL的关键组成部分

PLL电路主要由三个核心部分组成:相位检测器(PD)、环路滤波器(LF)和压控振荡器(VCO)。

- **相位检测器(PD)**:此部分负责比较参考信号与VCO输出信号的相位,并生成相应的误差电压或误差脉冲。它对整个PLL的同步性能有决定性的影响。

- **环路滤波器(LF)**:通常是一个低通滤波器,它决定了PLL的动态响应特性,包括系统稳定性和锁定速度。

- **压控振荡器(VCO)**:这个部分将误差电压转换为频率变化,通过改变其振荡频率来跟踪输入信号的相位变化。

### 2.1.2 相位检测器的工作原理

相位检测器有多种实现方式,包括模拟乘法器、数字鉴相器、边沿触发器等。最简单的模拟实现是利用乘法器将两个输入信号相乘,再通过低通滤波器得到误差电压。数字鉴相器通常使用D触发器,它利用两个信号的上升沿来输出脉冲,脉冲宽度与两信号的相位差成正比。

### 2.1.3 压控振荡器(VCO)的调制机制

VCO是PLL中响应误差电压变化的部分。理想的VCO输出频率与输入控制电压线性相关,但实际中会有非线性效应。设计VCO时需要考虑的参数包括控制灵敏度、频率范围、相位噪声性能、电源和温度稳定性等。

## 2.2 PLL的稳定性分析

PLL的稳定性是其能否正常工作的重要指标。在设计时,需要深入分析系统稳定性并采取相应设计措施。

### 2.2.1 环路滤波器的设计要点

环路滤波器的设计对PLL性能至关重要。滤波器需要在保持系统稳定性的同时,尽可能地减少锁定时间。设计时,通常会使用一阶或二阶低通滤波器。一阶滤波器简单但可能无法提供足够的稳定性裕度,二阶滤波器在设计上更为复杂,但可以提供更好的性能。

### 2.2.2 系统稳定性的数学模型

系统稳定性可以通过根轨迹方法、奈奎斯特准则或者波特图来分析。通过这些工具,设计师可以预测系统在不同频率下的稳定性和响应时间。

### 2.2.3 稳定性优化的实战技巧

在实际设计过程中,我们可以通过调节环路滤波器的参数来优化系统的稳定性和锁定性能。例如,增加环路滤波器的带宽可以缩短锁定时间,但过宽的带宽可能会导致系统稳定性降低。

## 2.3 高级PLL技术应用

现代电子系统中对PLL的性能要求越来越高,这催生了一系列高级技术的应用。

### 2.3.1 频率合成技术

频率合成技术允许PLL生成一系列稳定的输出频率。在设计时,需要权衡合成速度、频率分辨率和相位噪声等参数。

### 2.3.2 相位噪声降低策略

相位噪声是影响PLL性能的关键因素之一。降低相位噪声通常涉及提高VCO的品质因数(Q),减少环路滤波器的噪声贡献,以及使用低噪声的参考源。

### 2.3.3 锁相环在通信系统中的应用案例

在通信系统中,PLL被广泛用于实现载波同步、时钟恢复和数据恢复等。通过适当的设计,PLL能够在提供同步的同时抑制噪声和干扰。

**表 2.3.3-1:PLL在通信系统中的典型应用**

| 应用领域 | 功能描述 | 设计挑战 |

| -------------- | ------------------------------------------------ | ------------------------------------------------ |

| 载波同步 |PLL能够跟踪和同步载波频率,确保信号的准确接收。 | 需要应对频率偏差、噪声及多径效应的影响。 |

| 时钟恢复 |PLL用于从接收到的数据信号中提取时钟信号。 | 要求高精度和稳定性,以避免时钟漂移。 |

| 数据恢复 |PLL可以同步数据位边沿,恢复出数据信息。 | 需要高速处理能力,应对信号的误码率和抖动问题。 |

**示例代码:**

```c

// 示例:PLL参数设置函数

void SetPLLParams(PLL_TypeDef *PLL, uint32_t mul, uint32_t div, uint32_t clk) {

// 设置乘数和分频参数

PLL->MUL = mul;

PLL->DIV = div;

// 应用设置并启动PLL

PLL->CR = PLL_CR_START | (mul << PLL_CR_MULLShift) | (div << PLL_CR_DIVShift);

while((PLL->CSR & PLL_CSR_LOCK) == 0); // 等待锁定

}

```

**参数解释:**

- `PLL_TypeDef *PLL`:指向PLL寄存器结构体的指针。

- `uint32_t mul`:乘数参数,控制VCO的振荡频率。

- `uint32_t div`:分频参数,用于降低输出频率。

- `uint32_t clk`:输出时钟频率。

**逻辑分析:**

此代码展示了PLL初始化和配置的基本流程。首先,设置PLL的乘数和分频值,然后通过CR寄存器启用了PLL。之后,通过检查CSR寄存器中的LOCK位来确认PLL是否已成功锁定。

本节内容展示了PLL在模拟电路设计中的核心原理和应用实例,为后续章节中深入讨论PLL的实践技巧和性能优化打下了坚实的基础。

# 3. PLL在模拟电路中的实践技巧

在理解了PLL(Phase-Locked Loop,锁相环)的基本原理和应用之后,本章将深入探讨PLL在模拟电路中的实际操作技巧。从模块的搭建与测试开始,探讨在实际应用中遇到的挑战以及解决这些挑战的方法。

## 3.1 PLL模块的搭建与测试

PLL的搭建与测试是一个要求高度精确和耐心的过程。设计者必须理解电路的每一个组成部分,并能够准确地测量和分析

0

0