【信号完整性测试】:基于PRBS的尖端技术与挑战

发布时间: 2024-12-23 01:33:32 阅读量: 9 订阅数: 12

PRBS 波形发生器:从 PRBS 种子生成 PRBS 波形-matlab开发

# 摘要

信号完整性测试是确保高速电子系统可靠运行的关键环节,涉及理论与实践的多个方面。本文首先介绍了信号完整性测试的基础知识,然后深入探讨了伪随机二进制序列(PRBS)在测试中的应用及其在高速电路中的独特作用。文中还比较了PRBS与其他测试方法,并详细阐述了信号完整性测试的理论基础,包括核心概念和测试技术的分类。通过案例分析,本文进一步揭示了在实际电路设计中遇到的信号完整性问题及解决方案,并展望了信号完整性测试的未来趋势与挑战。最后,本文提供了实战技巧与建议,帮助工程师避免常见的测试误区,提高测试效果。

# 关键字

信号完整性测试;PRBS;高速电路;测试技术;电路设计;实战技巧

参考资源链接:[PRBS伪随机码生成原理详解及其应用](https://wenku.csdn.net/doc/64892292619bb054bf5d5634?spm=1055.2635.3001.10343)

# 1. 信号完整性测试基础

信号完整性测试是高速电路设计领域中至关重要的一环。它旨在确保信号在传输过程中保持其原始的时序与形态,不受到诸如反射、串扰、电磁干扰(EMI)等因素的影响。信号完整性不仅直接影响电路的性能和可靠性,还是产品能否成功商业化的关键因素之一。在本章节中,我们将介绍信号完整性测试的基本概念、重要性以及初步的测试方法。

## 1.1 信号完整性的概念

信号完整性(Signal Integrity, SI)关注的是信号在传输路径上是否保持其特性不变。这包括信号的时序、电压水平和信号质量。在高速电路中,由于信号变化的速度很快,信号完整性问题变得尤为突出。任何微小的不连续性都可能导致信号失真,影响电路性能。

## 1.2 信号完整性的重要性

对于高速数字电路,如千兆以太网、光纤通信等,信号完整性直接影响设备的运行速率和稳定性。一个良好的信号完整性保证了设备能够在规定的频率范围内可靠地工作,避免了数据丢失或错误的风险。因此,对信号完整性的研究和测试是电子工程师必须面对的一个基本课题。

## 1.3 信号完整性测试方法概述

信号完整性测试方法主要包括时域测试和频域测试。时域测试关注信号波形随时间的变化,常用于测量信号上升时间、下降时间、过冲和下冲等参数。频域测试则关注信号频谱的分布,适用于评估信号谐波成分和滤波器性能。通过这些测试方法,工程师能够诊断并解决信号完整性问题,确保电路设计的成功。

# 2. PRBS在信号完整性中的应用

### 2.1 PRBS信号的特点与生成

#### 2.1.1 PRBS序列的基本理论

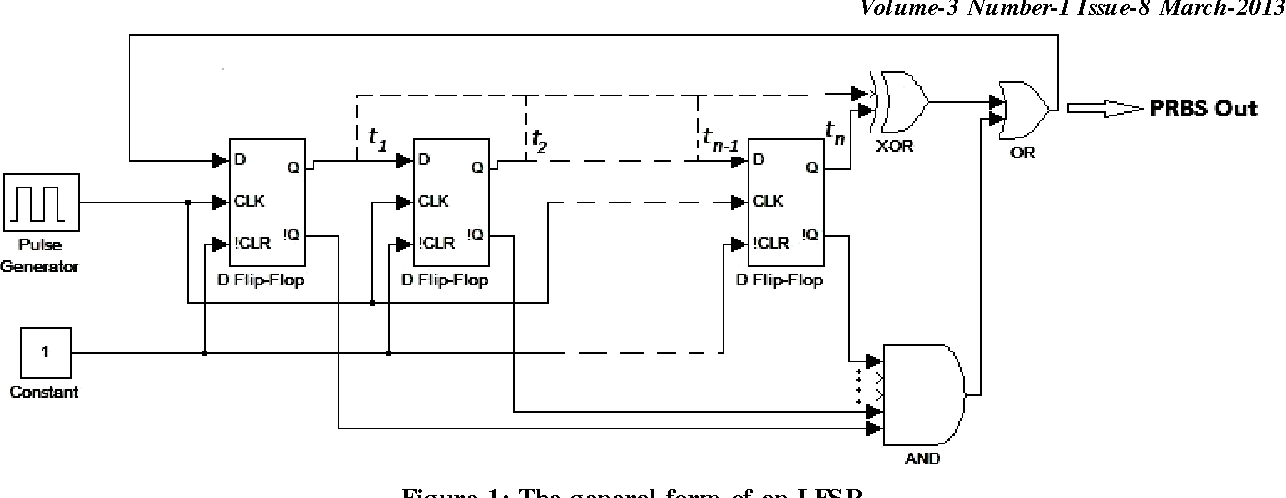

伪随机二进制序列(Pseudo-Random Binary Sequence,PRBS)是一种具有随机统计特性的周期性序列,广泛应用于信号完整性测试。PRBS序列的生成依赖于线性反馈移位寄存器(Linear Feedback Shift Register, LFSR),它能够产生一个具有伪随机特性的数字序列。

LFSR由几个触发器(通常为D型触发器)组成,以及一些反馈逻辑来实现序列的生成。其主要特点包括:

- **周期性**:PRBS序列的长度是固定的,一个完整的周期之后会重复。

- **平衡性**:序列中0和1的数量大致相同。

- **自相关性**:序列与其自身的不同位置的移位版本具有低相关性。

- **良好的随机性**:序列在统计意义上接近真正的随机序列。

在设计PRBS生成器时,序列的最大长度取决于LFSR中的位数和特定的反馈逻辑。

#### 2.1.2 PRBS生成器的设计与实现

设计PRBS生成器的一个关键是选择合适的反馈位置。一般情况下,当LFSR中的触发器数目为n时,可生成的最大周期为\(2^n - 1\)的序列。反馈位的选择应保证序列的最大周期性。

一个简单的PRBS生成器实现可以通过以下步骤:

1. 确定LFSR的位数n,并选择合适的反馈点。

2. 初始化LFSR的寄存器状态。

3. 在每个时钟周期,将最高位的输出(通常通过异或门和反馈点结合产生)移入LFSR的最低位,同时其它各位右移一位。

4. 经过\(2^n - 1\)个周期,PRBS序列会完成一个循环。

下面是一个使用Verilog实现3位LFSR生成器的例子代码:

```verilog

module prbs3_generator(

input clk, // 时钟信号

input reset, // 复位信号

output reg out // PRBS序列输出

);

reg [2:0] lfsr; // 3位LFSR

always @(posedge clk or posedge reset) begin

if (reset) begin

lfsr <= 3'b101; // 初始化为101,是一个常用的初始值

end else begin

// 移位操作和反馈

lfsr <= {lfsr[1:0], lfsr[2] ^ lfsr[0]};

end

end

// 将MSB作为输出

always @(lfsr) begin

out = lfsr[2];

end

endmodule

```

在这段代码中,我们定义了一个模块`prbs3_generator`,它有三个主要的逻辑部分:时钟和复位信号处理、LFSR寄存器状态的移位和反馈操作、以及输出逻辑。

### 2.2 PRBS在高速电路中的作用

#### 2.2.1 高速电路信号完整性概述

高速电路设计中信号完整性(Signal Integrity, SI)问题变得尤其重要,因为信号的传输速度提高,对信号的质量要求也随之提高。信号完整性问题主要体现在反射、串扰、抖动等方面。为了在高速电路中有效地评估信号质量,需要使用有效的测试信号。

PRBS作为一种有效的测试信号,在高速电路设计和测试中发挥着以下作用:

- **生成复杂的测试波形**:PRBS序列能够模拟实际数据流,生成包含丰富频率成分的测试信号。

- **提供均匀的统计特性**:PRBS序列的伪随机特性保证了测试信号在整个周期内的统计特性基本一致。

#### 2.2.2 PRBS在信号完整性测试中的应用案例

在信号完整性测试中,PRBS可以用于模拟数据传输的实际情况。例如,在测试PCB板级互连时,可以使用PRBS序列作为测试信号源,通过探头捕获数据流在传输过程中的变化,分析信号在时间域和频域上的表现。

例如,如果是在测试一个高速串行通信链路(如HDMI、USB3.0等),PRBS可以用来作为发送端的数据源,接收端则可以捕获接收到的信号并进行错误检测和信号质量评估。

一个简单的测试案例流程如下:

1. 将PRBS信号作为输入源,连接到高速电路的发送端。

2. 配置接收端设备捕获PRBS信号,并设置合适的门限值和采样率。

3. 使用误码率测试仪(BERT)检查接收信号与原始PRBS序列的比较结果,记录误码数。

4. 对捕获

0

0