【低功耗设计达人】:静态MOS门电路低功耗设计技巧,打造环保高效电路

发布时间: 2024-11-13 06:26:15 阅读量: 29 订阅数: 34

超低功耗电子电路系统设计原则

# 1. 静态MOS门电路的基本原理

静态MOS门电路是数字电路设计中的基础,理解其基本原理对于设计高性能、低功耗的集成电路至关重要。本章旨在介绍静态MOS门电路的工作方式,以及它们如何通过N沟道MOSFET(NMOS)和P沟道MOSFET(PMOS)的组合来实现逻辑功能。

## 1.1 MOSFET的基本概念

MOSFET,全称为金属-氧化物-半导体场效应晶体管,是构成MOS门电路的基本元件。它的主要组成部分包括源极(Source)、漏极(Drain)、栅极(Gate)和衬底(Substrate)。MOSFET工作时,电压施加在栅极上,控制源极和漏极之间的导电通道,从而实现开关作用。

## 1.2 逻辑门的构建

静态MOS门电路是使用多个MOSFET按照特定的逻辑功能连接而成。例如,一个简单的非门(NOT gate)可以用一个PMOS和一个NMOS晶体管串联实现,当输入为低电平时,NMOS截止,PMOS导通,输出为高电平;反之亦然。在实际应用中,复杂的逻辑功能需要更多的晶体管以特定的配置来构建。

理解MOSFET的操作原理和如何构建基本逻辑门是深入掌握静态MOS门电路设计的前提。下面章节将进一步探讨如何设计出高性能和低功耗的静态MOS门电路。

# 2. 静态MOS门电路设计的基本技巧

### 2.1 静态MOS门电路的功耗分析

#### 2.1.1 功耗的来源和类型

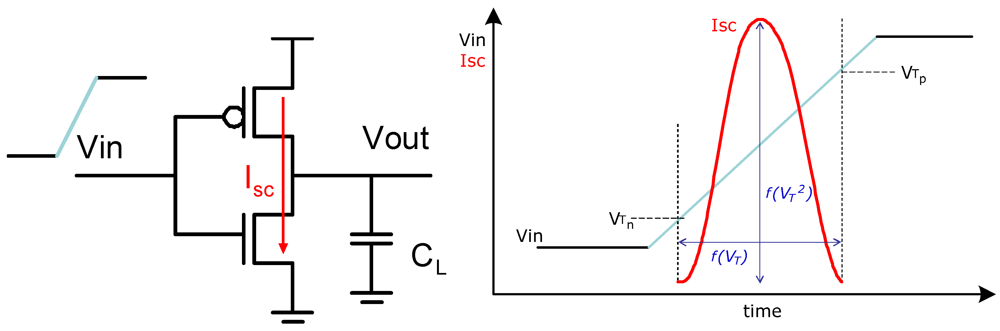

在设计静态MOS门电路时,了解功耗的来源和类型至关重要。电路的功耗主要可以分为静态功耗和动态功耗两大部分。

- **静态功耗(Leakage Power)**:主要来源于晶体管在关闭状态下的漏电流。由于MOS晶体管的物理特性,即使在其栅极电压为零时,仍然会有少量电流从漏极流向源极,这导致了静态功耗的存在。随着晶体管尺寸的减小,这一效应变得尤为显著。

- **动态功耗(Dynamic Power)**:在电路中,当晶体管切换状态时,电流会在电源和地之间流动,从而产生功耗。动态功耗与晶体管切换的频率成正比,以及与负载电容、电源电压的平方成正比,可用公式 P = αCV^2f 描述,其中α是活动因子,C是负载电容,V是电源电压,f是切换频率。

功耗分析是优化设计的一个重要环节,特别是在需要实现低功耗设计时,能够准确识别和评估功耗来源是至关重要的。

#### 2.1.2 影响功耗的因素

影响静态MOS门电路功耗的因素众多,以下为几个主要因素:

- **电源电压(VDD)**:根据动态功耗公式 P = αCV^2f,我们可以看到电源电压的平方与功耗直接相关,因此,降低电源电压是减少功耗的有效手段之一。

- **晶体管尺寸**:晶体管的尺寸(特别是宽度W)影响其开关速度和漏电流,较大的晶体管会有较高的开关功耗和较低的漏电流,反之亦然。

- **工艺节点**:随着半导体制造技术的进步,晶体管尺寸不断缩小,导致更高的漏电流和更复杂的工艺控制,从而影响整体功耗。

- **工作频率**:电路的工作频率与动态功耗密切相关。频率越高,晶体管切换次数越多,相应的功耗也就越大。

- **开关活动因子(α)**:它表示晶体管在特定时间内进行切换活动的频率,活动因子越高,动态功耗越大。

- **负载电容(C)**:负载电容的大小直接决定于电路中的寄生电容以及由晶体管连接的电容总和。负载电容越大,充电和放电所需能量就越多,从而造成更大的动态功耗。

接下来,我们将深入探讨如何通过电路优化来减少这些因素对功耗的影响。

# 3. 静态MOS门电路低功耗设计的实践应用

在本章节中,我们将深入探讨静态MOS门电路在实践中的低功耗设计。这一领域的重要性日益突显,随着电子设备越来越小型化,对电源效率的要求也日益严苛。我们将首先分析一个低功耗设计的电路实例,然后评估设计的效果,并讨论如何改进。

## 3.1 低功耗设计的电路实例分析

### 3.1.1 电路设计前的准备工作

在着手设计一个低功耗的静态MOS门电路前,必须先做好充分的准备工作。这包括理解应用需求、明确性能指标、选定合适的工艺节点以及选择合适的电路架构。以下是具体步骤:

1. **理解应用需求**:明确电路在目标应用中的功能、性能要求(如速度、输入输出电平、容错能力等),以及环境条件(如温度范围、电源电压等)。

2. **性能指标的定义**:根据应用需求,设定电路的功耗、速度、噪声容限、鲁棒性等关键性能指标。

3. **工艺选择**:选择合适的半导体工艺节点,考虑其在功耗、速度、成本等方面的优劣,以实现性能和成本的最佳平衡。

4. **电路架构的确定**:基于性能指标和工艺特性,决定采用的电路架构(如CMOS、Pseudo-NMOS等),并考虑如何在设计中实现低功耗。

### 3.1.2 电路设计的过程和结果

设计过程从概念出发,经过电路图设计、仿真验证、版图设计,最终完成原型测试。以下是详细步骤:

1. **电路图设计**:根据前面的准备工作,绘制电路图,确定晶体管的尺寸、连接方式等。

2. **仿真验证**:使用仿真软件(如SPICE)对电路进行功能和性能仿真,重点验证功耗参数。

3. **版图设计**:基于仿真结果,设计电路的版图,再次进行版图层面的仿真,考虑寄生参数和实际布局的影响。

4. **原型测试**:将版图信息送往制造厂商,并在制造完成后进行原型测试,通过实际测量来验证设计的低功耗性能是否达标。

## 3.2 低功耗设计的效果评估

### 3.2.1 功耗的测量和分析

对完成的电路原型进行功耗测量是评估低功耗设计效果的关键步骤。测量通常在特定的测试平台上进行,模拟实际应用场景中的工作条件。主要的测量和分析步骤如下:

1. **测试平台的搭建**:建立包含电源、负载、控制单元和测量设备的测试平台。

2. **工作模式的模拟**:根据实际应用,模拟电路在不同工作模式(如空闲模式、待机模式、动态操作模式)下的功耗。

3. **数据的采集与分析**:实时采集电路的电流和电压数据,并通过计算得到功耗信息。分析测量数据,确定电路在各模式下的功耗水平。

### 3.2.2 设计效果的评估和改进

设计效果的评估不仅需要考虑功耗指标,还应该关注其他性能指标是否满足设计要求。以下为评估和改进的步骤:

1. **性能指标对比**:将测量得到的性能指标与设计前的目标指标进行

0

0