【集成应用高手】:静态MOS门电路集成挑战与策略,突破集成电路设计瓶颈

发布时间: 2024-11-13 06:04:30 阅读量: 18 订阅数: 12

# 1. 静态MOS门电路集成技术概述

在现代电子工业中,静态MOS门电路是构建集成电路的核心组件。本章节将对静态MOS门电路的集成技术进行概述,为读者提供一个全面的理解框架。我们将从MOS门电路的基础概念出发,解析其在集成电路中的重要性,并简要介绍MOS技术发展对整个半导体行业的影响。

MOS(金属-氧化物-半导体)技术是一种广泛应用于集成电路制造中的技术,其基础构成是MOS晶体管。MOS晶体管因其独特的物理特性和电气性能,在实现微型化、低功耗以及高集成度方面有着不可替代的优势。MOS门电路,作为组合逻辑电路的基本单元,通过不同MOS晶体管的组合实现基本的逻辑功能,如与门(AND)、或门(OR)、非门(NOT)等。

随着半导体工艺的不断进步,MOS门电路的集成度越来越高,这直接推动了电子设备的小型化和性能的提升。然而,高集成度也带来了诸如信号传播延迟、功耗问题、热管理和制造成本等一系列挑战。下一章节将深入探讨MOS门电路的设计基础,并对这些挑战进行详细分析。

# 2. 静态MOS门电路集成设计基础

### 2.1 MOS门电路的工作原理

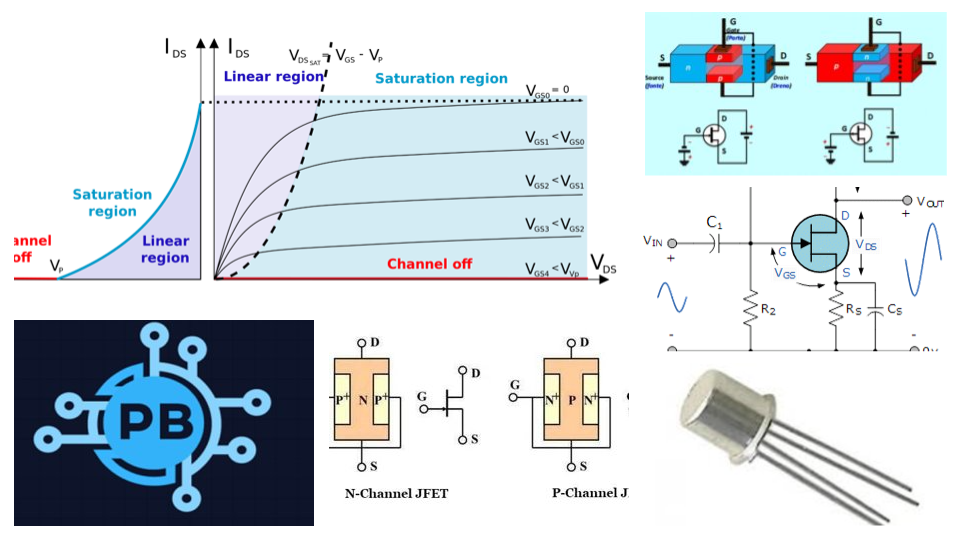

#### 2.1.1 MOS晶体管的基本构造与特性

MOS晶体管,全称为金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET),是现代集成电路的基础单元。MOSFET具有三种基本类型:N型耗尽型(Depletion-mode N-type)、N型增强型(Enhancement-mode N-type)、P型增强型(Enhancement-mode P-type)和P型耗尽型(Depletion-mode P-type)。

每种MOSFET的基本构造包含三个主要部分:源极(Source)、漏极(Drain)和栅极(Gate)。栅极被绝缘体(通常是二氧化硅SiO2)与半导体(硅Si)分隔,源极和漏极位于半导体的两侧。源极与漏极之间的通道是由半导体材料构成,其导电性能由栅极电压控制。

- **N型MOSFET**:当栅极电压高于一个阈值时,使得电子从源极流入漏极,形成电流。若栅极电压低于阈值,通道中缺少自由电子,电流为零。

- **P型MOSFET**:与N型相反,当栅极电压低于一个阈值时,导电通道形成,空穴从源极流动到漏极。

MOSFET特性包括导通电阻、阈值电压、跨导、输出电阻等。其中,导通电阻是指当晶体管处于导通状态时,源极和漏极之间的电阻。阈值电压决定了晶体管开启的电压条件。跨导反映了栅极电压变化时对漏极电流变化的影响。输出电阻则是指漏极电流变化时,漏极电压的变化幅度。

#### 2.1.2 逻辑门电路的工作机制

在数字电路中,逻辑门是执行基本逻辑功能的电路组件。静态MOS门电路利用MOSFET的开关特性来实现逻辑功能。如NAND门和NOR门就是MOS门电路中的基本逻辑单元。

逻辑门电路的核心在于使用MOSFET的导通与截止状态来实现逻辑真值表中的逻辑“1”和逻辑“0”。例如,NAND门的输出在所有输入为“1”时为“0”,其他情况为“1”:

```

输入A | 输入B | 输出

0 | 0 | 1

0 | 1 | 1

1 | 0 | 1

1 | 1 | 0

```

实现NAND门时,可以使用两个并联的N型MOSFET,一个P型MOSFET将它们串联。当输入A和B都为“1”时,N型MOSFET均导通,P型MOSFET截止,输出为低电平。若输入中任何一个为“0”,则至少有一个N型MOSFET截止,P型MOSFET导通,输出为高电平。

NOR门逻辑则相反,当输入中有任意一个为“1”,输出即为“0”,只有当所有输入为“0”时,输出才为“1”。NOR门可以使用两个串联的N型MOSFET,由一个P型MOSFET并联组成实现。

### 2.2 静态MOS门电路的电路分析

#### 2.2.1 电压传输特性曲线分析

电压传输特性(Voltage Transfer Characteristic, VTC)曲线是描述在不同输入电压下,输出电压如何变化的图表。它表示了MOS门电路从高输出状态到低输出状态转换的临界点以及过渡区域的特性。

典型的VTC曲线大致呈现为“S”型。关键区域包括:

- **阈值电压区域**:输出电压从高电平向低电平过渡的区域,通常为输入电压接近阈值电压时。在此区域内,MOSFET逐渐从截止状态变为导通状态。

- **转换区域**:输入电压超过阈值电压后,输出电压开始显著变化。

- **饱和区域**:输入电压继续增加,输出电压将趋向一个饱和值,此时MOSFET完全导通。

理想情况下,VTC曲线是陡峭的,意味着门电路的高低电平切换点明确。但在实际中,由于制造过程的变异和温度的影响,曲线可能会变得平缓,影响电路的开关速度和噪声容限。

```mermaid

graph TD;

A[高电平] -->|接近阈值| B[过渡区域]

B -->|继续增加| C[饱和区域]

C --> D[低电平]

```

#### 2.2.2 电源与负载效应

静态MOS门电路在电源电压和负载变化时会表现出不同的性能。电源电压主要影响电路的工作速度和功耗,而负载效应通常涉及到输出驱动能力和信号完整性问题。

- **电源电压**:电源电压的增加可以提高MOSFET的速度,因为驱动电流会增加。但同时,增加的电源电压也会导致功耗的增大,尤其是在高速开关操作时。

- **负载电容**:负载电容值的大小直接影响了门电路的开关速度。负载电容大时,为了充放电至高/低电平需要更长的时间,延迟增加,开关速度减慢。

负载电容包括互连电容、门电容和负载电容等多种因素。高负载电容将导致门电路的充电和放电时间延长,降低电路性能。因此,电路设计者需根据门电路的性能要求选择适当的MOSFET尺寸,以平衡延迟和功耗之间的关系。

### 2.3 静态MOS门电路设计准则

#### 2.3.1 延迟最小化原则

在设计静态MOS门电路时,延迟最小化是重要目标之一。延迟主要由门电路的传输延迟和充放电延迟两部分组成。为了最小化延迟,设计者必须关注以下要素:

- **晶体管尺寸**:选择合适的MOSFET尺寸来平衡驱动电流和电路延迟。大尺寸MOSFET能够提供更大的电流,有助于减少充放电时间,但同时也会增加电容负载。

- **晶体管配置**:通过合适的晶体管连接配置,可以优化电路的开关速度。例如,使用级联方式连接可以减少单一晶体管的负载电容,从而减少延迟。

- **电源电压**:优化工作电压可有效降低延迟,但同时要注意不超过晶体管的击穿电压和热设计功率。

这些设计原则需要结合具体的电路仿真和优化工具进行实验验证,以达到最佳性能。

```code

// 伪代码示例,展示如何通过仿真工具优化电路尺寸

// 在此处假设有一个电路仿真工具的接口函数

function optimizeGateDelay(inputCircuitDesign) {

// 输入当前电路设计参数

// 执行仿真并分析结果

// 根据仿真结果调整MOSFET尺寸和配置

// 返回优化后的电路设计参数

}

```

#### 2.3.2 功耗与噪声的考量

功耗是静态MOS门电路设计中的另一项关键指标。由于集成电路中的门电路数量庞大,即使单个门电路的功耗较小,总体功耗也可能非常显著。

- **动态功耗**:在开关操作中,电路的电容充放电需要能量,导致动态功耗。动态功耗与电源电压的平方、工作频率以及负载电容成正比。

- **静态功

0

0