W25Q64数据缓存与持久化设计模式:实践高效存储方案

发布时间: 2025-01-05 19:26:53 阅读量: 7 订阅数: 16

内墙装修涂料行业发展趋势:预计2030年年复合增长率(CAGR)为5.6%(2024-2030)

# 摘要

本文探讨了W25Q64 Flash存储器的基础知识、数据缓存技术的原理、数据持久化策略研究以及缓存与持久化在W25Q64中的设计模式。文章首先介绍了Flash存储器的基本概念和数据缓存技术的优势及其策略。接着,详细分析了数据持久化的需求、技术选择和数据恢复备份策略。第四章着重于结合缓存与持久化的设计模式、性能优化与测试。最后,通过W25Q64的实际应用案例分析,展现了理论知识与实践应用的结合,并对应用效果进行了评估和总结。本文旨在为存储器设计和数据管理提供全面的参考和指导。

# 关键字

Flash存储器;数据缓存;数据持久化;设计模式;性能优化;W25Q64

参考资源链接:[W25Q64中文手册:全面解析W25X系列SPI FLASH](https://wenku.csdn.net/doc/3ucayb8q9x?spm=1055.2635.3001.10343)

# 1. W25Q64 Flash存储器基础

## 1.1 W25Q64概述

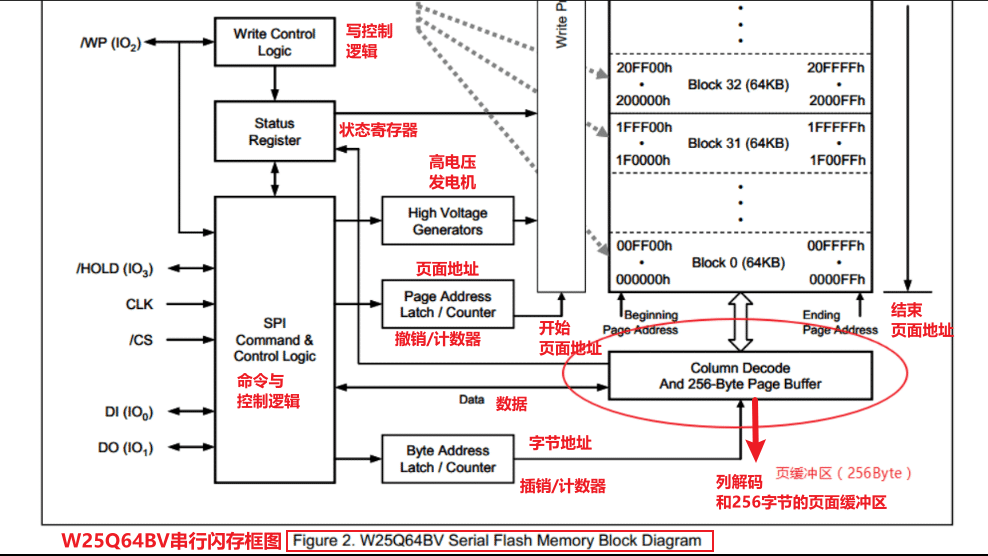

W25Q64是一种广泛使用的64M位串行Flash存储器,以其高可靠性和高效性在嵌入式系统和各种电子设备中扮演着重要角色。该存储器支持多种高性能的操作模式,如标准SPI、双输出SPI和四输出SPI模式,能够满足多种数据传输需求。

## 1.2 W25Q64的特点

W25Q64具备以下几个显著特点:

- 容量大:提供64M位(8M字节)的存储空间。

- 速度快:高速读写性能支持快速的数据处理。

- 低功耗:对功耗要求严格的设备中也能保持较低能耗。

## 1.3 W25Q64的应用领域

由于W25Q64提供了高可靠性和灵活的操作模式,它在多个领域有着广泛的应用,包括但不限于:

- 智能家居设备

- 工业控制系统

- 医疗仪器

- 汽车电子

W25Q64 Flash存储器为各种应用提供了稳定的存储解决方案,是现代嵌入式系统不可或缺的一部分。在后续章节中,我们将深入探讨其在缓存与持久化策略中的具体应用。

# 2. 数据缓存技术原理

## 2.1 缓存的作用与优势

### 2.1.1 缓存的定义和功能

缓存是一种存储技术,它利用快速访问的局部存储来保存频繁使用的数据,以减少访问时间较长的主存储器的次数。它作为一种临时存储区域,其主要功能是在处理器与主内存之间建立一个快速数据交换的通道。

缓存的优势体现在以下几个方面:

- **降低延迟(Latency)**:缓存能够快速响应处理器的数据请求,减少了等待时间,提高系统的响应速度。

- **提高吞吐量(Throughput)**:通过缓存预取和批量操作,可以提高大量数据处理的效率。

- **减少主存访问频率**:由于缓存的数据都是从主存中复制过来的,因而减少了直接访问主存的频率,从而减轻了主存的工作负担。

### 2.1.2 缓存策略的分类和应用

缓存策略可以分为以下几种:

- **写穿透(Write Through)**:数据被同时写入缓存和主存中。这种策略保证了数据的一致性,但是写操作的性能较低。

- **写回(Write Back)**:数据首先写入缓存,当数据被替换出缓存时,再写入主存。这种方式提高了写入速度,但增加了复杂性和潜在的数据一致性风险。

- **写失效(Write Invalidate)**:当缓存中的数据被修改时,该缓存行在其他缓存中的副本将被标记为无效,确保所有读取操作都能从主存或其他缓存中读取最新的数据。

- **写更新(Write Update)**:当缓存数据被修改时,其他缓存中相同数据的副本也会被更新。这可以减少未来的缓存未命中(Cache Miss),但增加了额外的网络流量。

在实际应用中,根据不同的应用场景和性能要求,选择最合适的缓存策略,可以优化系统的整体性能。

## 2.2 数据缓存的实现机制

### 2.2.1 内存与存储的缓存层次

现代计算机系统中,缓存通常被分为不同的层次,每一层的缓存有其特定的大小、速度和访问延迟。典型的内存层次结构包括:

- **一级缓存(L1 Cache)**:紧挨着CPU的核心,提供极低延迟的访问。但其容量相对较小。

- **二级缓存(L2 Cache)**:作为一级缓存的补充,拥有更大的容量,访问速度介于L1与主存之间。

- **三级缓存(L3 Cache)**:进一步扩大缓存容量,为多个CPU核心服务。

- **主存(Main Memory)**:较大的容量,但访问速度相对缓存来说较慢。

此外,近年来,非易失性内存(如Intel的Optane技术)作为新的存储层次出现在体系结构中,它在性能和容量之间提供了新的平衡点。

### 2.2.2 缓存映射和替换算法

缓存映射是指将主存地址映射到缓存中的过程,常见的映射方式包括:

- **直接映射(Direct Mapped)**:每个主存块只能映射到一个特定的缓存行。

- **全相联映射(Fully Associative)**:主存块可以映射到任意一个缓存行。

- **组相联映射(Set Associative)**:结合了直接映射和全相联映射的特点,主存块可以映射到一组特定的缓存行。

替换算法决定在缓存满时,哪个缓存行将被新的数据替换出去。典型的算法包括:

- **最近最少使用(LRU)**:替换最长时间未被访问的数据。

- **随机替换**:随机选择一个缓存行进行替换。

- **先进先出(FIFO)**:根据数据在缓存中的驻留时间进行替换。

每种映射和替换策略都有其适用场景,开发者需要根据具体的应用需求选择合适的策略。

```mermaid

graph LR

A[主存块] -->|映射关系| B[缓存行]

B -->|直接映射| C[直接映射缓存]

B -->|全相联映射| D[全相联映射缓存]

B -->|组相联映射| E[组相联映射缓存]

```

在组相联映射中,缓存被划分为多个组,每个组内可以有多个缓存行。这种策略平衡了直接映射的简单性和全相联映射的灵活性。

## 2.3 缓存一致性问题分析

### 2.3.1 缓存一致性问题的成因

缓存一致性问题主要由多级缓存结构中的数据副本引起。当一个数据被多个缓存所持有时,数据的更新将导致缓存之间的状态不一致。在多处理器系统中,这种问题尤为突出,因为多个处理器可能同时读写同一个数据,但缓存中的数据副本并没有实时同步。

为了维持缓存一致性,必须实施一定的同步协议和算法,如MESI(修改、独占、共享、无效)协议,它是一种广泛应用的缓存一致性协议。

### 2.3.2 解决方案及效果评估

解决缓存一致性问题的常见方案有:

- **写直达(Write Through)**:更新数据时,同时写入缓存和主存,保证所有副本的一致性,但会带来较高的写入延迟。

- **监听总线(Snooping)**:多处理器系统中的缓存监听总线上的事务,及时更新自己的缓存状态。

- **目录(Dir

0

0