硬件模拟与现实世界:Logsim加减法应用案例深度分析

发布时间: 2024-12-14 09:23:33 阅读量: 6 订阅数: 10

logsim8位可控加减法电路设计.txt

参考资源链接:[Logisim教程:8位可控加减法电路设计详解](https://wenku.csdn.net/doc/446ctioi80?spm=1055.2635.3001.10343)

# 1. Logsim简介与加减法模拟基础

## 1.1 Logsim平台概述

Logsim 是一款专注于逻辑电路模拟和教育目的的软件,它提供了一个直观的环境来设计、测试和分析数字电路。Logsim 以其易用性和强大的功能在学术界和工业界获得了广泛的应用。对于初学者,Logsim 提供了一个理解和实践数字逻辑设计的平台。对于资深工程师和研究人员,Logsim 则是一个可以验证复杂数字系统和算法的工具。

## 1.2 加减法模拟的重要性

在数字电路设计中,加法和减法是最基本的操作,它们构成了更复杂数学运算的基础。通过模拟加减法,可以建立起对数字电路工作原理的基本理解。此外,对加减法的模拟还是学习更高级概念,如算术逻辑单元(ALU)设计、二进制数的算术运算等的基石。因此,本章将重点介绍如何使用Logsim来模拟基础的加减法操作,并为进一步学习更复杂的电路设计打下坚实基础。

# 2. Logsim中加减法的理论基础

## 2.1 数字逻辑的基础知识

### 2.1.1 二进制加减法原理

在数字电路设计中,二进制加减法是基础中的基础,几乎所有的运算都是在这一层面上展开的。二进制加法遵循与十进制相似的法则,只是进位的条件变成了2而不是10。具体来说:

- 0 + 0 = 0

- 0 + 1 = 1

- 1 + 0 = 1

- 1 + 1 = 0 (进位 1)

为了理解加法器是如何构建的,我们需要知道如何将多个位相加,包括进位的情况。减法则更为复杂一些,因为它涉及到借位的概念。同样,二进制减法的基本法则为:

- 0 - 0 = 0

- 1 - 0 = 1

- 1 - 1 = 0

- 0 - 1 = 1 (借位 1)

借位处理时,我们从相邻的高位借一,这个“一”在二进制中实际上是以 2 的形式存在,因为每个位的权值是 2 的幂。

### 2.1.2 逻辑门与布尔代数

数字逻辑电路由基本的逻辑门组成,比如AND门、OR门、NOT门等。这些基本的门电路可以通过布尔代数的法则进行组合,以实现更复杂的逻辑功能。例如:

- AND 门表示逻辑乘(AND),只有当所有输入都为1时输出才为1。

- OR 门表示逻辑加(OR),只要有任何一个输入为1,输出就为1。

- NOT 门则是对输入信号进行逻辑非操作。

布尔代数的基础运算法则包括交换律、结合律、分配律、德摩根定律等,这些都是进行逻辑设计时不可或缺的工具。

## 2.2 加法器的构建与原理

### 2.2.1 半加器和全加器的设计

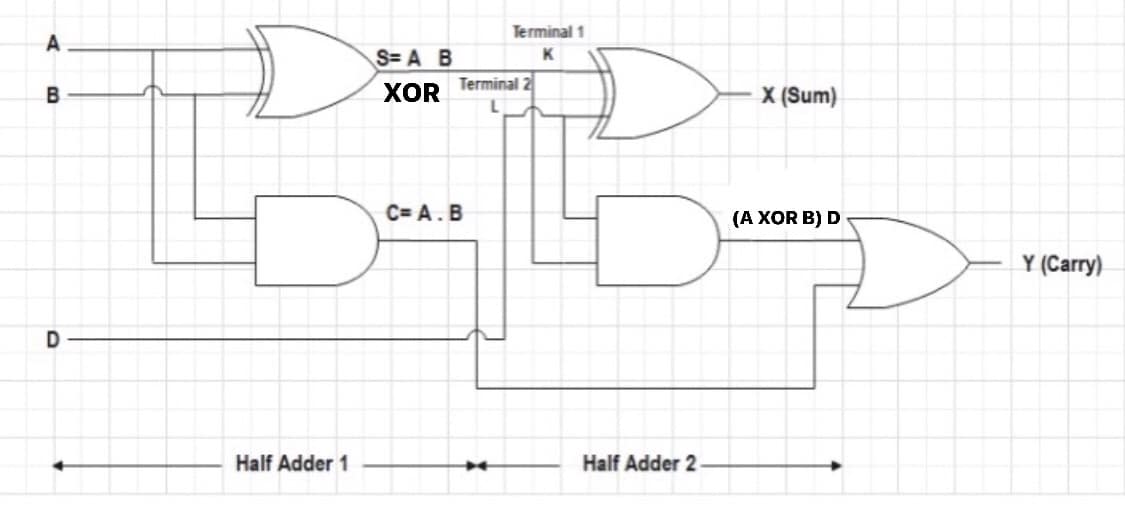

在数字电路中,最基本单元之一就是加法器。加法器又分为半加器和全加器。半加器仅考虑两个输入的加法情况,而全加器可以处理三个输入(两个加数加上前一位的进位)。

- 半加器的设计通常包括一个异或门(XOR)来实现求和(S),以及一个与门(AND)来实现进位(C)。

- 全加器除了包含半加器的逻辑,还需要加入一个额外的输入端来处理进位输入。这通常通过两个AND门、一个OR门和一个半加器组合实现。

### 2.2.2 并行加法器的原理与实现

在实际应用中,通常需要同时处理多个数据位的加法,这就需要用到并行加法器。并行加法器由多个全加器级联而成,以实现多比特的加法。

关键在于正确地处理进位。在并行加法器中,每个全加器的进位输出都会连接到下一个全加器的进位输入。这种级联的设计是实现并行加法的基础。

## 2.3 减法器的设计与优化

### 2.3.1 补码的概念和应用

减法在数字电路中通常是通过加法来实现的,这就要用到补码的概念。补码可以将减法操作转换为加法操作,简化了电路设计。补码的计算是基于二进制数的反码(每个位取反)再加一。

例如,要计算 5 - 3,首先找到3的补码(即 -3),然后将其与5相加:

```

5 = 0101 (二进制)

3的补码 = 1101 (反码是 1010, 加 1 得到补码)

相加得:

0101

+ 1101

0010 (结果是 2)

```

### 2.3.2 减法器的构建方法和注意事项

构建减法器时,我们通常会实现一个全减器(Full Subtractor),它包含三个输入:被减数、减数和借位输入。全减器的输出包括差和借位输出。

设计减法器时需注意的几个关键点:

- 借位输入的处理。

- 减法器在级联时的借位传递逻辑。

- 减法器的优化,例如,减少逻辑门的数量以提高电路的效率和速度。

通过使用补码和全减器,我们可以构建高效且功能强大的减法器电路。在下一章节,我们将通过 Logsim 进行这些理论知识的实践应用。

# 3. Logsim加减法模拟实践

## 3.1 Logsim环境设置与工具介绍

### 3.1.1 Logsim界面概览

Logsim是一个旨在帮助学生和专业人士更好地理解数字逻辑及其设计过程的模拟软件。在开始构建加减法模拟之前,了解Logsim的用户界面至关重要。用户界面是集成的,设计简洁,但功能强大。在主界面中,用户可以看到工具栏、项目浏览器、设计区和属性窗口等几个主要部分。

- **工具栏**:提供创建新项目、打开项目、保存工作、撤销和重做等常规功能。

- **项目浏览器**:列出项目中所有的组件,方便用户管理和导航。

- **设计区**:这是构建和编辑数字电路的主要区域,直观地显示了电路的逻辑结构。

- **属性窗口**:显示选中组件的详细信息,允许用户对组件进行精确配置。

Logsim的界面设计使得新手用户可以迅速上手,同时对于有经验的用户来说,也提供了足够的灵活性和控制度。

### 3.1.2 必要组件的添加与配置

在Logsim中进行加减法模拟之前,需要添加必要的组件并进行适当的配置。下面的步骤将指导你完成这一过程:

1. 打开Logsim,创建一个新的项目。

2. 通过工具栏中的"组件库"按钮打开组件库。

3. 从组件

0

0