【解析Logsim控制逻辑】:设计有效逻辑的专家指南

发布时间: 2024-12-14 08:25:59 阅读量: 5 订阅数: 10

数字逻辑---交通灯系统设计(HUST) 头歌

参考资源链接:[Logisim教程:8位可控加减法电路设计详解](https://wenku.csdn.net/doc/446ctioi80?spm=1055.2635.3001.10343)

# 1. Logsim控制逻辑基础

在数字电路设计和逻辑分析领域中,Logsim控制逻辑扮演着至关重要的角色。本章旨在为读者搭建一个坚实的基础,深入理解Logsim控制逻辑的基本概念、构建原理以及其在各种应用场景中的运用。我们将从最基础的元素开始,介绍如何运用Logsim来设计和模拟数字逻辑系统,使初学者能够快速上手,同时为有经验的读者提供更深层次的分析和见解。

## 1.1 Logsim的基本功能介绍

Logsim是一个功能强大的逻辑仿真软件,它提供了一个直观的图形界面,让用户能够通过拖放各种逻辑门来设计电路。它支持时序和组合逻辑电路,同时也允许用户进行电路的模拟、调试和优化。通过这一章节的学习,读者将掌握如何使用Logsim来创建简单的逻辑电路,并进行基本的逻辑运算。

## 1.2 设计流程入门

设计一个逻辑电路,首先需要明确电路的功能需求和逻辑表达式。接下来,通过选择合适的逻辑门(如AND、OR、NOT门等),将逻辑表达式转化为逻辑电路图。Logsim简化了这一过程,用户可以在图形界面中直观地搭建电路,而无需编写复杂的代码。本章将引导读者通过实例操作,完成从逻辑表达式到电路图的转化,并介绍如何使用Logsim进行电路的模拟测试。

在后续章节中,我们将深入探讨Logsim在控制逻辑设计中的高级应用、实践案例分析、以及面临的挑战和优化技巧。通过逐步深入的学习,读者将能够熟练运用Logsim解决实际问题,并提升设计的复杂度和性能。

# 2. Logsim控制逻辑理论分析

## 2.1 逻辑设计的基本原理

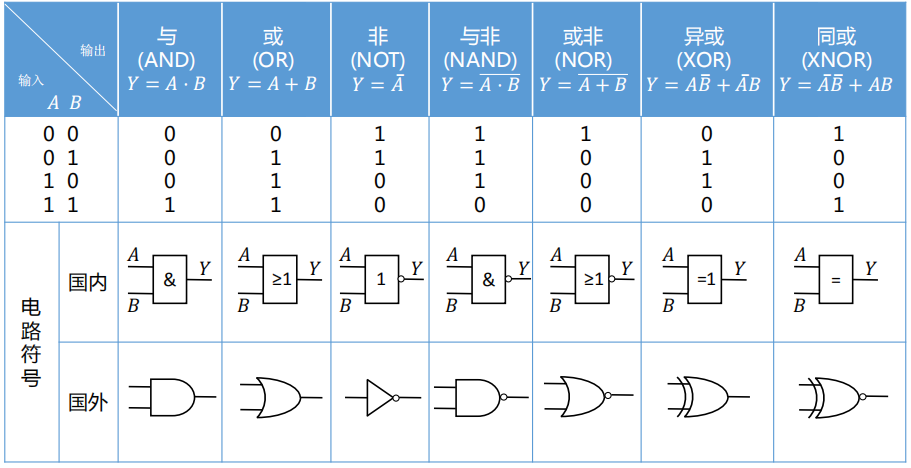

### 2.1.1 逻辑门和基本运算

逻辑设计是构建任何数字系统的基石,它涉及使用各种逻辑门来实现基本的布尔逻辑运算。在Logsim中,我们可以通过组合AND、OR、NOT等基本逻辑门来构建更复杂的逻辑电路。理解这些基本操作是掌握更高级概念的基础。

一个典型的组合逻辑门,如AND门,当且仅当所有输入为真时输出才为真。OR门则在任一输入为真时输出为真。NOT门是一个非门,用于反转输入信号的逻辑状态。这些门在Logsim中以图形化组件的形式存在,使得逻辑设计直观且易于操作。

```markdown

| 逻辑门类型 | 符号表示 | 逻辑功能描述 |

|-----------|----------|----------------------------|

| AND | A ∧ B | 当A和B都为真时,输出为真 |

| OR | A ∨ B | 当A或B至少一个为真时,输出为真 |

| NOT | ¬A | 如果A为真,则输出为假,反之亦然 |

```

### 2.1.2 逻辑电路的组合和时序设计

组合逻辑电路是指电路的输出仅取决于当前输入,而与时序无关。它们在设计中用于实现数据路径,如加法器、编码器、解码器等。时序逻辑电路则在设计中增加记忆功能,输出不仅取决于当前输入,还依赖于之前的输入状态。这通常通过引入触发器(如D触发器、JK触发器)实现。

在Logsim中设计时序逻辑电路时,可以将触发器配置为实现特定的计数器、寄存器或状态机。这些时序元素对于构建能够存储信息并基于过去事件作出反应的复杂系统至关重要。

## 2.2 Logsim中的高级逻辑概念

### 2.2.1 多路选择器和解码器的实现

多路选择器(Multiplexer,简称MUX)允许从多个输入信号中选择一个作为输出,通常由多个逻辑门组合实现。它在Logsim中是实现数据选择和路由的关键组件。解码器则是一种执行相反操作的设备,它将一个二进制数作为输入,并激活对应输入值的输出线。

一个基本的多路选择器由逻辑门和数据选择逻辑构成。假设我们有一个2-to-1多路选择器,它接受两个输入数据线和一个选择线,输出则根据选择线的状态来选择输入数据线。

```logsim

// 2-to-1 MUX 实现(伪代码)

if (select_line) {

output = input1;

} else {

output = input2;

}

```

### 2.2.2 状态机设计和逻辑优化

状态机是数字电路设计中用于处理特定输入序列并产生相应输出序列的模型。它包含一组状态、一个初始状态和根据输入以及当前状态进行状态转换的规则。在Logsim中,我们可以设计出能够识别特定模式或执行复杂任务的状态机。

设计状态机时需要考虑以下要素:状态数量、状态转换逻辑、输出逻辑以及是否需要存储输入。设计完成后,通常要进行逻辑优化以减少所需的逻辑门数量,降低电路复杂度,提高效率。一种常见的优化方法是状态编码的优化,将状态机的状态编码为二进制值时,尽量减少状态转换所需的逻辑门。

## 2.3 Logsim控制逻辑的限制与挑战

### 2.3.1 设计中的常见错误

在设计过程中,设计师常会遇到一些常见的错误,比如违反时序约束、未能正确初始化状态机等。确保电路的时序正确是设计成功的关键,如果时序设置不当,可能会导致输出结果出现意外或不稳定的行为。

为了帮助识别这些错误,Logsim提供了一系列的诊断工具,包括时序分析器和波形观察器。通过检查时序约束,我们可以确保电路中没有冲突的信号转换,以减少潜在的设计缺陷。

### 2.3.2 硬件资源与性能平衡

在任何逻辑设计项目中,设计者都会面临资源消耗与性能优化的权衡。为了在有限的硬件资源下获得最佳性能,需要深入了解硬件的工作原理,包括门延迟、路径延迟、功耗等因素。

在Logsim中,我们可以通过分析电路的延迟路径,确定瓶颈所在。这涉及到对电路进行仔细的检查,可能需要重构电路逻辑或优化门的布局来减少延迟和提高效率。这在设计大型或要求严格的系统时尤其重要。

通过上述分析,我们对Logsim控制逻辑的基础知识有了深入的理解,并且学到了如何处理实际设计中的高级概念和挑战。在第三章,我们将进一步讨论Logsim控制逻辑的实践案例,以加深理论知识与实际应用之间的联系。

# 3. Logsim控制逻辑实践案例

#### 3.1 初学者的入门实践

##### 3.1.1 从简单的电路开始

对于初学者来说,理解并掌握Logsim控制逻辑的最好方式是从基础开始,构建简单的电路逻辑。首先,我们需要熟悉Logsim的界面和基本工具。界面通常包括工具栏、设计区域和属性窗口。Logsim提供了丰富的逻辑门组件,如AND、OR、NOT、NAND、NOR、XOR等,这些是构建任何复杂逻辑电路的基础。

为了开始我们的实践,我们可以构建一个简单的组合逻辑电路,比如一个半加器。半加器能够实现两个一位二进制数的加法运算,产生一个和位以及一个进位位。在Logsim中,我们将通过拖放逻辑

0

0