【指令缓存优化】:华中科技大学报告揭示CPU设计的性能提升关键

发布时间: 2024-12-25 06:23:40 阅读量: 16 订阅数: 12

华中科技大学mips cpu源代码文件

# 摘要

CPU指令缓存作为处理器性能的关键组成部分,对系统执行速度和效率有着决定性的影响。本文系统性地介绍了指令缓存的基本概念、工作原理以及性能优化技术。从指令预取技术、缓存行和替换策略、缓存一致性问题到缓存容量和组织结构的优化,本文详细阐述了缓存设计的核心要素及其对性能的影响。通过实际案例分析与性能测试,本研究揭示了优化技术的应用效果,并展望了指令缓存技术未来的发展趋势,包括新兴技术的应用和对CPU设计性能的长远影响,旨在为CPU指令缓存的设计与优化提供理论依据和技术指导。

# 关键字

指令缓存;预取技术;缓存一致性;性能优化;缓存替换策略;缓存访问延迟

参考资源链接:[华中科技大学计算机组成原理实验报告-CPU设计实验.docx](https://wenku.csdn.net/doc/6401ad17cce7214c316ee402?spm=1055.2635.3001.10343)

# 1. CPU指令缓存的基本概念

在现代计算机体系结构中,CPU指令缓存扮演着至关重要的角色。作为连接中央处理单元(CPU)与主内存的桥梁,指令缓存极大程度上决定了计算机处理任务的效率和速度。当CPU执行程序时,它需要频繁地从内存中读取指令和数据,而指令缓存的引入,就是为了减少这种访问延迟。通过对内存中的数据进行缓存,它允许CPU快速地访问常用的指令和数据,显著提高执行速度。本章将详细介绍CPU指令缓存的基本概念,为理解其工作原理和优化策略打下坚实的基础。

# 2. 指令缓存的工作原理

### 2.1 指令预取技术

#### 2.1.1 预取策略的分类与选择

指令预取是一种预测性技术,旨在减少处理器因等待指令从内存中检索而空闲的时间。预取策略可以分为两类:软件预取和硬件预取。软件预取通常由编译器或程序员显式地在代码中插入预取指令,而硬件预取则由处理器自动执行,无需软件介入。

在选择预取策略时,需要权衡多个因素,包括处理器的类型、内存访问模式、以及预取对整体系统性能的影响。对于内存局部性较高的程序,软件预取可能更为有效,因为它允许更加精细的控制。而对于内存局部性不明或难以预测的程序,则硬件预取可能更为适用,因为硬件可以基于实时的行为动态地调整预取行为。

#### 2.1.2 预取算法对性能的影响

预取算法的效率直接影响了指令缓存的性能。一个有效的预取算法能够确保预取的指令尽可能地被处理器利用,减少不必要的内存访问和缓存未命中的次数。常见的预取算法包括顺序预取、分支预测、基于历史的预取等。顺序预取是最简单的形式,适用于顺序执行的代码段。分支预测则依赖于复杂的预测模型来预取可能在分支中被选中的代码。基于历史的预取算法则记录指令访问模式,利用这些模式来预测未来的访问。

预取算法的实现通常会对处理器设计带来额外的复杂性。例如,硬件预取需要在处理器中集成预取逻辑,可能会增加晶体管数量和功耗。在设计预取算法时,需要平衡预取带来的性能提升与实现的成本。

### 2.2 缓存行和缓存替换策略

#### 2.2.1 缓存行的构成与作用

缓存行是缓存中的基本单位,通常包含固定大小的数据块以及相关的标签信息。数据块中存储的是来自主内存的指令或数据副本。当处理器请求某个数据时,会根据地址信息找到相应的缓存行,如果缓存行中存在请求的数据,则发生缓存命中,否则为缓存未命中。

缓存行的大小对于缓存的效率至关重要。较大的缓存行可以减少因地址冲突导致的替换次数,但同时也增加了每次缓存行失效时需要从内存中取回的数据量,从而可能增加延迟。选择合适的缓存行大小需要综合考虑处理器架构、内存访问模式和应用场景。

#### 2.2.2 替换策略的优缺点分析

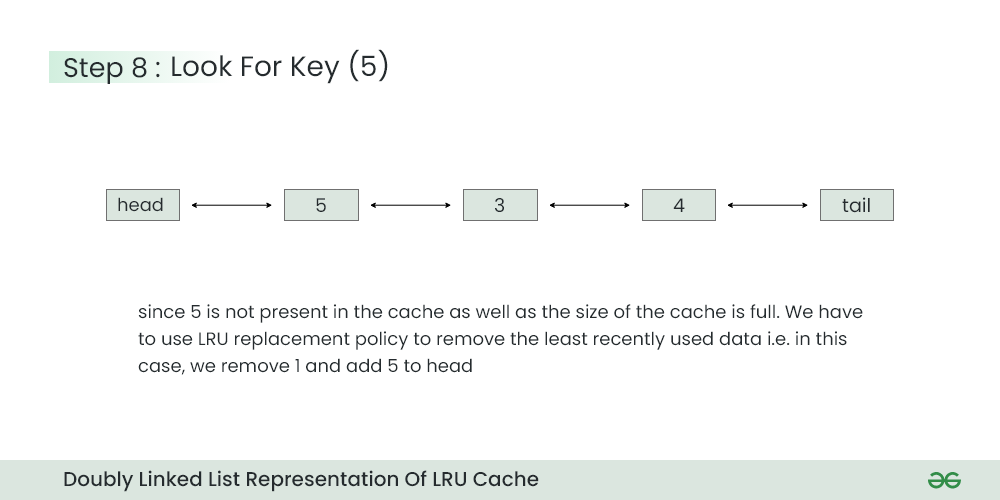

当缓存行被填满后,新的数据需要写入缓存时,就需要用到替换策略来决定替换哪一行。常见的缓存替换策略包括最近最少使用(LRU)、随机替换(Random)和先进先出(FIFO)。LRU是最常用的策略之一,它假设最长时间未被访问的行是最不可能再次被访问的。然而,LRU的实现成本较高,尤其是在大型缓存中,可能需要维护额外的状态信息。随机替换策略则避免了这种状态信息的维护,但可能会替换掉即将被访问的数据。FIFO策略是最简单的替换策略,但不考虑数据的使用模式,可能会替换掉频繁访问的数据。

选择合适的替换策略需要依据实际应用场景以及处理器的工作负载。例如,在指令缓存中,如果程序表现出良好的时间局部性,则LRU可能表现得较好。但如果访问模式更加随机,那么FIFO或随机替换可能更合适。

### 2.3 缓存一致性问题

#### 2.3.1 缓存一致性协议

缓存一致性是指在多核处理器系统中,所有处理器缓存中相同的数据必须保持一致的状态。为了解决这一问题,提出了缓存一致性协议,如MESI(修改、独占、共享、无效)协议。MESI协议通过标记缓存行的状态来维护数据的一致性。每个缓存行可以处于以下四个状态之一:修改(M)、独占(E)、共享(S)或无效(I)。当处理器想要读取或写入数据时,必须根据当前的缓存行状态来采取不同的动作,如发送消息通知其他处理器进行状态更新。

#### 2.3.2 解决缓存一致性问题的策略

为实现缓存一致性,处理器之间必须进行通信。这一通信可以通过总线、交叉开关或目录协议来实现。总线监听是一种简单的通信方式,但其效率会随着处理器数量的增加而下降。交叉开关和目录协议提供了更高效的通信机制,它们可以减少通信的冲突,提高缓存一致性的维持效率。

解决缓存一致性问题的策略需要平衡通信开销与维护一致性的需求。例如,目录协议通过集中管

0

0