【流水线技术深度解码】:华中科技大学实验报告中的高效处理器构建指南

发布时间: 2024-12-25 06:01:43 阅读量: 22 订阅数: 10

# 摘要

本文详细探讨了流水线技术的原理、设计、优化、测试以及未来的发展方向。首先介绍了流水线技术的基础概念及其在处理器设计中的核心地位。随后深入分析了流水线处理器的工作原理,包括各阶段功能、冲突解决方法和性能评估指标。进一步讨论了高效处理器设计的实践问题,涵盖了设计工具、控制单元实现、数据路径优化等关键方面。为了确保处理器设计的质量,本文还介绍了流水线处理器测试与验证的多种方法和技巧。最后,基于新兴技术,本文展望了流水线技术的未来发展趋势,包括多核架构、指令级并行以及人工智能与量子计算在该领域中的潜在应用。通过华中科技大学的实验报告,本文还提供了对高效处理器构建有启示意义的案例研究。

# 关键字

流水线技术;处理器设计;性能评估;测试与验证;多核架构;人工智能;量子计算

参考资源链接:[华中科技大学计算机组成原理实验报告-CPU设计实验.docx](https://wenku.csdn.net/doc/6401ad17cce7214c316ee402?spm=1055.2635.3001.10343)

# 1. 流水线技术概念与原理

## 1.1 流水线技术基础

流水线技术是一种将指令执行过程分解为多个可以并行处理的子过程的方法,每个子过程称为一个阶段或流水级。在计算机科学中,流水线通常用于提高处理器(CPU)的指令处理能力,类似于工厂的装配线,在不同的工作站上进行不同的生产步骤。

## 1.2 指令执行的分解

在传统的单周期处理器中,每个指令从获取、解码到执行都需要花费一个完整的时钟周期。而流水线技术允许不同的指令在不同的阶段并行处理。例如,当一条指令处于执行阶段时,另一条指令可以同时进行取指,第三条指令可以进行解码。

## 1.3 流水线的性能提升

通过流水线技术,可以在不增加单个时钟周期长度的情况下,提高指令的吞吐量,即单位时间内处理的指令数量。这种并行处理机制在理想情况下可以将CPU的性能提升至接近理论极限,但实际应用中会受到数据冲突、控制冲突与结构冲突等因素的限制。

```mermaid

graph LR

A[开始] --> B[取指]

B --> C[译码]

C --> D[执行]

D --> E[访存]

E --> F[写回]

F --> G[结束]

```

在上述流程图中,我们可以清晰地看到流水线的各个阶段,指令从取指开始,依次经过各个阶段直至完成。每个节点都代表一个处理步骤,流水线化使得整个处理器的效率得到显著提升。

# 2. 处理器设计的基本理论

## 2.1 指令集架构基础

### 2.1.1 指令集的概念和作用

指令集是处理器能够理解和执行的命令集合。每条指令都由一系列的操作码(操作的类型)和操作数(操作的数据)构成,它们是计算机编程语言的最低层表示。指令集架构(ISA)作为软硬件之间的界面,定义了软件能做什么以及硬件应该如何实现这些功能。

在处理器设计中,指令集架构扮演着至关重要的角色。它不仅决定了处理器能够执行哪些操作,还影响着软件的编写方式、程序的效率以及硬件设计的复杂性。一个良好的指令集应该具备足够的功能来支持高效的程序实现,同时应尽量简单以便于硬件设计和优化。

### 2.1.2 常见指令集架构的比较

市场上存在多种指令集架构,其中最著名的包括复杂指令集计算(CISC)和精简指令集计算(RISC)。CISC以Intel x86架构为代表,其特点是指令多样、功能复杂,每条指令能够完成较为复杂的操作。RISC以ARM和MIPS架构为代表,特点是简单、快速和高度优化的指令集。

通过下表,我们可以更直观地理解这两种架构的差异:

| 特性 | CISC | RISC |

| --- | --- | --- |

| 指令数量 | 较多 | 较少 |

| 指令复杂度 | 较高 | 较低 |

| 指令长度 | 可变 | 固定 |

| 执行周期 | 较长 | 较短 |

| 指令执行 | 可能包含多个操作 | 通常只执行一个操作 |

| 举例 | Intel x86 | ARM, MIPS |

了解这些特点能够帮助我们选择或设计适合特定应用场景的处理器架构。例如,对于资源受限的嵌入式系统,RISC架构是一个优选,因为其简单性和高效性。而对于需要高度兼容性的通用计算机系统,CISC架构则更为常见。

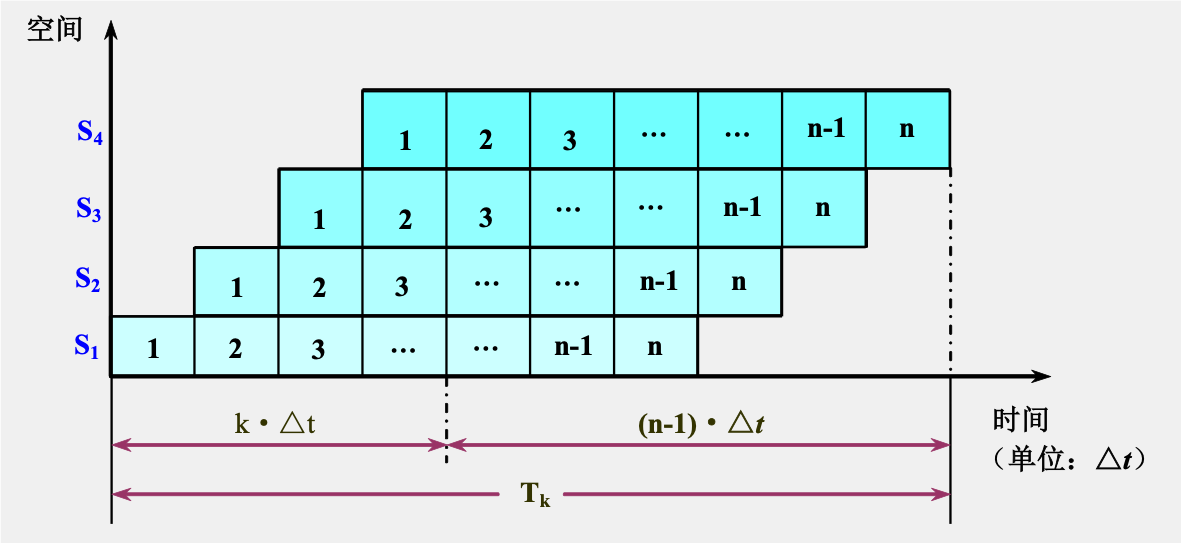

## 2.2 流水线处理器的工作原理

### 2.2.1 流水线的各个阶段和功能

流水线技术是现代处理器设计的核心,它将指令的执行过程划分为多个阶段,每个阶段由不同的功能单元处理。常见的流水线阶段包括取指(IF)、译码(ID)、执行(EX)、访存(MEM)和写回(WB)。

- **取指(IF)阶段**:从指令缓存中读取指令。

- **译码(ID)阶段**:解析指令的操作码和操作数。

- **执行(EX)阶段**:执行算术逻辑单元(ALU)操作。

- **访存(MEM)阶段**:访问数据缓存,进行数据读写操作。

- **写回(WB)阶段**:将执行结果写回到寄存器。

下面是一个简化的流水线操作的mermaid流程图:

```mermaid

graph TD

A[开始] --> B[IF: 取指令]

B --> C[ID: 译码]

C --> D[EX: 执行]

D --> E[MEM: 访存]

E --> F[WB: 写回]

F --> G[结束]

```

### 2.2.2 数据冲突、控制冲突与结构冲突的解决方法

在流水线中,冲突指的是由于资源竞争或者数据依赖导致流水线不能有效前进的情况。冲突主要包括数据冲突、控制冲突和结构冲突。

- **数据冲突**:可以通过数据前递(forwarding)技术解决,即将后续阶段产生的数据提前传递给需要它的前序阶段。

- **控制冲突**:通常与分支指令相关,可以使用分支预测技术来缓解,比如双发射技术或者延迟分支技术。

- **结构冲突**:由于硬件资源被多个指令同时请求而产生,解决方法通常是引入更多的功能单元或者增加访问资源的路径。

### 2.2.3 流水线的性能评估指标

评估流水线性能的主要指标包括吞吐率、时钟周期时间和加速比。其中,吞吐率(Throughput)指单位时间内完成指令的数量;时钟周期时间(Cycle Time)指完成一条指令所需的最小时间;加速比(Speedup)指优化前后的性能比。

计算加速比的公式为:

\[ \text{加速比} = \frac{\text{优化前的执行时间}}{\text{优化后的执行时间}} \]

## 2.3 高级流水线设计技术

### 2.3.1 超流水线与超标量技术

超流水线和超标量是两种提高处理器性能的技术。超流水线通过增加流水线的深度来提高时钟频率,本质上是每个时钟周期内完成指令的一部分。超标量则是通过并行处理多条指令来提高吞吐率。

### 2.3.2 预测技术和指令重排策略

为了进一步提升流水线效率,现代处理器引入了分支预测技术和指令重排技术。分支预测技术预测程序的分支路径,以减少分支指令导致的停顿。指令重排技术则是在不影响程序结果的前提下,通过重新安排指令执行顺序来避免冲突。

重排策略可以通过编译器或硬件实现。编译器优化通常在编译时进行,而硬件指令重排则在运行时动态进行。

在下一章节中,我们将继续探讨处理器设计的实践应用,包括流水线控制单元的实现和数据路径优化。

# 3. 高效处理器设计实践

## 3.1 设计工具和环境搭建

在现代处理器设计中,合适的设计工具和环境搭建对于实现高效设计至关重要。设计工具的选择与配置是构建高效处理器设计流程的基石,而环境搭建与验证流程确保了设计的正确性和可扩展性。

### 3.1.1 设计工具的选择与配置

设计工具包括硬件描述语言(HDL)模拟器、综合工具、时序分析软件以及布局布线工具。对于HDL模拟器,像ModelSim和Vivado Simulator提供了强大的仿真环境,用于验证设计的逻辑功能。综合工具,如Synopsys Design Compiler, 将HDL代码转换为可以在实际硬件上实现的门级描述。时序分析软件,例如Cadence Tempus, 确保设计满足严格的时序要求。布局布线工具如Cadence Genus, 则负责将综合后的设计映射到具体的物理布局上。

选择设计工具时,需要考虑工具的综合能力、仿真速度、易用性以及与现有设计流程的兼容性。对于流水线处理器设计而言,还应考虑工具对于流水线级数的支持和优化能力。

### 3.1.2 环境搭建和验证流程

环境搭建首先是安装和配置上述工具,确保它们能够协同工作。这可能包括设置环境变量、安装必要的库文件和依赖包。然后需要进行验证流程的建立,它包括编写测试平台、运行仿真、收集结果并分析。在验证流程中,常见的做法是编写针对各个流水线阶段的测试向量,测试数据通路的一致性和流水线的性能表现。

代码块和表格是描述此过程的重要元素,以下是一个简化的代码块示例,说明如何创建一个基本的测试平台:

```verilog

// Testbench for Pipeline Processor Verification

module testbench;

// Inputs

reg clk;

reg reset;

reg [31:0] instruction_in;

// Outputs

wire [31:0] data_out;

// Instantiate the Unit Under Test (UUT)

pipeline_proc

```

0

0