【计算机体系结构终极指南】:掌握从入门到精通的20个核心概念

发布时间: 2024-12-15 02:22:23 阅读量: 14 订阅数: 12

计算机网络期末复习指南:核心概念、体系结构、传输、协议、设备与安全

参考资源链接:[王志英版计算机体系结构课后答案详解:层次结构、虚拟机与透明性](https://wenku.csdn.net/doc/646747c6543f844488b70360?spm=1055.2635.3001.10343)

# 1. 计算机体系结构基础概述

计算机体系结构是研究计算机硬件与软件之间交互方式的学科,它对整个计算机系统的性能和功能起着决定性作用。计算机体系结构的定义和重要性不仅在于硬件的物理布局,还包括系统的设计理念、数据处理流程以及软件与硬件之间的协同工作方式。

随着技术的飞速发展,计算机体系结构经历了从早期的冯·诺依曼体系到现代的多核和并行处理架构的演变。历史上,随着晶体管技术的进步,我们可以看到摩尔定律对于计算机性能提升的持续推动作用。

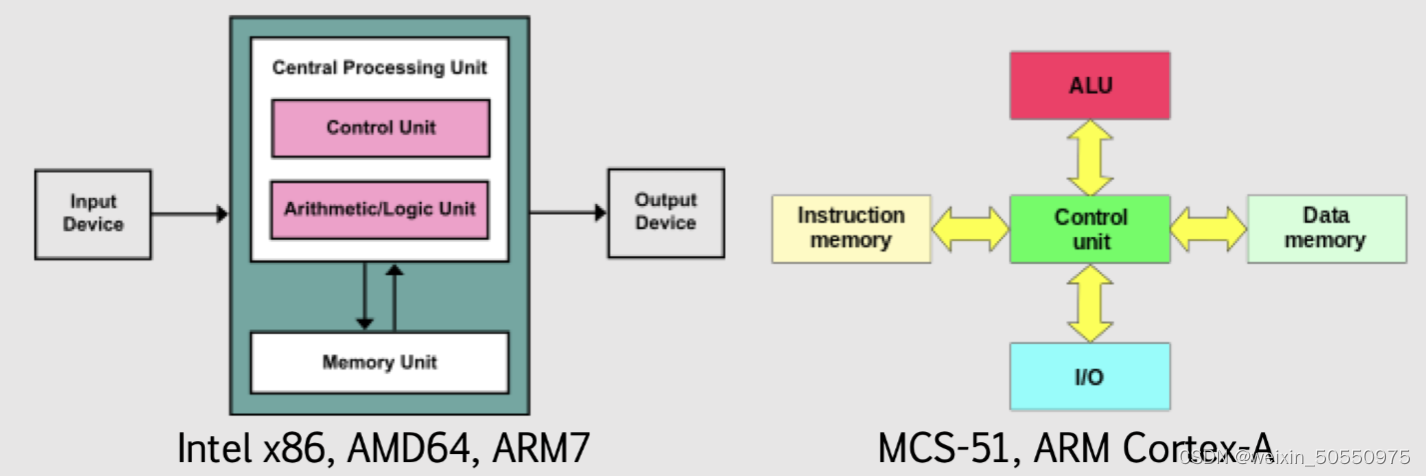

体系结构的基本组成通常包括处理器(CPU)、内存、输入输出系统(I/O)和存储设备等,每部分都承担着独特的功能,共同确保计算机系统的高效运行。了解这些组成及其交互是深入研究计算机体系结构不可或缺的基础。

# 2. 核心硬件组件解析

### 内存和缓存

#### 内存的类型和管理机制

内存是计算机系统中不可或缺的组件,它负责存储和快速检索程序数据。根据其存在形式,内存分为随机存取存储器(RAM)和只读存储器(ROM)。RAM又可分为静态RAM(SRAM)和动态RAM(DRAM)。SRAM通常用作CPU缓存,因为它存取速度快,但成本较高;而DRAM用于主存,成本较低但需要定期刷新以维持数据。

内存管理涉及多个方面,包括内存地址映射、内存分页和交换(swap)机制。现代操作系统使用虚拟内存系统来管理内存,通过分页机制,将物理内存划分为固定大小的页(page),并将程序的虚拟地址映射到物理地址。这种抽象允许操作系统灵活管理物理内存,提供了一个统一的大容量地址空间给用户程序。

#### 缓存的设计原理和优化策略

缓存是位于CPU和主存之间的快速存储设备,其设计目的是减少CPU访问主存所需的时间。缓存利用了“局部性原理”,即在很短的时间内,程序倾向于访问相同的数据或地址附近的数据。缓存通常分为几个级别,L1、L2和L3,其中L1速度最快但容量最小,L3容量最大但速度相对较慢。

优化缓存性能的策略包括:

- 增加缓存行(cache line)大小,减少缓存未命中时从主存加载数据的次数。

- 实现写缓冲,以减少写回主存的时间。

- 使用预取技术,预测将要访问的数据,并提前加载到缓存中。

- 采用多级缓存策略,其中各级缓存相互补充,优化内存访问延迟和带宽。

### 输入输出系统(I/O)

#### I/O 端口和总线

I/O 端口是连接设备和CPU的接口,允许数据在处理器和外围设备间传输。总线是多个硬件设备共享的信号路径,是电子系统中数据传输的通道。I/O端口和总线共同构成了计算机的输入输出系统,它负责管理数据的输入输出操作。

一个典型的I/O系统包括:

- 控制器和适配器,用于管理特定类型的设备。

- I/O端口,提供与CPU通信的接口。

- 总线,用于连接多个设备并传输数据。

#### I/O 通信协议和标准

为了确保不同的硬件设备能够有效地通信,制定了各种I/O通信协议和标准。例如,SCSI(小型计算机系统接口)是一种用于连接硬盘驱动器、光盘驱动器和扫描仪等设备的并行接口协议。而SATA(串行ATA)是目前广泛使用的硬盘接口标准,它以串行方式传输数据,具有较高的传输速率。

USB(通用串行总线)也是一种流行的标准,它通过一个标准化的接口支持数据和电源的传输,支持热插拔。此外,PCI(外设组件互连)总线广泛用于计算机内部组件之间的连接。

### 处理器架构

#### CISC与RISC架构的对比分析

复杂的指令集计算机(CISC)和精简指令集计算机(RISC)是两种不同的处理器架构设计。

CISC架构,以x86架构为代表,特点是提供丰富的指令集,这些指令可以完成复杂的操作。在早期,由于编译技术的限制,使用CISC架构可以直接在硬件层面上执行高级语言中的复杂操作,从而简化了编译器的设计。

而RISC架构,以ARM架构为例,采用更简单的指令集,每个指令的执行速度非常快,但要完成复杂操作需要多条指令。RISC的优势在于其简单的设计可以达到更高的执行速度,并且有利于指令流水线的实现。

#### 多核处理器和并行处理

随着集成电路技术的发展,处理器的尺寸不断减小,晶体管数量却在不断增加。为了更有效地利用这些晶体管,处理器设计者开始在单个芯片上集成多个处理器核心,形成了多核处理器架构。多核处理器允许操作系统并行执行多个线程,大大提高了计算机的处理能力,特别是在执行多任务环境中。

并行处理技术通过在硬件和软件层面上利用多核处理器的优势,对程序的执行进行优化。程序可以通过多种方式进行并行化,包括数据并行和任务并行,从而提高计算效率,减少程序运行时间。

多核处理器和并行处理要求操作系统、编程语言和应用程序软件共同协作,有效地分配和管理计算资源,以充分挖掘多核计算的潜力。

# 3. 中央处理单元(CPU)的工作原理与优化

## 3.1 CPU的设计和结构

### 3.1.1 指令集架构和流水线技术

中央处理单元(CPU)是计算机系统的核心部件,负责执行指令和处理数据。CPU的设计复杂,主要依赖于其指令集架构(ISA),它定义了CPU能理解和执行的指令集。ISA不仅涉及数据类型、寄存器、寻址模式,还包括编程模型等高级特性。

在讨论CPU设计时,流水线技术是一个不可忽视的概念。它是一种将指令执行分解为多个子过程的技术,每个子过程由流水线的特定阶段完成。通过流水线,CPU能够在同一时刻对多个指令执行不同的处理阶段,从而提高总体的执行效率。现代CPU的流水线可能非常复杂,包括从简单的五级流水线到更高级的深度流水线。

例如,一个典型的五级流水线包括如下阶段:

1. 取指(Fetch):从内存中取得指令。

2. 解码(Decode):分析指令中的操作码和操作数。

3. 执行(Execute):执行算术或逻辑运算。

4. 访存(Memory access):访问数据存储器,若指令中包含数据存取。

5. 写回(Writeback):将执行结果写回寄存器。

代码块示例:

```assembly

; 一个简单的汇编级示例指令序列

; 假设使用的是x86架构

; 指令序列将两个寄存器中的值相加,并将结果存储在第一个寄存器中

mov eax, 1 ; 将立即数1传送到寄存器eax

mov ebx, 2 ; 将立即数2传送到寄存器ebx

add eax, ebx ; 将寄存器ebx的值加到eax,并存储结果到eax

```

### 3.1.2 超线程与多线程处理

随着处理器技术的发展,多核处理器已变得非常普遍,但为了进一步提高性能,引入了超线程(Hyper-Threading)技术,也称为多线程处理。超线程允许单个物理核心同时处理多个线程,通过在核心内部模拟两个逻辑核心来实现。

这种技术允许多个线程在执行过程中共享核心内的资源,如ALU(算术逻辑单元)、缓存等。当一个线程等待(例如,等待数据从内存中加载到缓存),另一个线程可以占用核心资源继续执行。这显著提高了核心的利用率和整体系统性能。

## 3.2 CPU性能评估

### 3.2.1 性能指标和基准测试

衡量CPU性能的指标包括时钟频率(CPU运行速度)、核心数量、线程数、缓存大小等。这些指标通过基准测试得到量化的性能表现。基准测试是一种标准化的性能评估方法,旨在在控制条件下重复执行测试套件,以便比较不同系统的性能。

一个著名的基准测试工具是SPEC CPU,它包括一系列实际应用程序的测试用例,可以评估CPU在不同类型的工作负载下的性能表现。除了SPEC,还有其他测试,比如Cinebench、PassMark等,用于不同的性能评估目的。

### 3.2.2 性能优化技巧和案例分析

为了提升CPU性能,开发者和系统管理员可以采取多种优化手段。以下是一些常见的CPU性能优化技巧:

1. 调整代码来提高指令级并行性(Instruction-level parallelism, ILP),利用现代CPU的流水线和超标量架构。

2. 使用多线程或多进程来充分利用多核CPU。

3. 减少分支预测错误率,使用条件编译等技术来编写预测性更强的代码。

4. 避免缓存未命中,优化数据结构布局和访问模式以提高缓存命中率。

案例分析:

假设我们正在优化一个科学计算程序,发现大部分时间都花在了矩阵乘法上。通过分析,我们发现CPU缓存未命中率较高,原因是数据访问模式不规律。解决方法是采用分块矩阵乘法算法,将大矩阵分割为小块,然后依次处理每个小块,这样可以显著提高缓存命中率,减少对内存的访问次数,从而加快计算速度。

代码块示例:

```c

// 分块矩阵乘法算法示例

void matrix_multiply_block(int size, float **C, float **A, float **B) {

const int block_size = 32; // 根据缓存大小设定合适的块大小

for (int bi = 0; bi < size; bi += block_size) {

for (int bj = 0; bj < size; bj += block_size) {

for (int bk = 0; bk < size; bk += block_size) {

for (int i = bi; i < MIN(bi + block_size, size); i++) {

for (int j = bj; j < MIN(bj + block_size, size); j++) {

for (int k = bk; k < MIN(bk + block_size, size); k++) {

C[i][j] += A[i][k] * B[k][j];

}

}

}

}

}

}

}

```

## 3.3 CPU与系统互连

### 3.3.1 前端总线和高速缓存一致性

CPU与系统其他组件(如内存、I/O设备)的互连主要通过前端总线(Front Side Bus, FSB)来实现。FSB负责传输数据、地址和控制信号。为了保证数据的一致性,特别是在多核处理器中,需要使用高速缓存一致性协议,如MESI(修改、独占、共享、无效)。

缓存一致性协议确保了每个处理器核心上的缓存可以同步更新,共享数据的一致视图。若一个核心修改了缓存中的数据,其他核心必须被通知这一更新,从而保持一致性。

### 3.3.2 系统级的性能瓶颈分析

系统级的性能瓶颈分析关注的是整个系统性能受限的环节。常见的瓶颈包括I/O带宽、内存带宽、网络延迟等。要进行性能瓶颈分析,首先要利用性能分析工具(如oprofile、sysstat等)进行监控和采样。

一种常用的分析方法是通过负载测试(如压力测试、稳定性测试)来模拟实际的高负载环境,然后使用分析工具追踪资源利用情况。通过这种方式,可以识别出最影响性能的瓶颈点并优先进行优化。

### 3.3.3 系统架构优化

系统架构优化聚焦于提高系统的整体性能和效率,可能包括:

- 数据流优化:确保数据可以尽可能快地在系统内流动,避免不必要的等待和传输。

- 内存子系统优化:根据工作负载特性调整内存配置,如使用更快的内存技术或调优内存子系统的结构。

- 电源管理优化:通过动态调整电源状态来平衡性能和能耗,以适应不同的计算需求和能效目标。

- 热设计优化:优化散热解决方案以维持CPU及其他组件在最佳工作温度,防止因过热导致性能下降或硬件损坏。

最后,随着技术的发展,现代计算机体系结构趋向于采用异构计算架构,整合不同类型的处理器和加速器(如GPU、FPGA)来共同完成计算任务,以进一步提升性能和能效。

# 4. 存储技术及其在体系结构中的角色

## 4.1 磁盘存储技术

### 硬盘驱动器(HDD)与固态驱动器(SSD)

磁盘存储技术是计算机体系结构中负责数据持久化存储的核心组件。其中,硬盘驱动器(HDD)和固态驱动器(SSD)是最为常见的存储设备。

HDD是传统磁存储设备,其工作原理基于磁头在旋转的磁盘表面读写数据。HDD的优点在于成本效益高,但缺点是机械部件易磨损且速度相对较慢。典型的HDD通过SATA或SAS接口与主板连接。

与HDD不同,SSD是基于闪存的存储设备,没有机械移动部件,因此具有更快的读写速度和更好的耐冲击性。SSD通过NVMe(Non-Volatile Memory Express)接口或SATA接口连接。虽然SSD的成本较高,但随着闪存技术的进步和价格的下降,SSD已经逐渐成为主流存储选项。

### RAID和数据冗余技术

RAID(Redundant Array of Independent Disks)技术通过组合多个硬盘驱动器来提升存储性能、可靠性和/或容量。RAID技术有多种级别,每种级别针对不同的性能和数据安全需求。

RAID 0通过条带化(Striping)提高性能,但不提供冗余。RAID 1使用镜像(Mirroring)提供冗余,但不提升性能。RAID 5和RAID 6提供性能提升和一定程度的冗余,通过奇偶校验信息保护数据。

数据冗余技术的另一个例子是Erasure Coding,它比传统的RAID镜像或奇偶校验提供更好的空间效率。尽管有性能开销,但这种方法在存储大量数据时非常有效。

```mermaid

flowchart LR

A[硬盘驱动器 HDD] -->|慢速| B[高容量成本比]

C[固态驱动器 SSD] -->|快速| D[低容量成本比]

E[RAID级别] -->|RAID 0| F[性能优化]

E -->|RAID 1| G[数据镜像]

E -->|RAID 5| H[奇偶校验]

E -->|RAID 6| I[双奇偶校验]

E -->|Erasure Coding| J[空间效率优化]

```

## 4.2 内存层次结构

### 主存、虚拟内存和交换空间

内存层次结构在现代计算机体系结构中起着至关重要的作用,包括主存、虚拟内存和交换空间的概念。

主存(RAM)是计算机运行时用于存储程序和数据的易失性存储器。它为CPU提供高速访问,以执行程序代码和处理数据。然而,主存的容量受限,无法存储所有运行时数据。

为了解决这一限制,虚拟内存系统将数据从磁盘(硬盘)加载到主存。当主存不足以存储所有程序数据时,操作系统将部分数据移出主存,存储到交换空间(也称为分页文件)。这种技术允许系统运行内存密集型应用,但访问交换空间比直接访问主存慢得多。

### 存储层次的设计原则和影响因素

设计存储层次结构时需要考虑多个因素。首先,存储设备的访问速度和成本直接影响性能和成本效益。其次,存储层次需要与应用程序的数据访问模式相匹配。例如,频繁访问的数据最好存储在快速设备上。

数据局部性原则是存储层次设计的另一个重要考虑因素,包括时间局部性和空间局部性。基于局部性原理,缓存和主存通常设计为小而快速的存储设备,而备份存储则可以更大但速度较慢。

```mermaid

graph LR

A[主存 RAM] -->|快速访问| B[直接存取]

A -->|容量限制| C[使用虚拟内存]

C -->|空间不足| D[交换空间]

D -->|较慢访问| E[磁盘存储]

```

## 4.3 高级存储系统

### 分布式文件系统和存储网络

随着大数据和云计算的兴起,分布式文件系统和存储网络变得越来越重要。这些系统通过网络连接多个服务器上的存储资源,为用户和应用程序提供高可用性、容错性和可伸缩性。

分布式文件系统,如Google的GFS(Google File System)和Apache的HDFS(Hadoop Distributed File System),在处理大规模数据集方面表现出色。它们被设计成能够在廉价的商用硬件上运行,并能够处理硬件故障。

存储网络,如SAN(Storage Area Network)和NAS(Network Attached Storage),通过特定的网络协议提供文件共享和存储资源的集中管理。

### 存储虚拟化和云存储服务

存储虚拟化技术允许将多个存储设备抽象为一个逻辑单元,从而简化存储管理并提高资源利用率。虚拟化层可以隐藏物理存储的复杂性,并提供灵活的数据迁移和快照功能。

云存储服务提供在线数据存储和备份解决方案。服务提供商如Amazon S3、Google Cloud Storage和Microsoft Azure Storage,为用户和企业提供按需存储资源。云存储服务利用大规模数据中心的优势,提供弹性、高可用性和数据安全。

```mermaid

graph LR

A[分布式文件系统] -->|数据处理能力| B[大规模数据集]

A -->|高可用性| C[容错机制]

D[存储网络] -->|集中管理| E[文件共享]

D -->|网络协议| F[硬件隔离]

G[存储虚拟化] -->|逻辑抽象| H[简化管理]

G -->|虚拟层功能| I[数据迁移和快照]

J[云存储服务] -->|弹性伸缩| K[资源按需分配]

J -->|数据安全| L[高可用性和备份]

```

在存储技术领域,各种技术的融合和创新将不断推动计算机体系结构向前发展。无论是从传统的磁盘存储到新型的固态驱动器,还是从单一存储设备到复杂的分布式文件系统,存储技术的演进都在为计算机体系结构提供支持和动力。随着云存储服务和存储虚拟化技术的日益成熟,未来的存储解决方案将更加灵活、高效和智能化。

# 5. 计算机体系结构的未来趋势和创新

## 5.1 新兴技术与体系结构

### 5.1.1 量子计算和光计算的潜力

量子计算和光计算代表了计算技术的前沿发展。量子计算利用量子位(qubits)代替传统比特,通过量子叠加和纠缠状态实现了比传统计算更快的算法。例如,Shor的算法可以在多项式时间内完成大数质因数分解,而传统计算机却需要超多项式时间。

**量子位和量子计算的实现原理:**

- 量子位可以同时处于0和1的状态,称为量子叠加。

- 量子纠缠使得两个或多个量子位的状态不再是独立的,对其中一个量子位的操作瞬间影响到另一个。

- 量子门是量子计算的基本操作单元,通过特定的量子门实现对量子位的操作。

量子计算机的实现对体系结构提出了新的要求,例如需要超低温环境以保持量子位的稳定,以及高度隔离的物理空间以避免外部干扰。

### 5.1.2 人工智能(AI)在体系结构中的应用

人工智能技术正迅速改变着计算机体系结构。例如,神经网络处理器(NPU)和AI加速器被设计来优化机器学习任务,这些硬件加速器通过专用指令集和并行处理能力显著提高了AI任务的性能。

**AI加速器的设计和应用场景:**

- AI加速器在芯片设计中通常包括大量的并行处理单元,以支持矩阵乘法等AI工作负载。

- 专用的AI框架和库可以利用这些加速器,如TensorFlow、PyTorch等。

- AI芯片开始出现在边缘计算设备中,实现本地的快速推理和决策。

## 5.2 可持续和绿色计算

### 5.2.1 能效比(Energy per Instruction)和绿色设计原则

随着数据中心的规模不断扩大,能源消耗问题日益严重。能效比(Energy per Instruction, EPI)成为衡量计算机系统能量效率的重要指标。降低EPI意味着在完成相同计算任务的情况下,系统的能耗更低。

**绿色计算的实践:**

- 采用节能型处理器和高效电源。

- 利用冷却技术优化,例如液冷技术降低数据中心温度。

- 实现智能的能耗管理,比如根据负载动态调整计算资源。

设计绿色计算机体系结构还涉及对软件和硬件进行整合,以提高整体系统的能源效率。比如,操作系统可以动态调整CPU的频率和电压,以应对不同的负载需求。

### 5.2.2 资源管理和回收技术

随着硬件资源的不断增长,资源管理和回收成为绿色计算的关键组成部分。高效的资源分配可以保证计算任务在较少的硬件资源上运行,而资源回收技术则确保资源得到最大化利用。

**资源回收和管理的技术趋势:**

- 虚拟化技术允许单一物理服务器上运行多个虚拟机,提高了硬件资源的使用效率。

- 容器化技术如Docker提供了轻量级的虚拟化解决方案,使得应用的部署和迁移更加高效。

- 自动化资源调度策略和负载均衡技术动态分配计算资源,以适应不断变化的工作负载。

## 5.3 安全性和隐私保护

### 5.3.1 安全架构和加密技术

计算机体系结构的安全性是当今IT领域面临的一大挑战。硬件级别的安全架构,比如可信执行环境(TEE),提供了隔离执行代码的安全空间,以保护敏感数据不被未授权访问。

**加密技术的运用:**

- 硬件加速器可以加速加密算法的执行,如AES、RSA等,提高了数据保护的效率。

- 采用安全芯片设计,如TPM(Trusted Platform Module),来安全地存储加密密钥和其他敏感信息。

- 硬件级别的安全特性如Intel SGX(Software Guard Extensions),允许开发者在硬件保护的区域内执行特定代码。

### 5.3.2 隐私保护和数据安全的最佳实践

隐私保护和数据安全已经成为设计计算机系统不可或缺的一部分。最佳实践包括从体系结构设计的早期阶段就将安全性考虑进去,以及对数据访问进行细粒度控制。

**体系结构级别的隐私保护:**

- 数据在存储和传输时都应进行加密处理。

- 定期进行安全漏洞扫描和渗透测试来发现潜在风险。

- 实施最小权限原则,确保用户和程序只能访问其需要的数据和资源。

通过上述方法,未来的计算机体系结构将继续朝着更高性能、更节能、更安全和保护用户隐私的方向发展。这些创新不仅会增强计算能力,也将为用户和企业提供更加可靠和可持续的技术支持。

0

0