【Vivado与ModelSim协同仿真终极指南】:从新手到专家的10大必学技巧

发布时间: 2025-01-09 22:03:37 阅读量: 3 订阅数: 8

FPGA那些事儿--Modelsim仿真技巧REV6.0_FPGA的仿真_fpgamodelsim仿真_FPGA那些事儿_

# 摘要

本文旨在探讨Vivado与ModelSim协同仿真的基础知识与高级应用。首先介绍了Vivado与ModelSim的环境配置、项目管理以及基本使用方法。紧接着,重点讨论了协同仿真中的关键技巧,如设计模块化、测试平台建立和波形分析。第四章进一步探索仿真优化、高级测试技术应用以及多核仿真与并行测试的优势与实践。最后,通过多个实战案例,详细分析了FPGA项目的仿真流程、典型工程案例的协同仿真效果及专家级别的调试与性能提升策略。本文为从事FPGA设计与仿真的工程师提供了全面的技术指南和实用参考。

# 关键字

Vivado;ModelSim;协同仿真;模块化设计;测试平台;波形分析;性能优化;多核仿真;并行测试;FPGA调试

参考资源链接:[Vivado与ModelSim联合仿真教程:设置与常见问题](https://wenku.csdn.net/doc/558d2rnpxp?spm=1055.2635.3001.10343)

# 1. Vivado与ModelSim协同仿真的基础知识

## 1.1 简介

在现代FPGA设计流程中,Vivado和ModelSim是两大不可或缺的工具,它们共同为设计者提供了从设计实现到功能验证的全套解决方案。Vivado是Xilinx公司推出的FPGA设计套件,提供了高级的综合、布局布线以及分析工具。ModelSim则是业界广泛使用的硬件描述语言仿真软件,提供高性能的仿真能力和丰富的调试工具。

## 1.2 协同仿真概述

协同仿真指的是将Vivado与ModelSim结合使用,以提高设计验证的效率和准确性。Vivado负责生成仿真所需的波形文件和测试平台,而ModelSim则利用这些文件进行详尽的功能和时序仿真。这样可以充分发挥两个工具的优势,快速发现设计中的错误,避免在实际硬件上的问题。

## 1.3 协同仿真的重要性

对于复杂的FPGA设计项目,仅仅依靠单一的仿真工具很难全面验证设计的正确性。通过Vivado和ModelSim的协同仿真,设计者可以从不同角度检验设计,提高仿真覆盖率。此外,协同仿真还支持时序分析,可以更精确地模拟设计在实际硬件上的运行情况,这对于要求高准确性的设计验证尤为重要。

# 2. Vivado环境配置与项目管理

## 2.1 Vivado界面和工作流程概述

### 2.1.1 Vivado界面布局

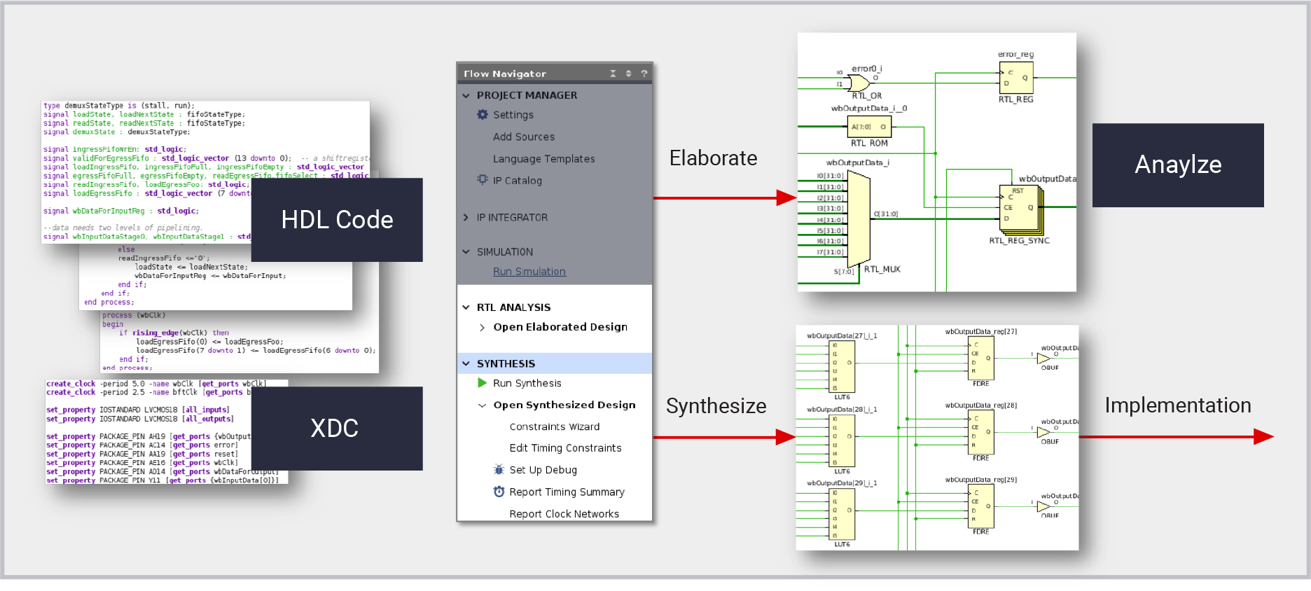

Vivado是Xilinx公司推出的一款强大的FPGA设计套件,提供了一体化的界面布局,适用于从设计输入到硬件实现的整个流程。界面通常包括项目管理、IP集成、综合、实现以及设备配置等多个模块。

在Vivado的主界面中,左侧是工具导航栏,显示了不同的设计任务和工具模块。右侧是具体任务的详细操作界面,可根据当前进行的任务切换不同的标签页。顶部菜单提供了常用的文件、编辑、视图、工具、窗口等操作选项。底部状态栏显示当前项目的状态信息和日志输出。

### 2.1.2 创建和管理工程

创建一个新的工程首先需要通过“File”菜单选择“New Project...”进行项目设置。在此过程中,需要指定项目名称、位置以及目标FPGA设备。接着,用户需要选择项目中将包含的设计源文件类型,例如Verilog、VHDL或者XDC约束文件等。完成初始设置后,Vivado会生成一个包含必要文件和目录的工程结构。

管理工程时,需要处理源文件、约束文件以及仿真文件等。Vivado提供了一个直观的文件管理界面,允许用户轻松添加、删除或修改文件。此外,用户可以通过“Settings”对话框定制项目特定的综合和实现选项,从而确保设计按照预期的性能目标进行。

## 2.2 ModelSim的基本使用

### 2.2.1 ModelSim的界面介绍

ModelSim是一款广泛应用于硬件设计验证的仿真工具,支持多种硬件描述语言的仿真。它的界面通常包括项目浏览器、源代码编辑器、仿真控制器、波形查看器、控制台和命令行窗口等部分。

项目浏览器列出了项目中所有的文件和模块,用户可以通过它快速浏览和切换不同设计单元。源代码编辑器则用于编写和编辑设计文件,通常支持代码高亮和语法检查等功能。仿真控制器用于启动和控制仿真流程,可以设置断点、进行单步执行等。波形查看器则提供了图形化的时序波形,便于观察和分析仿真结果。

### 2.2.2 编译和仿真流程

ModelSim的编译和仿真流程相对直观。首先需要进行设计文件的编译,这通常涉及到在仿真环境中为设计文件生成仿真模型。编译过程可以通过命令行输入编译指令,如`vlog`对于Verilog文件和`vcom`对于VHDL文件,或者通过图形化界面进行。

编译完成后,可以进行仿真。仿真一般包括设计模块的实例化、测试平台(Testbench)的编写以及仿真运行。测试平台是模拟设计工作环境的关键组件,通过编写测试平台,可以向设计模块发送激励信号,并收集输出信号进行分析。在仿真过程中,用户可以在波形查看器中监控信号的变化,分析设计的行为是否符合预期。

## 2.3 Vivado与ModelSim的集成

### 2.3.1 集成流程概述

Vivado与ModelSim的集成是通过Vivado的仿真功能实现的,允许用户在Vivado界面内部启动ModelSim的仿真环境。集成流程大致可分为以下步骤:

1. 在Vivado中创建项目,确保项目中包含了需要仿真验证的设计文件。

2. 在项目设置中指定ModelSim作为仿真工具。

3. 编写设计的测试平台(Testbench)。

4. 运行仿真,Vivado会自动调用ModelSim环境进行仿真,并捕获仿真结果。

5. 在Vivado中查看和分析仿真结果,根据需要进行设计修改和迭代。

### 2.3.2 集成中的常见问题及解决方案

在进行Vivado与ModelSim的集成仿真时,可能会遇到一些常见问题,例如仿真环境配置不正确、仿真运行错误或波形查看不准确等。解决这些问题需要从以下几个方面着手:

- 确保仿真工具配置正确,Vivado版本和ModelSim版本应兼容。

- 检查设计文件的语法错误,确保所有源文件都能正确编译。

- 检查测试平台代码,确保激励信号正确无误,并且能够模拟真实的工作环境。

- 如果波形查看器出现问题,可以尝试清理仿真数据或重新编译项目。

- 在Vivado中查看仿真日志,分析报错信息,针对具体错误进行修正。

通过上述的流程与解决方案,可以有效地利用Vivado和ModelSim进行协同仿真,提高硬件设计的效率和质量。

# 3. 协同仿真中的关键技巧

协同仿真是一种高效的设计验证手段,它结合了Vivado和ModelSim的优点,为FPGA开发人员提供了强大的设计验证平台。在本章中,我们将深入探讨在进行协同仿真时需要掌握的一些关键技巧。

## 3.1 设计模块化与封装

### 3.1.1 设计模块化的理论基础

模块化是将复杂系统分解为独立模块的过程,每个模块都具有明确的接口和功能。在数字设计中,模块化有助于提高代码的可维护性、可重用性和可读性。模块化设计的概念在硬件描述语言(HDL)中通过封装实现,允许设计者隐藏模块的内部实现细节,而只暴露有限的接口。

### 3.1.2 封装与接口定义实践

在Vivado中,封装通常是指创建一个具有端口定义的模块,这些端口作为模块与其他部分通信的接口。接口定义是HDL编码的重要部分,它确保了模块间正确的数据和控制信号传输。

```vhdl

-- VHDL 代码示例

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity example_module is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

data_in : in STD_LOGIC_VECTOR(7 downto 0);

data_out : out STD_LOGIC_VECTOR(7 downto 0));

end example_module;

architecture Behavioral of example_module is

begin

-- 模块内部逻辑

end Behavioral;

```

在上述VHDL代码中,`example_module` 通过其端口 `clk`, `rst`, `data_in`, 和 `data_out` 进行了封装。在ModelSim中,这些端口可以在仿真时被驱动和监视。

## 3.2 测试平台的建立与管理

### 3.2.1 测试平台的结构与作用

测试平台(Testbench)是设计验证中不可或缺的组件,它提供了一个无需实际硬件环境即可测试设计模块的环境。测试平台可以生成测试向量,驱动被测模块的输入信号,并监视输出信号以验证设计的正确性。

### 3.2.2 创建和管理测试用例

在协同仿真中,创建和管理测试用例是测试平台的核心任务。测试用例应包括各种可能的输入条件和预期的输出结果。管理测试用例通常需要编写脚本或者使用仿真工具提供的功能来自动化测试流程。

```verilog

// Verilog 代码示例

module testbench;

// 测试信号声明

reg clk;

reg rst;

reg [7:0] data_in;

wire [7:0] data_out;

// 实例化被测模块

example_module uut (

.clk(clk),

.rst(rst),

.data_in(data_in),

.data_out(data_out)

);

// 初始化和测试序列

initial begin

// 初始化测试信号

clk = 0;

rst = 1;

data_in = 0;

#10;

// 释放复位信号

rst = 0;

#10;

// 进行一系列的输入操作并监视输出

// ...

end

endmodule

```

## 3.3 波形分析与调试技巧

### 3.3.1 Vivado波形查看器

Vivado波形查看器提供了一种图形化的方式观察仿真过程中信号的变化。这不仅使得信号之间的相互关系更直观,而且便于识别和定位设计中的错误。

### 3.3.2 ModelSim波形分析方法

ModelSim同样提供波形分析工具,允许设计者深入探究仿真的细节。通过ModelSim,用户可以设置断点,监视和记录信号值,以及执行波形的前向和后向导航,这些都是调试过程中非常有用的技巧。

本章节介绍了协同仿真中一些关键的技巧,包括设计的模块化与封装,测试平台的建立与管理,以及波形分析与调试技巧。掌握这些技巧对于提高FPGA设计的验证效率和设计质量至关重要。在下一章中,我们将进一步探讨仿真优化与高级应用,这些内容将帮助读者提升协同仿真工作的效率和水平。

# 4. 仿真优化与高级应用

## 4.1 仿真时间与资源管理

### 4.1.1 时间和资源优化策略

在FPGA设计的仿真阶段,时间与资源的管理是确保高效率仿真的关键。时间资源优化策略通常包括减少不必要的仿真细节、采用更高效的仿真算法以及利用多核处理器的优势来并行处理仿真任务。

对于减少不必要的仿真细节,可以通过修改测试激励,仅模拟实际需要的场景,跳过或简化一些不关键的行为。比如,在仿真一个接收器模块时,可以假设输入数据是正确的,而不需要仿真所有可能的错误情况。

采用高效的仿真算法,例如,对于某些特定的测试,使用更快的仿真模型代替完整的硬件描述模型。例如,可以使用参数化的宏模型来代替复杂的数学运算模型以提高仿真速度。

多核处理器的使用能够显著提高仿真执行的效率。现代仿真工具通常提供了并行仿真的支持,允许设计者将任务分布到多个核上执行。例如,可以将一个庞大的测试套件分配到不同的核上,从而加速整个测试过程。

### 4.1.2 性能瓶颈的诊断与解决

在仿真过程中,性能瓶颈的诊断与解决是一个持续的优化过程。首先,需要识别瓶颈所在。性能分析工具可以帮助我们理解仿真过程中的资源消耗情况和瓶颈问题。常见的性能瓶颈包括处理器资源、内存使用、磁盘I/O等。

一旦确定了瓶颈,接下来需要采取相应的策略来解决。例如,如果瓶颈是CPU资源,可能需要重新审视测试用例,优化仿真代码,或者使用更快的硬件来执行仿真。如果内存是一个问题,可以考虑优化数据结构,避免不必要的数据存储,或者增加系统内存。

## 4.2 高级测试技术的应用

### 4.2.1 随机化测试和覆盖率分析

随机化测试通过在测试中引入随机数据来提高测试的全面性。这种方法能够覆盖到那些在传统测试中可能被忽略的边缘情况。在Vivado和ModelSim协同仿真中,可以通过设置随机种子或者使用专门的随机化测试工具来生成测试激励。

覆盖率分析是评估测试完整性的重要工具。它可以帮助设计者了解测试是否覆盖了设计的所有功能,以及哪些功能还未被测试到。在Vivado中,覆盖率工具可以和仿真工具集成,自动收集和报告代码覆盖数据。通过查看这些数据,设计者可以调整测试用例以提高覆盖率。

### 4.2.2 边界条件测试与故障注入

边界条件测试专注于验证设计在极端情况下的行为,这对于确保设计的健壮性至关重要。它涉及到测试设计在输入值达到边界或者超出预期范围时的行为。在仿真中,可以通过手动编写测试用例来实现边界条件测试,也可以使用自动化工具来生成这些条件。

故障注入是指在测试过程中故意引入故障来验证设计的容错能力。这可以是在仿真中模拟硬件故障,比如时钟域交叉问题、信号干扰等。在Vivado中,可以使用内置的故障注入功能来模拟这些故障,并观察设计的响应。

## 4.3 多核仿真与并行测试

### 4.3.1 多核仿真的优势与实现

现代的仿真工具,如ModelSim,已经支持多核仿真,这允许同时在多个核心上执行仿真任务,极大地缩短了仿真时间。多核仿真的优势在于它能够在不牺牲测试质量的情况下加速仿真过程。

实现多核仿真通常只需在仿真工具中启用相应的选项。然而,为了充分利用多核的优势,需要对测试用例进行优化。一些测试用例可能需要被分解成更小的、可以并行执行的部分。这可能需要额外的配置工作,但一旦完成,将显著提高仿真效率。

### 4.3.2 并行测试框架与应用案例

并行测试框架是支持多核仿真的软件环境。它提供了必要的接口和管理工具来分配任务、同步进程以及收集和整理测试结果。在Vivado环境中,可以使用内置的并行测试功能,或者集成第三方的并行测试框架来实现更加复杂的测试需求。

在实际应用案例中,例如,对于一个大型FPGA设计的系统级仿真,可以将不同的子系统或模块分配给不同的核心进行测试。并行测试框架将确保这些模块的仿真在正确的时序和依赖关系中执行,而最终结果能够被正确地收集和分析。

```mermaid

graph LR

A[开始并行测试] --> B[分配任务给核心1]

A --> C[分配任务给核心2]

A --> D[分配任务给核心N]

B --> E[执行核心1的测试任务]

C --> F[执行核心2的测试任务]

D --> G[执行核心N的测试任务]

E --> H[收集核心1的结果]

F --> I[收集核心2的结果]

G --> J[收集核心N的结果]

H --> K[整理结果]

I --> K

J --> K

K --> L[结束并行测试]

```

并行测试框架将每个核心的测试结果汇总起来,以确保测试的完整性。最终,通过并行测试可以显著减少仿真时间,提高开发效率,并为快速迭代和优化提供支持。

# 5. 实战案例分析

在这一章节,我们将通过具体的实战案例来探讨如何运用Vivado和ModelSim进行FPGA项目的开发,以及如何通过协同仿真来提升设计的可靠性和性能。

## 5.1 FPGA项目实战流程解析

### 5.1.1 从设计到仿真全流程

FPGA项目开发是一个从设计到实现的完整过程。本小节将带领读者全面了解整个流程。

在设计阶段,首先要根据项目需求定义硬件功能,使用硬件描述语言(HDL)如Verilog或VHDL编写设计代码。这一阶段,可采用模块化设计来提高代码的复用性和可读性。

代码编写完毕后,需要进行初步的语法检查,这可以通过Vivado的HDL综合预览功能实现。通过检查后,可以将设计代码导入到Vivado中。

接下来,是功能仿真阶段,此时使用ModelSim作为仿真工具。在ModelSim中,我们首先对各个模块进行单独测试,确保它们的正确性,然后进行模块间的交互测试,最后进行整个系统的集成测试。

仿真阶段之后,设计需要进行综合。Vivado的综合工具能够将HDL代码转换成FPGA的逻辑元素,这一过程中还会进行优化来满足时序要求。

通过综合和优化后,生成的网表文件可以用于实现,即在FPGA上进行布局和布线(Place & Route, P&R)。完成P&R后,我们得到了可用于FPGA的比特流文件。

比特流文件下载到FPGA之后,就可以在实际硬件上进行测试,验证功能是否符合预期。

### 5.1.2 常见问题案例分析

在实际操作过程中,可能会遇到各种问题,以下是一些常见问题及应对策略:

- **综合时序问题**:通过调整约束文件来解决,或者修改设计以降低复杂度。

- **仿真与实际硬件不符**:可能因为仿真时的模型不准确,需要检查仿真激励和测试环境。

- **资源利用率过高**:可能需要优化设计,如减少逻辑单元使用或者更改设计结构。

## 5.2 典型工程案例的协同仿真

### 5.2.1 IP核的仿真与验证

IP核是预先设计好的功能模块,可以加速整个FPGA项目的开发。IP核的仿真和验证对项目的成功至关重要。

在协同仿真中,首先需要将IP核的HDL代码加入到我们的项目中,然后进行仿真。为了确保IP核按照预期工作,通常需要使用与IP核相关的测试平台(testbench),它可以模拟IP核的工作环境。

在ModelSim中运行仿真时,应检查IP核输出和预期结果是否一致。此外,也要验证IP核的边界条件和异常行为处理。

### 5.2.2 系统级仿真案例分享

系统级仿真是对整个系统行为的模拟,包括处理器、存储器和自定义逻辑。

在系统级仿真中,我们需要使用一个高级别的测试平台,它能够描述整个系统的运行环境。可以使用高级语言(如C/C++)来编写测试用例,这在ModelSim中通过SystemC接口实现。

系统级仿真案例的关键在于验证各个模块之间交互的正确性,以及整个系统的时序是否满足设计要求。例如,在一个包含处理器的系统中,需要确保处理器指令集的正确执行,并且各外设能够正常响应。

## 5.3 专家级别的调试与性能提升

### 5.3.1 高级调试技术的应用

在复杂的设计中,高级调试技术能够帮助我们快速定位问题。Vivado提供了一个集成的调试环境,允许我们查看波形、设置断点、单步执行和查看信号状态等。

高级调试技术如波形比较(Waveform Compare, WFM COMP),可以比较不同仿真运行之间的波形差异;触发条件(Triggers)和高级时序分析(Advanced Timing Analysis)则可以用来诊断复杂的时序问题。

### 5.3.2 性能优化的深入探讨

在性能优化方面,除了硬件设计层面的优化,软件层面的优化同样重要。在仿真阶段,可以调整综合约束和优化策略,比如使用Vivado的时序驱动布局(Timing-Driven Placement)。

此外,在协同仿真中,ModelSim的X-Propagation分析可以揭示可能出现的X值问题,这是FPGA设计中的一个常见问题。通过X-Propagation分析,我们可以了解X值产生的位置,并采取措施消除不确定的逻辑状态。

在代码层面,使用专门的代码覆盖率工具来评估代码测试的充分性,确保所有的逻辑路径都已经被测试到。优化过程可能包括添加或者修改代码,来减少组合逻辑的深度,提高数据吞吐量。

性能优化的最终目标是确保系统在规定的时钟频率下稳定工作,而且资源使用率也达到最优。

0

0