高级仿真技术指南:提升Vivado与ModelSim仿真效率

发布时间: 2025-01-09 22:41:24 阅读量: 7 订阅数: 10

vivado与modelsim的联合仿真教程.pdf

# 摘要

随着集成电路设计复杂性的增加,高级仿真技术在确保设计质量方面发挥着越来越重要的作用。本文首先概述了高级仿真技术的基础知识,随后详细介绍了Vivado和ModelSim仿真工具的使用技巧、高级特性及性能优化方法。第三章和第四章分别探讨了仿真环境搭建、高级用法以及如何通过脚本自动化和环境优化来提升仿真效率。文章的最后部分展望了仿真技术的发展趋势,包括基于云计算的服务和机器学习的应用前景,以及新兴仿真工具和行业标准化的最新进展。本文旨在为设计工程师提供全面的仿真技术指南,帮助他们有效提升工作效率和设计可靠性。

# 关键字

高级仿真技术;Vivado仿真;ModelSim仿真;仿真效率;云计算;机器学习

参考资源链接:[Vivado与ModelSim联合仿真教程:设置与常见问题](https://wenku.csdn.net/doc/558d2rnpxp?spm=1055.2635.3001.10343)

# 1. 高级仿真技术概览

## 1.1 仿真技术的重要性

在现代IT领域,尤其是在集成电路(IC)设计和验证中,仿真技术发挥着至关重要的角色。它是验证设计是否符合预期的必要步骤,有效模拟硬件行为,帮助工程师在物理制造前发现和解决问题。

## 1.2 仿真技术的分类

仿真技术主要分为两大类:功能仿真和时序仿真。功能仿真着重于逻辑功能的正确性,而时序仿真则关注于信号在电路中的传播时间和时序问题。

## 1.3 高级仿真技术的应用场景

随着电子系统复杂性的增加,高级仿真技术成为了应对设计挑战的利器。它可以在系统级别、芯片级别以及FPGA实现中提供深入的分析和验证,如断言和覆盖分析、代码覆盖率等高级特性,以提高设计的可靠性和效率。

```mermaid

graph LR

A[仿真技术概览] --> B[仿真技术的重要性]

A --> C[仿真技术的分类]

A --> D[高级仿真技术的应用场景]

```

# 2. Vivado仿真基础与技巧

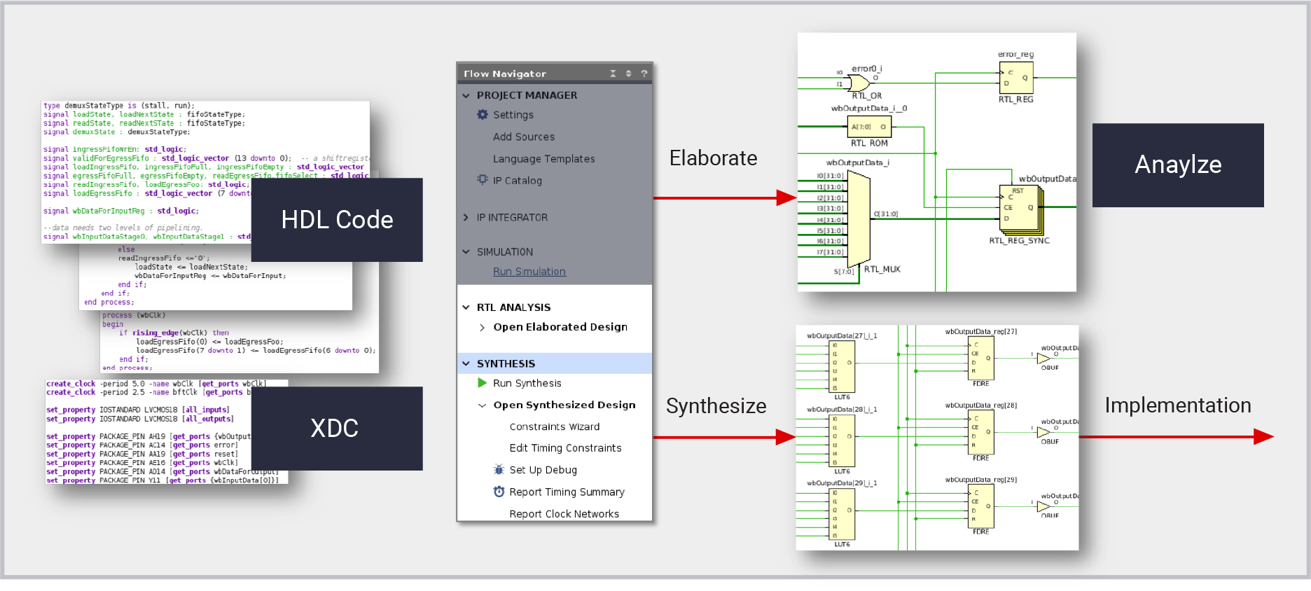

## 2.1 Vivado仿真流程详解

### 2.1.1 仿真前的准备和配置

在开始使用Vivado进行仿真之前,用户需要做一系列的准备工作。这包括安装Vivado环境,创建项目,并进行适当配置。首先,确保安装了最新版本的Vivado套件,并安装了必要的软件包和驱动程序。接下来,创建一个新项目,并指定项目的位置以及要设计的芯片型号。

在项目创建之后,用户应该添加设计文件,包括Verilog或VHDL源代码、约束文件等。配置项目包括指定目标FPGA设备、设置仿真语言标准(如IEEE 1800-2009对于SystemVerilog),以及设置仿真时间长度和分辨率。这些设置对后续的仿真测试平台编写和运行至关重要。

例如,在Vivado中配置仿真时间长度可以通过以下步骤完成:

1. 打开Vivado项目。

2. 选择“Simulation Settings”(仿真设置)。

3. 在弹出的窗口中,选择“Simulation”标签页。

4. 设置“Stop Time”(停止时间)值,例如为“1000 ns”。

5. 选择“OK”保存设置。

完成这些步骤后,Vivado将根据用户指定的时间长度进行仿真运行。

### 2.1.2 编写和运行测试平台(Testbench)

测试平台(Testbench)是仿真环境的关键组成部分,它不被映射到硬件中,用于对设计进行测试。在Vivado中,测试平台是用Verilog或VHDL编写的,并且通常包含了对设计模块输入信号的模拟,以及对输出信号的期望值的验证。

一个基本的测试平台代码示例如下:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity tb_example is

-- Testbench has no ports

end tb_example;

architecture behavior of tb_example is

-- Component declaration for the Unit Under Test (UUT)

component uut_example

Port ( input_signal : in STD_LOGIC;

output_signal : out STD_LOGIC);

end component;

--Inputs

signal input_signal : STD_LOGIC := '0';

--Outputs

signal output_signal : STD_LOGIC;

-- Instantiate the Unit Under Test (UUT)

uut: uut_example PORT MAP (

input_signal => input_signal,

output_signal => output_signal

);

-- Clock signal

signal clk : STD_LOGIC := '0';

constant clk_period : time := 10 ns;

signal stop_sim : boolean := false;

begin

-- Clock process definitions

clk_process :process

begin

while not stop_sim loop

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end loop;

wait;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

-- insert stimulus here

input_signal <= '1';

wait for 10 ns;

input_signal <= '0';

wait for 90 ns;

-- add stimulus here

-- stop simulation

stop_sim <= true;

wait;

end process;

end behavior;

```

在这个测试平台的VHDL代码中,我们定义了输入输出信号和一个时钟信号,其中时钟信号用作激励过程的计时基础。测试平台的目的是模拟输入信号并观察输出信号以验证设计是否按照预期工作。

一旦测试平台编写完成,就可以在Vivado中运行仿真了。运行仿真过程通常包括几个步骤:

1. 在Vivado中打开仿真视图。

2. 加载测试平台文件。

3. 运行仿真。

4. 检查波形窗口中的结果。

5. 分析仿真结果以确保设计的功能正确性。

## 2.2 Vivado仿真高级特性

### 2.2.1 断言和覆盖分析

在Vivado的仿真中,断言(assertions)和覆盖分析(coverage analysis)是用于验证设计正确性的高级特性。断言用于在仿真运行期间检查特定条件是否得到满足,并在条件不满足时报告错误。覆盖分析则用于收集仿真期间关于信号值、条件和代码执行路径的数据,帮助用户确保设计的所有部分都得到了充分测试。

在SystemVerilog中,断言可以通过`assert`、`assume`、`cover`等关键字来定义。以下是一个简单的断言例子:

```systemverilog

module tb_assertion;

logic a, b;

always_comb begin

a = !b;

end

// Using assert to check if the value of 'a' is the inverse of 'b'

assert property (@(posedge clk) a == !b);

// If the above condition is not met, an error will be reported during simulation.

endmodule

```

在这段代码中,我们断言在每一个时钟上升沿,`a`的值必须是`b`的逻辑非。如果不满足这个条件,Vivado仿真器会报告一个错误。

覆盖分析可以是表达式覆盖、跳转覆盖或条件覆盖,它们帮助开发者了解哪些代码路径被执行,哪些信号值被测试。覆盖分析可以使用SystemVerilog的`cover`属性来实现:

```systemverilog

module tb_coverage;

logic [3:0] counter;

// Cover the counter value reaches a certain value

cover property (@(posedge clk) (counter == 4'b1010));

endmodule

```

这个例子中的覆盖属性用来检查计数器`counter`是否在某一时间点等于4'b1010。如果仿真运行期间计数器达到了这个值,相应的覆盖率报告将会被更新。

断言和覆盖分析是Vivado仿真中非常有用的工具,因为它们可以提高测试的自动化水平,帮助开发者快速发现设计中的问题,并确保所有关键功能都得到了全面的测试。

## 2.2.2 波形和数据的可视化

在Vivado的仿真过程中,波形和数据的可视化是非常重要的,因为它允许工程师以图形化的方式检查和分析信号的行为。

0

0