【Quartus 2项目实战教程】:从设计到实现,掌握全流程操作

发布时间: 2025-01-04 12:08:31 阅读量: 14 订阅数: 11

FPGA设计实战训练参考VERILOG例程quartus工程源代码50例合集

# 摘要

本文详细介绍了使用Quartus 2软件进行VHDL设计的流程,从项目准备、环境搭建到设计实施和优化,以及最终的案例分析。首先概述了Quartus 2的基础知识和项目准备的步骤,然后深入到VHDL设计的每一个阶段,包括设计输入、仿真测试、综合、器件适配、实现、硬件验证以及性能优化。文章特别强调了高级设计技巧和模块化设计的重要性,并探讨了设计安全性与可靠性的问题。最后,通过两个实战案例,展示了Quartus 2在数字逻辑设计和复杂系统设计中的应用,为读者提供了实际操作的参考。

# 关键字

Quartus 2;VHDL设计;硬件验证;性能优化;模块化设计;案例分析

参考资源链接:[Quartus 2 RS、D、JK、T、触发器实验报告

D触发器构成二分频、四分频电路

](https://wenku.csdn.net/doc/6401ace6cce7214c316ed8fa?spm=1055.2635.3001.10343)

# 1. Quartus 2概述及项目准备

## 1.1 Quartus 2简介

Quartus II 是一款由Altera公司开发的综合性FPGA/CPLD设计软件,它提供从设计输入到硬件配置的全套解决方案。Quartus II支持多种设计输入方法,如VHDL、Verilog HDL和原理图,使得设计者可以根据自己的习惯选择最方便的设计方法。

## 1.2 项目准备

项目准备工作是确保设计顺利进行的重要步骤,包括明确设计目标、收集需求、选择合适的FPGA器件以及熟悉Quartus II开发环境。项目准备工作还涉及配置开发环境,例如设置项目路径、选择FPGA型号和配置Quartus II项目参数等,确保后续设计工作的顺利进行。

## 1.3 设计流程概览

设计流程通常包括设计输入、编译、仿真、综合、适配、布局布线、下载和硬件测试等阶段。对于一个初学者来说,掌握这些基本流程对于理解整个FPGA设计至关重要。接下来的章节将会对每个步骤进行深入的讲解和操作演示。

# 2. VHDL设计基础与Quartus 2环境搭建

### 2.1 VHDL基础知识

#### 2.1.1 VHDL语言简介

VHDL(VHSIC Hardware Description Language)是一种用于描述电子系统硬件功能、结构和行为的硬件描述语言。它起源于1980年代的VHSIC(Very High Speed Integrated Circuit)项目,是一种标准的电子系统设计语言,被广泛应用于数字电路设计领域。

VHDL具备以下特点:

- **平台无关性**:VHDL代码可以在不同的硬件平台和制造商之间移植,使得设计者可以专注于设计本身,而不受限于具体硬件。

- **模块化设计**:VHDL支持模块化设计,有利于复杂系统的设计和管理,通过模块复用能够提高设计效率。

- **并行处理能力**:VHDL自然支持并行处理,这对于描述数字逻辑电路而言是非常自然的。

#### 2.1.2 VHDL基本语法

VHDL代码主要由以下三部分构成:

- **实体声明**(Entity):定义了电路的外部接口,包括输入、输出和双向信号。

- **架构声明**(Architecture):描述了实体内部的逻辑功能实现。

- **库引用和配置声明**(Library and Configuration):用于引用VHDL标准库和其他库中的组件,以及配置实体与架构之间的关系。

一个简单的VHDL实体声明如下:

```vhdl

entity my_entity is

port(

a : in std_logic; -- 输入信号

b : in std_logic;

c : out std_logic -- 输出信号

);

end entity my_entity;

```

架构声明可能如下:

```vhdl

architecture my_architecture of my_entity is

begin

-- 实现逻辑描述

c <= a and b;

end architecture my_architecture;

```

在这段代码中,我们定义了一个简单的逻辑门电路,该电路接收两个输入信号`a`和`b`,输出它们的逻辑与(AND)结果。

### 2.2 Quartus 2软件安装与界面熟悉

#### 2.2.1 Quartus 2软件安装步骤

Quartus II是Altera公司(现为英特尔旗下)开发的一款FPGA/CPLD设计软件,广泛用于逻辑设计、仿真、编程和调试。Quartus II提供了从设计输入、综合、仿真到设备编程的全套工具。

安装Quartus II软件的步骤通常包括:

1. 下载安装包:访问官方下载页面获取安装文件。

2. 运行安装向导:解压缩安装包后,双击运行`setup.exe`。

3. 选择安装组件:根据需要选择安装的组件,如Quartus II软件、ModelSim仿真工具等。

4. 完成安装:按照安装向导提示完成安装并重启计算机。

请注意,安装过程中需要合适的硬件配置和有效的软件许可。

#### 2.2.2 Quartus 2主要界面介绍

Quartus II的用户界面包含了设计工作区、工具栏、菜单栏等,用户可以通过这些工具进行项目创建、编辑、编译、仿真、下载等操作。

- **项目导航器**:用于管理项目文件、查看文件依赖关系和组织层次。

- **编辑器窗口**:编写HDL代码、图形设计和其他文本文件。

- **编译器**:对设计进行编译、综合、适配,并提供编译报告。

- **仿真工具**:进行设计的仿真测试,验证功能正确性。

- **分析仪**:包括时序分析器、资源消耗分析器等。

### 2.3 设计项目的新建与管理

#### 2.3.1 创建新项目

在Quartus II中创建一个新项目需要以下步骤:

1. 打开Quartus II软件,选择“File” -> “New Project Wizard”开始创建新项目。

2. 按照向导提示输入项目名称、位置及目标设备信息。

3. 添加设计文件,比如VHDL、Verilog代码或图形设计文件。

4. 完成向导,并生成项目框架。

创建项目后,Quartus II将自动打开项目导航器,其中包含一个空的项目目录。

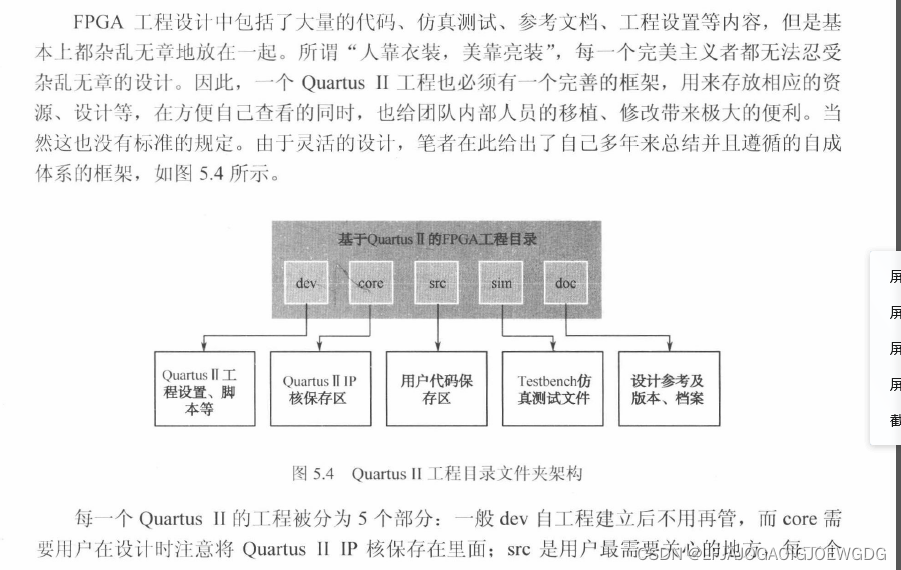

#### 2.3.2 项目文件结构和管理

项目文件结构和管理是高效使用Quartus II软件的重要部分。项目目录通常包含以下内容:

- **QPF(Quartus Project File)**:项目的配置文件,包含项目设置。

- **QSF(Quartus Settings File)**:文件包含特定于项目的所有设置和命令。

- **源代码文件**:存储为HDL代码或图形设计文件。

- **仿真文件**:用于验证设计功能的测试平台代码。

- **编译报告**:编译后的报告文件,提供了有关设计综合和适配的详细信息。

管理项目文件通常涉及添加、删除、重命名文件,以及配置文件依赖关系。通过项目导航器可以方便地执行这些操作,并对项目文件结构进行可视化管理。

以上内容是VHDL设计基础与Quartus 2环境搭建的详细介绍,接下来我们将进入下一章节,深入讨论VHDL设计流程与Quartus 2项目实施的细节。

# 3. VHDL设计流程与Quartus 2项目实施

## 3.1 设计输入与仿真测试

### 3.1.1 编写VHDL设计代码

VHDL(VHSIC Hardware Description Language)是一种用于描述数字和混合信号系统行为和结构的硬件描述语言。它是电子系统级设计的基石,允许设计师以文本方式描述硬件功能。在Quartus II软件中,VHDL设计的编写通常涉及以下步骤:

1. 创建一个新的VHDL源文件,并为其提供一个合适的文件名,以反映文件的内容。

2. 定义实体(entity),这是设计的接口,指定了模块的输入和输出信号。

3. 构造架构(architecture),这是设计的主体,它描述了实体行为的具体实现。

4. 实现功能逻辑,这通常涉及到条件语句(如if-then-else)、进程(process)等高级VHDL语言特性。

5. 对代码进行编译,确保没有语法错误。

例如,一个简单的VHDL设计代码如下:

```vhdl

library ieee;

use ieee.std_logic_1164.all;

entity simple_dff is

Port ( clk : in std_logic;

d : in std_logic;

q : out std_logic);

end simple_dff;

architecture Behavioral of simple_dff is

begin

process(clk)

begin

if rising_edge(clk) then

q <= d;

end

```

0

0