【数字逻辑实验深度分析】:D触发器分频电路构建的关键策略

D触发器二分频电路图

摘要

本文深入探讨了数字逻辑实验的核心内容,重点关注了D触发器的工作原理及其在分频电路中的应用。通过对D触发器的基本概念、时序特性和电路实现的系统分析,本文揭示了其在同步和可预置分频器设计中的关键作用。同时,文章还详述了分频电路的设计要点,包括工作模式、稳定性要求及优化策略,并通过实验项目实践,展示了分频电路搭建、测试与分析的过程。最后,本文展望了数字逻辑实验的发展趋势和创新设计,强调了软件仿真和非传统技术在实验创新中的重要性,并讨论了解决实验中挑战的策略。

关键字

数字逻辑实验;D触发器;分频电路;同步分频;可预置分频;电路优化

参考资源链接:Quartus 2 RS、D、JK、T、触发器实验报告 D触发器构成二分频、四分频电路

1. 数字逻辑实验概述

数字逻辑实验的重要性

在现代信息技术飞速发展的今天,数字逻辑实验已经成为IT和电子工程专业教育中不可或缺的一部分。数字逻辑实验不仅仅是理论知识的简单应用,更是培养学生实际操作能力、分析和解决实际问题能力的关键环节。通过这些实验,学生可以更好地理解数字系统的基本概念,掌握数字电路设计、仿真和测试的技能,从而为将来的职业道路打下坚实的基础。

实验的目标与要求

数字逻辑实验的目的在于通过实践操作来加深对数字电路理论知识的理解,学会使用现代电子设计工具进行电路设计和仿真,并能独立搭建电路,对其进行测试和分析。对于5年以上的IT从业者,这些实验同样具有启发性,可以通过实验来更新自己的专业知识,了解新兴技术和工具,解决实际工作中的复杂问题。

实验的主要内容

数字逻辑实验的内容包括了多个方面,从基础的逻辑门电路到复杂的时序逻辑电路,包括触发器、计数器、分频器等。此外,实验还涉及电路的仿真分析、性能测试和故障诊断等内容。通过这些实验,参与者不仅可以学习到电路设计的基本方法,还可以锻炼自己的创新思维和问题解决能力。

2. D触发器的工作原理

2.1 D触发器的基本概念

2.1.1 D触发器的定义

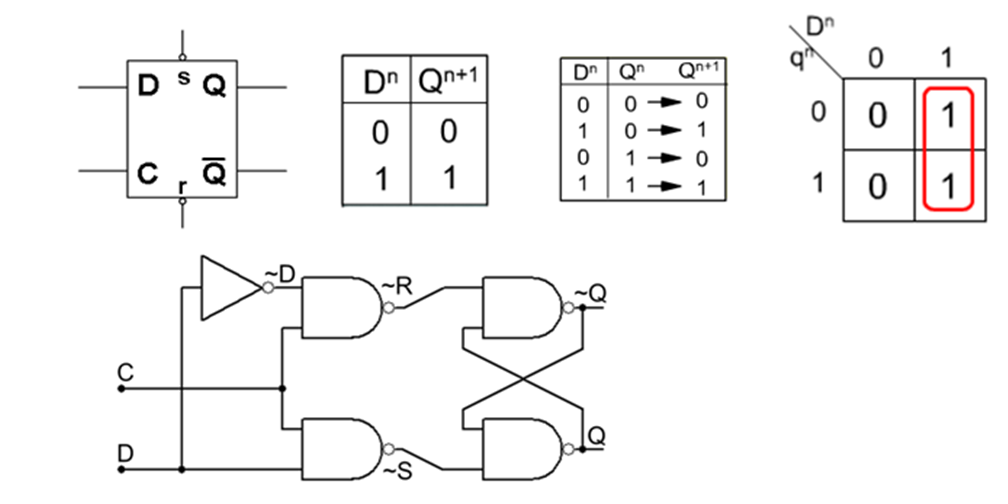

D触发器(D Flip-Flop)是数字电路中常见的存储单元之一,主要用于存储一位二进制信息。其核心是一个开关机制,允许在特定的时钟边沿触发下,输入的数据(D)被存储并反映到输出(Q)。D触发器是实现同步逻辑系统的基础组件,广泛应用于各种数字设备,比如计数器、寄存器、存储器等。

在内部结构上,D触发器可以看作是由两个或多个门电路构成的环形结构,其中包括至少一个反馈回路。这一结构允许它在触发时刻捕获输入信号,并在下一个触发信号到来之前保持该状态。

2.1.2 D触发器的逻辑功能

D触发器的行为符合“数据锁存”的逻辑功能,即“在时钟信号的上升沿或下降沿,D端的数据被锁存到Q输出端”。D触发器有一个时钟输入端(CLK),当CLK产生有效的边沿时,D输入端的数据状态会复制到Q输出端。

D触发器具有两个稳定状态(置0或置1),并且可以在时钟信号控制下从一个状态稳定地转移到另一个状态。这个特性使得D触发器可以用于同步数字系统,确保数据的可靠传输和处理。

2.2 D触发器的时序特性

2.2.1 时钟边沿触发

D触发器的触发是通过时钟信号的边沿实现的,通常有上升沿触发和下降沿触发两种类型。上升沿触发意味着在时钟信号从低电平跳变到高电平时,D触发器的状态会更新;而下降沿触发则是在时钟信号从高电平跳变到低电平时更新状态。

触发边沿的选择取决于设计需求,上升沿触发更常用。选择合适的触发边沿是同步电路设计中的一个关键因素,它影响到整个系统的时间行为。

2.2.2 状态稳定性和传播延迟

状态稳定性是指D触发器在锁存数据后,能保持输出状态不变,直到下一个有效触发边沿到来。此特性对于设计稳定可靠的同步系统至关重要。

传播延迟(Propagation Delay)是指D信号输入到Q输出之间的时间差。延迟时间过长可能导致系统时序问题,因此在设计时,工程师需要确保触发器的传播延迟在整个电路中是可接受的。

2.3 D触发器的电路实现

2.3.1 逻辑门级联实现

从基础的逻辑门电路出发,D触发器可以由若干个与门、或门、非门等逻辑门电路级联组成。这种实现方式有助于理解触发器内部的工作原理,但是由于级联电路的复杂性,它在实际应用中可能会因为过多的延迟而变得不可靠。

级联实现的基本思路是使用两个锁存器,一个用来捕获数据(主锁存器),另一个用来稳定输出(输出锁存器)。两个锁存器交替工作,在一个时钟周期内,一个捕获数据,另一个稳定输出。

2.3.2 使用集成电路实现

在现代数字电路设计中,D触发器通常由专用的集成电路(IC)实现。使用IC的D触发器模块,不仅可以简化电路设计,还能提供更好的稳定性和性能。常见的D触发器IC包括74HC74、74LS74等型号。

集成电路实现的D触发器通常拥有更短的传播延迟,以及更高的工作频率和稳定性。此外,它们还可以集成其他功能,如置位、复位、使能等,以满足更复杂的电路设计需求。

在实际应用中,设计者会根据需求选择合适的IC型号,并参考数据手册来正确连接和配置触发器。以下是一个简单的D触发器的电路连接示例代码:

- module d_flip_flop(

- input clk, // 时钟信号

- input rst_n, // 异步复位信号,低电平有效

- input d, // 数据输入端

- output reg q // 数据输出端

- );

- always @(posedge clk or negedge rst_n) begin

- if (!rst_n) begin

- q <= 1'b0; // 异步复位,输出置零

- end else begin

- q <= d; // 在时钟上升沿更新输出

- end

- end

- endmodule

在上述Verilog代码中,always块是敏感于时钟上升沿以及复位信号的下降沿。当复位信号为低电平时,无论时钟信号的状态如何,输出都会被置为0;当复位信号无效且时钟上升沿到来时,D端的数据会被传递到Q端。

以上是对D触发器工作原理的深入探讨,通过基础知识、时序特性和电路实现的介绍,我们可以全面理解这一基础数字组件的工作机制。在后续章节中,我们将探讨D触发器如何应用于分频电路设计中。

3. 分频电路的基本原理

在数字电路设计领域中,分频电路是一种至关重要的组