同步加法计数器深度解析:如何解决设计中的常见问题?

发布时间: 2024-12-18 19:48:15 阅读量: 2 订阅数: 4

Python项目-自动办公-56 Word_docx_格式套用.zip

# 摘要

同步加法计数器是数字电路设计中的关键组件,具有广泛的应用范围,如时钟同步和数据总线控制。本文全面介绍了同步加法计数器的基本概念、工作原理、设计理论和实现方法。通过分析同步与异步计数器的区别,讨论了设计中的电路选择、状态转换、时序分析以及常见的设计问题和解决策略。文章还提供了同步加法计数器的编程实现实例,包括基于FPGA和微控制器的方法,并对其实践应用进行了深入探讨。此外,本文探讨了同步加法计数器的高级特性和优化技术,以实现功耗降低和性能提升。最后,文章展望了计数器设计的未来挑战和发展趋势,特别是新材料技术、计数器架构创新以及量子计算和人工智能的潜在应用。

# 关键字

同步加法计数器;数字电路设计;状态转换图;时序分析;故障诊断;性能优化

参考资源链接:[数字电子课程设计:八进制同步加法计数器实现详解](https://wenku.csdn.net/doc/649d257f50e8173efdb27754?spm=1055.2635.3001.10343)

# 1. 同步加法计数器基本概念与原理

## 1.1 同步加法计数器的定义与重要性

同步加法计数器是一种数字电路,它的每个触发器(或位)的状态更改都发生在相同的时钟边沿上,因此可以进行快速的计数操作。这种计数器的设计对于现代计算机系统和其他数字设备中的时序控制至关重要。

## 1.2 计数器的基本工作原理

计数器的工作原理基于状态转移,其在接收到脉冲信号时改变内部状态,并将该状态表示为输出。基本的加法计数器会按照序列进行状态切换,从0开始,每个脉冲使计数增加1,直到达到最大计数值后回滚至0重新开始。

## 1.3 同步与异步计数器的区别

同步计数器与异步计数器的主要区别在于触发方式。同步计数器在每个时钟周期中同时更新其状态,而异步计数器则逐级传递触发信号。同步计数器可以实现更高速的计数且没有异步计数器中的延迟问题,但设计上要求所有触发器同步,这在高速计数时可能会带来挑战。

# 2. 同步加法计数器的设计与实现

## 2.1 同步加法计数器的设计理论

### 2.1.1 计数器的工作原理

计数器是数字电路中重要的组成部分,它的核心功能是记录输入脉冲的个数。同步加法计数器利用触发器在每个时钟脉冲到来时改变状态,以实现计数的功能。每个触发器代表一个二进制位,它们共同组成了计数器的状态机,能够以二进制形式存储和增加数值。在同步加法计数器中,所有的触发器都连接到同一个时钟信号,因此在时钟脉冲的上升沿或下降沿(取决于触发器的类型),所有的触发器会同时改变状态。

### 2.1.2 同步与异步计数器的区别

同步计数器和异步计数器的主要区别在于触发器状态变化的方式。在同步计数器中,所有的触发器都是同步变化的,这意味着计数的增加发生在同一时间点。这种设计使得同步计数器在速度上快于异步计数器,因为它消除了在触发器之间的延迟。异步计数器,又称为串行计数器,每个触发器的状态变化取决于前一个触发器的变化,这导致了整个计数过程的延迟。

## 2.2 同步加法计数器的电路设计

### 2.2.1 逻辑门与触发器的选择

在设计同步加法计数器时,触发器是实现同步状态变化的核心部件。最常见的触发器有D触发器、T触发器、JK触发器和SR触发器。对于同步加法计数器,JK触发器由于其灵活的特性,即 JK 触发器的输出取决于 J 和 K 输入端的状态,因此它们在设计中被广泛应用。JK触发器能够通过输入端的适当配置,实现计数器的进位功能。

### 2.2.2 状态转换图的绘制

状态转换图是设计同步加法计数器的重要工具,它表示了计数器在不同状态之间的转换。例如,一个4位的同步加法计数器会有16个状态,从0000到1111。状态转换图将这些状态以节点的形式表示,并通过箭头指示触发器状态转换的路径。这个图需要详细标注每个状态转换时触发器的输入条件,确保计数器能够正确地计数。

### 2.2.3 电路图的绘制与实现

绘制电路图是将理论设计转换为实际电路的过程。这一步需要将选定的触发器和逻辑门以图示方式表达出来,展现它们是如何连接以及如何协同工作的。电路图中的每个连接和元件都应标注清楚,并应包含必要的信号名称和逻辑关系说明。设计过程中,需要考虑如电源、地线、时钟信号、数据输入输出等各个部分,并确保电路设计符合预期的计数范围和功能要求。

## 2.3 同步加法计数器设计中的常见问题及解决方法

### 2.3.1 竞态条件与消除策略

在同步计数器的设计中,由于多个触发器几乎同时改变状态,可能会出现竞态条件。竞态条件是由信号的传播延迟引起的,可能导致触发器在不应该变化的时候发生变化。解决这一问题通常需要在电路设计中引入适当的时序控制措施。例如,确保时钟信号到达所有的触发器几乎是同时的,或者设计电路时引入额外的逻辑门延迟,来确保信号在改变状态前具备足够的稳定时间。

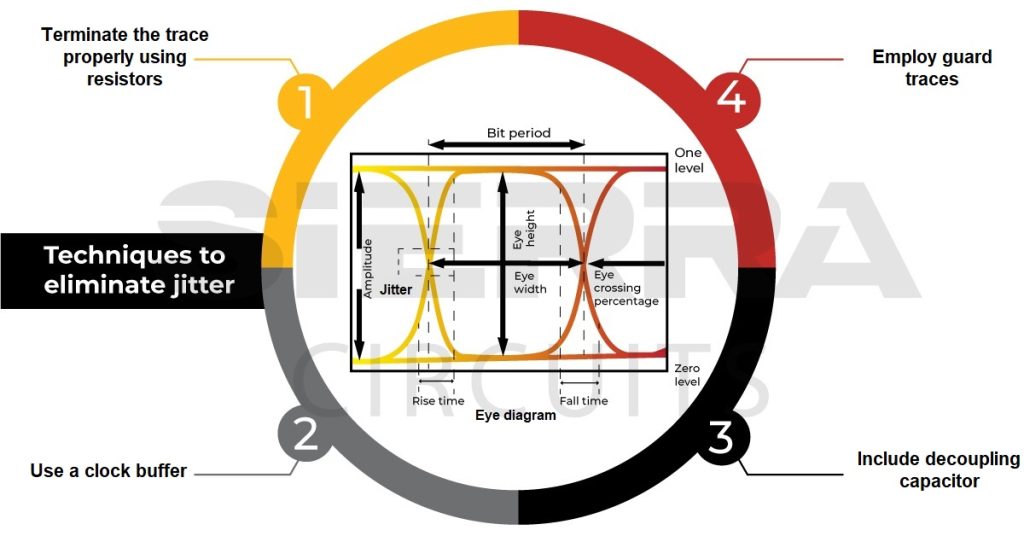

### 2.3.2 防抖动机制的设计

在计数器的设计中,尤其是在由外部事件触发计数的场景下,防抖动机制非常关键。防抖动机制能保证输入信号的稳定,避免因为机械开关或传感器带来的短暂、不稳定的信号导致计数错误。实现防抖动的常见方法包括使用RC电路、施密特触发器或软件算法等。这些方法可以有效地过滤掉噪声信号,确保计数器在稳定的信号上进行计数。

### 2.3.3 同步设计的时序分析

同步设计的时序分析是确保计数器正确工作的关键步骤。这包括分析时钟信号的边缘特性、触发器的设定和保持时间、以及信号在电路中的传输时间。时序分析一般使用专业工具来完成,它能帮助工程师发现潜在的问题,如时钟偏移、信号延迟等,并采取措施解决这些问题。在设计时序时,工程师需要确保计数器在最坏情况下仍能满足时序要求。

通过本章节的介绍,我们详细探讨了同步加法计数器设计的理论基础、电路实现方法以及解决设计中常见问题的策略。下一章节将重点介绍同步加法计数器在实际应用中的实现与实践应用。

# 3. 同步加法计数器的实践应用

同步加法计数器不仅在理论上具有重要的地位,在实际的数字系统设计中同样扮演着不可或缺的角色。本章节将深入探讨同步加法计数器在数字系统中的应用,提供实际编程实例,并涉及故障诊断与测试的相关内容。

## 3.1 同步加法计数器在数字系统中的应用

### 3.1.1 计数器在时钟同步中的作用

在数字系统设计中,时钟同步是一个重要的话题,它确保了系统内各个部分的时序一致。同步加法计数器在这一过程中起到了关键作用。通过计数器来产生一个稳定的、周期性的信号,可以用于同步其他数字电路。例如,在一个处理器中,计数器可能被用来提供一个与CPU时钟同步的计数信号,以确保指令流的正确执行。

同步加法计数器通过同步时钟脉冲的驱动,确保计数值的更新与系统时钟完全同步。这种同步机制通常通过一个全局时钟信号实现,使得整个电路在每一个时钟周期都进行状态更新,这样可以有效减少由于异步操作所带来的时序不确定性和信号冲突。

```mermaid

flowchart LR

A[全局时钟信号] -->|驱动| B[同步加法计数器]

B -->|更新计数值| C[其他数字电路]

C -->|反馈| A

```

在上述流程图中,我们可以看到全局时钟信号是如何驱动同步加法计数器,并最终将同步的计数值传递到其他数字电路的。此外,计数器的状态反馈又可以用于维持时钟信号的稳定性和同步性,形成一个闭环系统。

### 3.1.2 计数器在数据总线控制中的应用

数据总线是数字系统中用于数据传输的通道,而同步加法计数器在此扮演了一个重要角色。在数据传输过程中,计数器可以用来记录传输的数据量,例如,用于确定何时启动或停止数据传输,或者在数据包传输中用于跟踪数据包的完整性。同步加法计数器能够保证这一过程的精确性和可靠性。

举个例子,当一个外设向系统内存发送数据时,同步加法计数器可以用来生成一个计数值,该值与将要发送的数据量相对应。当计数器达到预设值时,传输结束的信号被触发,通知相关部分完成数据传输,并可以准备下一个数据传输周期。

## 3.2 同步加法计数器编程实例

### 3.2.1 利用FPGA实现同步加法计数器

现场可编程门阵列(FPGA)是一种非常适合实现同步加法计数器的硬件平台。在FPGA中,计数器可以通过硬件描述语言(HDL),如Verilog或VHDL实现。

以下是利用Verilog语言实现4位同步加法计数器的代码示例:

```verilog

module sync_adder_counter(

input clk, // 时钟信号

input reset, // 复位信号

output reg [3:0] Q // 4位输出

);

always @(posedge clk or posedge reset)

begin

if(reset)

Q <= 4'b0000; // 当复位信号为高时,计数器清零

else

Q <= Q + 1'b1; // 否则在时钟上升沿增加计数器的值

end

endmodule

```

在上面的代码中,`sync_adder_c

0

0