八进制同步加法计数器设计挑战:如何确保稳定性和准确性?

发布时间: 2024-12-18 20:08:35 阅读量: 2 订阅数: 4

# 摘要

本文全面探讨了八进制同步加法计数器的原理、设计、优化及应用。首先介绍了八进制数系统的特点和同步加法计数器的工作原理,随后深入阐述了计数器稳定性与准确性的基础理论。在设计实践部分,详述了逻辑图与真值表的构建、电路元件选择与布局以及测试代码编写和模拟验证的重要性。文章还讨论了优化策略,包括电源管理、错误检测与纠正以及性能测试与调试技巧。最后,探索了八进制同步加法计数器在高级应用中的潜力和未来展望,并总结了设计中的挑战与未来研究方向。

# 关键字

八进制计数器;同步加法;稳定性;准确性;电路优化;测试与调试

参考资源链接:[数字电子课程设计:八进制同步加法计数器实现详解](https://wenku.csdn.net/doc/649d257f50e8173efdb27754?spm=1055.2635.3001.10343)

# 1. 八进制同步加法计数器概述

在现代电子系统设计中,同步加法计数器扮演着不可或缺的角色,特别是当涉及到特定数字系统或嵌入式系统时。本章将简要介绍八进制同步加法计数器的基础概念,并为后续章节的详细讨论奠定基础。

## 1.1 八进制同步加法计数器简介

同步加法计数器是一种数字电路组件,它能够对输入的脉冲信号进行计数,并根据设定的进位规则同步地增加计数值。八进制同步加法计数器专为处理八进制数系统设计,它以8为基数进行计数,从0计数到7后自动归零并产生进位。

## 1.2 计数器的同步特性

同步加法计数器之所以得名,是因为它使用同一时钟信号源来触发每一个计数单元,这意味着所有计数单元的计数动作都是同步进行的。这种设计比异步计数器有更低的延迟,更高的速度,适合于高速计数应用。

## 1.3 计数器的应用场景

八进制同步加法计数器广泛应用于需要特定进制计数的场合,比如某些类型的数字仪表、计时器,以及一些特定的通信协议实现中。随着电子系统复杂性的提升,同步加法计数器在许多高精度和高可靠性要求的场合成为首选。

通过对八进制同步加法计数器的初步了解,我们为后续章节中对其稳定性、准确性、设计实践及优化策略的深入探讨打下了基础。这有助于IT和电子行业从业者在设计相关系统时,能够更好地理解和应用这一关键技术组件。

# 2. 计数器稳定性与准确性基础理论

## 2.1 八进制数系统及其特点

### 2.1.1 八进制数的基本概念

八进制数系统是一种基数为8的数制,每一位上的数字可以是0到7之间的任何一个整数。这种数制在计算机科学中曾经非常常见,因为在早期计算机设计中,它比二进制更加紧凑,而比十进制更易于计算机处理。八进制数系统的特点是每一位的数值只用八个符号表示,这在硬件实现上相对简单,尤其是在使用了三位二进制数就能表示一个八进制数的情况下。例如,八进制中的数字"10"相当于二进制的"1000",八进制的"7"相当于二进制的"111"。

### 2.1.2 八进制与二进制的转换

在设计和分析八进制同步加法计数器时,将八进制数转换为二进制数是一个基础的技能。八进制转换为二进制的过程非常直接:每一位八进制数可以直接转换为一个三位的二进制数。具体规则如下:

- 八进制的0转换为二进制的000

- 八进制的1转换为二进制的001

- 八进制的2转换为二进制的010

- 八进制的3转换为二进制的011

- 八进制的4转换为二进制的100

- 八进制的5转换为二进制的101

- 八进制的6转换为二进制的110

- 八进制的7转换为二进制的111

反之,将二进制数转换为八进制数时,可以将二进制数每三位一组,从低位到高位进行分组,然后将每组转换成对应的八进制数字。

## 2.2 同步加法计数器的工作原理

### 2.2.1 同步加法计数器的定义

同步加法计数器是一种电子计数器,它在时钟信号的驱动下,通过同步方式完成数值的累加。与异步计数器相比,同步计数器在计数时所有触发器(Flip-Flop)的状态改变发生在同一时钟边沿,这使得其工作更为快速和稳定。在同步加法计数器中,最常用的触发器是D型触发器,因为它能够在时钟边沿捕捉输入信号并稳定地输出。

### 2.2.2 触发器在计数器中的应用

在同步加法计数器的设计中,触发器扮演着至关重要的角色。触发器在每个时钟周期的边沿到来时,根据输入信号改变其状态,从而实现计数功能。例如,一个典型的4位同步加法计数器可能包含4个D型触发器,每个触发器对应一个二进制位。这些触发器相互连接,以确保计数序列连续且同步。

触发器通常在时钟脉冲的上升沿或下降沿改变状态。在同步计数器中,计数的增加通常发生在时钟脉冲的上升沿。计数器的输出端可以是一个多路输出,每个输出连接到一个触发器的Q端,这样在每个时钟周期后,输出端就能显示出当前的计数值。

## 2.3 确保稳定性和准确性的理论依据

### 2.3.1 时钟信号的稳定性要求

为了确保同步加法计数器的稳定工作,时钟信号必须满足特定的要求。时钟信号的稳定性至关重要,因为它决定了触发器状态改变的准确性和同步性。时钟信号需要具有恒定的频率和幅度,并且应当尽可能减少噪声和抖动。

为了保证计数器在多个计数周期中的稳定性,时钟信号应具备以下几个特性:

- 精确的时钟周期和边沿定位

- 较小的周期抖动(Jitter)

- 高的电平保持时间以避免错误触发

- 高的信号上升和下降边沿速率

### 2.3.2 电路噪声与计数器准确性

电路噪声是影响计数器准确性的主要因素之一。噪声可能来源于电磁干扰、电源波动、信号耦合等多种途径,它会导致计数器中的触发器产生误操作。为了最小化电路噪声对计数器准确性的影响,设计者需要考虑:

- 使用高质量的电源和恰当的电源管理技术

- 对敏感的信号线进行屏蔽和隔离

- 使用去耦电容来稳定电源电压

- 设计合理的信号线布局,以减少信号间的串扰

在进行计数器的物理布局时,要特别注意信号线的布线长度和方向,尽量避免长线信号传输,因为长线容易引入噪声。此外,在时钟线路和敏感信号线附近避免高速信号线路,以防互相干扰。通过这些策略,可以显著提高同步加法计数器的稳定性和准确性。

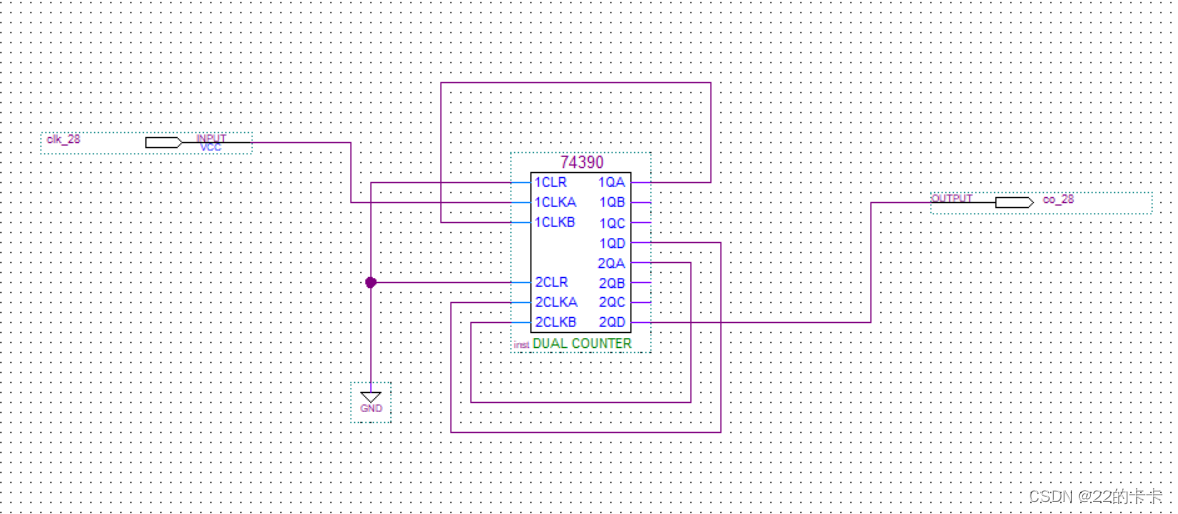

# 3. 八进制同步加法计数器设计实践

## 3.1 设计初期的逻辑图与真值表

### 3.1.1 绘制逻辑图的基本步骤

在设计八进制同步加法计数器的初始阶段,绘制逻辑图是理解整个计数器工作原理和信号流动的关键步骤。绘制逻辑图的过程可以分为以下几个步骤:

1. **确定输入输出**:首先要明确计数器的输入信号和输出信号。对于八进制计数器来说,通常输入信号包括时钟信号CLK、复位信号RESET以及其他可能的控制信号。输出信号则是计数器的三位二进制表示,因为八进制可以表示为三位二进制数。

2. **定义状态转移**:八进制同步加法计数器有八个状态,对应于0到7的十进制数。定义这些状态之间的转移逻辑是设计逻辑图的基础。

3. **选择触发器类型**:在同步计数器中,常常使用触发器(如D触发器或T触发器)来保存和转移状态。确定使用的触发器类型后,可以绘制出每个触发器的时序图,表示在时钟信号的作用下状态的变化。

4. **逻辑门电路的实现**:通过逻辑门(如与门、或门、非门等)实现状态转移的逻辑功能。这包括对计数器加一时各个触发器的输出和下一个状态的确定。

5. **电路的优化**:在完成基本的逻辑图设计后,还需要考虑电路的优化。这包括减少逻辑门的数量、提高电路的速度、降低成本等。

### 3.1.2 真值表的构建及其作

0

0