【数据链路构建】:AD7175与FPGA通信协议的高效实现

发布时间: 2025-01-10 12:22:29 阅读量: 6 订阅数: 8

通信与网络中的无线HART数据链路层设计与实现

# 摘要

本文详细介绍了AD7175与FPGA之间的通信协议及其硬件接口设计。首先概述了AD7175的基本工作原理及FPGA的应用场景和设计流程。随后,深入分析了两者通信协议的理论基础,包括信号时序、同步机制、错误检测和校正机制,以及通信协议的层级结构。在实践实现章节,本文探讨了通信协议在实际应用中的部署、软硬件实现细节及问题诊断方法。最后,对高级通信技术的应用和通信协议的可扩展性进行了展望。通过这一系列探讨,本论文旨在提供一个关于如何有效利用AD7175与FPGA进行数据通信的参考,同时为未来通信技术的发展提供理论基础和技术支持。

# 关键字

AD7175;FPGA;通信协议;硬件接口;信号时序;可扩展性

参考资源链接:[FPGA实现AD7175多路复用ADC控制逻辑Verilog代码详解](https://wenku.csdn.net/doc/4gr8x5ia3t?spm=1055.2635.3001.10343)

# 1. AD7175与FPGA通信协议概述

本章将为读者提供AD7175与FPGA通信协议的概况,为理解后续章节的内容打下坚实的基础。AD7175是一款高性能的模拟数字转换器(ADC),而FPGA(现场可编程门阵列)作为一种高性能的可编程逻辑设备,二者结合可实现复杂的数据采集和处理任务。我们将重点介绍这种通信方式在数据采集系统中的应用以及通信协议的基础知识。

## 1.1 AD7175与FPGA结合的必要性

AD7175以其高精度和低噪声特性广泛应用于多通道数据采集系统中。FPGA的并行处理能力和可编程性则为这些系统提供了灵活性和高效的信号处理能力。将AD7175与FPGA结合起来,能够满足实时数据采集、处理和传输的需求。

## 1.2 通信协议的作用与重要性

通信协议作为AD7175与FPGA之间交流的规则和标准,是确保数据准确传输的关键。在本章节中,我们将讨论这些规则如何被定义和实现,并概述它们在数据完整性、错误处理和系统稳定运行中的作用。

## 1.3 本章小结

通过本章的介绍,读者应能理解AD7175与FPGA结合的优势,以及通信协议在保证数据传输质量方面的重要性。接下来的章节将详细介绍AD7175的基本工作原理、FPGA的基础知识,以及硬件接口的连接和设计要点。

# 2. ```

# 第二章:AD7175与FPGA硬件接口基础

硬件接口是连接不同硬件组件的桥梁,确保它们能够高效、可靠地交换数据。本章节将深入探讨AD7175与FPGA的硬件接口基础,包括AD7175的工作原理和特性、FPGA的技术特点和应用场景,以及硬件接口连接与设计要点。

## 2.1 AD7175的基本工作原理与特性

AD7175是一款由Analog Devices公司生产的高精度模拟数字转换器(ADC),在工业和医疗领域有着广泛的应用。它提供了低噪声、高分辨率的模拟信号转换功能,为设计者提供了灵活的配置选项。

### 2.1.1 AD7175的功能结构与数据转换原理

AD7175具有多个通道,可以同时或单独转换输入的模拟信号。其内部结构包括多路复用器、模拟输入保护、可编程增益放大器、Σ-Δ调制器和数字滤波器。数据转换原理依赖于Σ-Δ调制器将模拟信号转换成高速的位流,然后通过数字滤波器处理成最终的数字输出。

### 2.1.2 AD7175的配置参数与寄存器映射

AD7175提供了一系列的寄存器,用于配置其工作参数,如采样速率、增益设置、工作模式等。这些寄存器映射为FPGA提供了配置和读取数据的接口。FPGA需要按照AD7175的寄存器映射表来精确地配置和读取数据。

## 2.2 FPGA的基本概念与作用

现场可编程门阵列(FPGA)是一种可重新编程的集成电路,它允许用户在硬件层面上实现自定义的逻辑和算法。FPGA以其灵活的编程能力和较高的性能,在数据采集、处理和通讯系统中发挥着核心作用。

### 2.2.1 FPGA的技术特点与应用场景

FPGA能够同时处理多个信号,提供了并行处理的能力,这使得它在处理高速数据流方面具有独特的优势。由于其可重配置的特性,FPGA在需要快速迭代和适应多种标准的应用场景中特别有用。

### 2.2.2 FPGA的设计流程与开发工具

设计FPGA通常遵循以下步骤:需求分析、设计输入、功能仿真、综合、布局与布线、时序分析以及硬件测试。在这个过程中,开发人员通常会使用如Xilinx Vivado、Altera Quartus II等专业工具。

## 2.3 硬件接口连接与设计要点

在设计AD7175与FPGA的硬件接口时,必须考虑电气连接的规范和设计的挑战,确保信号的完整性和系统的可靠性。

### 2.3.1 AD7175与FPGA的电气连接规范

AD7175与FPGA之间的接口可以通过SPI或并行接口实现。对于SPI接口,需要确保时钟频率、数据速率和引脚连接都符合AD7175的数据手册要求。连接时还需要考虑信号完整性,例如,添加适当的终端电阻来减少反射。

### 2.3.2 硬件接口设计的挑战与解决方案

硬件接口设计面临的挑战包括信号完整性问题、电磁兼容(EMC)以及电源管理。解决这些问题的方法包括使用差分信号来提高抗干扰能力、设计良好的接地策略和合适的去耦合电容。

接下来,我们将深入探讨AD7175与FPGA通信协议的理论分析,包括信号时序、同步机制、物理层设计考量以及数据链路层的设计与实现。

```

# 3. AD7175与FPGA通信协议的理论分析

## 3.1 通信协议的核心概念与要素

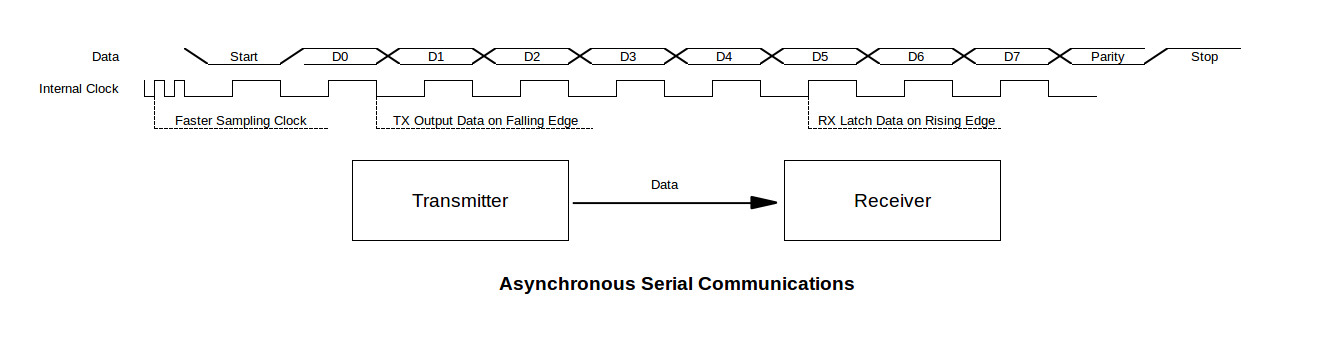

### 3.1.1 信号时序与同步机制

在AD7175与FPGA之间建立稳定可靠的通信协议,信号的时序与同步机制是至关重要的。信号时序描述了数据如何在时间上被准确地采样和同步,而同步机制则确保了数据传输的准确性和完整性。AD7175作为一个高精度模数转换器(ADC),其采样率、分辨率以及通信速率都是影响时序的关键因素。

信号的时序通常涉及到采样时钟、数据有效窗口以及建立时间和保持时间等参数。在设计AD7175与FPGA的通信时,需要精确控制这些时序参数以避免数据的错位或丢失。例如,AD7175的输出数据速率是由SCLK(串行时钟)来控制的,而CS(片选)则用于启动转换过程并使数据准备好被读取。

同步机制方面,常见的有主从同步、握手协议等。在主从同步模式中,FPGA通常作为主设备,负责生成时钟信号并驱动通信过程;而AD7175作为从设备,按照FPGA的指令进行数据转换,并在指定的时序下输出数据。握手协议则是一种双向同步机制,通过请求和应答信号来确保数据传输的正确进行。

为了实现有效的同步,AD7175与FPGA的通信协议通常采用边沿触发或者电平触发的方式来采样数据。在边沿触发模式下,数据在时钟信号的上升沿或下降沿被锁存;在电平触发模式下,数据在时钟信号保持稳定电平的期间被采样。

以下是AD7175与FPGA通信的一个简化代码示例,展示了如何通过FPGA来控制AD7175的同步采样:

```verilog

module ad7175_communication (

input wire clk, // FPGA的系统时钟

input wire start_conv, // 开始转换信号

output wire cs, // 片选信号

output wire sclk, // 串行时钟

input wire data_ready, // 数据就绪信号

input wire [15:0] data_in // AD7175的数据输入

);

reg [3:0] state; // 定义状态机的当前状态

// 状态机逻辑,用于控制与AD7175的通信时序

always @(posedge clk) begin

case(state)

0: begin

// 等待开始转换信号

if(start_conv) begin

state <= 1;

end

end

1: begin

// 拉低片选信号,开始通信

cs <= 0;

state <= 2;

end

2: begin

// 生成时钟信号,读取数据

sclk <= ~sclk;

```

0

0