Verilog高级技巧:从基础到优化AD7175控制逻辑

发布时间: 2025-01-10 12:30:20 阅读量: 12 订阅数: 12

Python图像识别示例及代码,3不不同级别的代码示例,详细

# 摘要

本文综述了Verilog HDL基础知识,重点介绍AD7175模数转换器的工作原理、特性及其应用场景。详细阐述了如何利用Verilog HDL进行AD7175控制逻辑的设计,包括代码结构、时序控制、初始化和数据采集流程。进一步探讨了性能优化的策略,包括代码优化、资源管理和集成测试。文章还涵盖了进阶技巧,如多通道数据处理、噪声抑制技术,并预测了与FPGA和SoC集成的未来趋势。最后,通过一个实践案例,分析了Verilog控制AD7175的项目实施过程和性能评估。本文旨在为工程师提供一套完整的技术指南,用于高效和准确地应用Verilog控制AD7175模数转换器。

# 关键字

Verilog HDL;AD7175模数转换器;控制逻辑设计;性能优化;多通道数据处理;FPGA集成

参考资源链接:[FPGA实现AD7175多路复用ADC控制逻辑Verilog代码详解](https://wenku.csdn.net/doc/4gr8x5ia3t?spm=1055.2635.3001.10343)

# 1. Verilog HDL基础知识回顾

在深入探讨Verilog HDL在AD7175模数转换器控制逻辑中的应用之前,让我们先回顾一下Verilog的基础知识。Verilog是一种硬件描述语言,主要用于电子系统的设计和描述。在数字电路设计和FPGA编程中,它扮演着重要的角色。了解Verilog基础对于设计高效且可靠的控制逻辑至关重要。

## 1.1 Verilog的基本组成

Verilog代码主要由模块(module)构成,每个模块代表一个硬件功能块。模块内可以定义端口(port)、参数(parameter)、信号(signal)、寄存器(reg)、线网(net)等基本元素。通过组合这些元素,我们可以实现各种电路功能。

```verilog

module adder(

input [3:0] a, b, // 4-bit input ports for operands

output [4:0] sum // 5-bit output port for sum result

);

assign sum = a + b; // Assigning sum of a and b to output port

endmodule

```

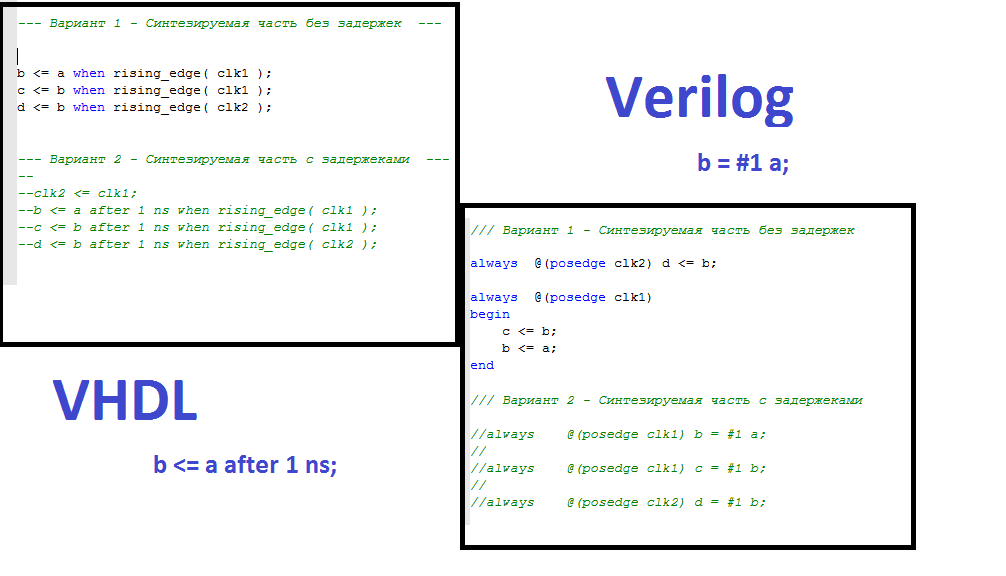

## 1.2 时序控制与并发行为

Verilog中描述硬件行为有两种基本方式:过程化过程和并发过程。过程化过程如`initial`和`always`块,用于定义时序逻辑,描述在特定事件或时钟边沿触发的行为。并发过程如`assign`语句,用于描述组合逻辑,它表明信号的赋值是持续发生的。

## 1.3 设计的层次化和模块化

为了便于管理和维护,设计应该采用层次化和模块化的方法。将复杂系统分解为多个模块,每个模块专注于一组相关的功能。这种设计方法使得代码易于阅读、修改和复用,是高效硬件设计的关键。

在下一章中,我们将深入了解AD7175模数转换器的特性及其在实际应用中的作用。在此之前,请确保你对Verilog的基本概念和编程方法有一个坚实的理解。

# 2. AD7175模数转换器的介绍

## 2.1 AD7175的工作原理和特性

### 2.1.1 模数转换器的基本概念

在数字系统中,模数转换器(ADC)是实现模拟信号与数字信号之间转换的关键组件。这种转换是通过采样、量化和编码三个过程完成的。模数转换器的性能直接影响到整个系统的测量精度和速度,因此在设计过程中选择合适的ADC至关重要。

AD7175是由Analog Devices公司生产的一款高精度24位Σ-Δ型模数转换器。它具有良好的噪声抑制能力,可以达到非常高的分辨率,特别适合于工业测量和医疗设备等领域。Σ-Δ型ADC通过过采样和数字滤波技术,将模拟信号转换为数字信号,并能够实现极高的精度和稳定性。

### 2.1.2 AD7175的硬件接口和通信协议

AD7175提供了灵活的数字接口选项,包括串行外设接口(SPI)和I2C接口,便于与各种微控制器(MCU)和数字信号处理器(DSP)等进行通信。其SPI接口支持最高3MHz的通信速率,而I2C接口则支持标准、快速和高速模式。

在硬件接口设计中,AD7175的引脚配置要遵循其电气特性要求。例如,数字地(DGND)和模拟地(AGND)需要分开处理,以避免数字噪声对模拟信号的干扰。同时,AD7175的通信协议设计需要遵循相应的时序要求,以确保数据传输的准确性和稳定性。

## 2.2 AD7175的应用场景和设计要求

### 2.2.1 精度、速度和电源管理要求

AD7175的一个显著特点是具有很高的精度和较宽的动态范围,使得其在精密测量领域有着广泛的应用。在设计中,需要关注其精度、速度和电源管理的要求。例如,AD7175在250kSPS的最大吞吐率下,仍然能够提供高达22位的有效分辨率。

在电源管理方面,AD7175支持多种电源电压配置,设计者可以根据实际应用需要选择合适的电源电压。此外,低功耗设计是现代电子设计的趋势,因此在设计中应充分考虑AD7175的功耗,并采取适当的优化措施。

### 2.2.2 常见的设计挑战和解决方案

在使用AD7175时,设计者可能会遇到一些常见的挑战。例如,高速信号的布线可能会导致信号完整性问题,从而影响ADC的性能。对此,可以采用多层板设计和信号回路优化的方法,以减少信号串扰和反射。

另一个挑战是如何实现高精度的参考电压源。AD7175的性能很大程度上依赖于参考电压的稳定性。设计者需要选择合适的低噪声参考电压源,并考虑如何进行稳定的电源分配和去耦设计,以确保参考电压的纯净。

在本章节中,我们介绍了AD7175模数转换器的工作原理、特性以及在应用中可能遇到的挑战和解决方案。下一章节,我们将深入探讨如何在Verilog中设计用于控制AD7175的逻辑。

# 3. Verilog在AD7175控制逻辑中的应用

## 3.1 设计AD7175控制逻辑的Verilog代码结构

### 3.1.1 接口定义和模块划分

设计一个用于控制AD7175的Verilog模块时,首先需要对模块的接口进行定义。这些接口通常包括对AD7175进行通信所必须的信号线,比如数据线(SDI/SDO)、时钟信号(SCLK)、片选信号(CS)以及可能的中断信号等。对这些信号线的定义,需要精确地映射到AD7175的数据手册中指定的物理引脚。

在定义了接口之后,就需要划分不同的模块,每个模块完成特定的功能。比如,可以设计一个独立的模块用于时序控制,另一个模块负责数据的打包与解包。这样的模块化方法有助于代码的维护和后续的功能扩展。

```verilog

// 定义AD7175控制模块的接口

module ad7175_controller(

input wire clk, // 时钟信号

input wire reset_n, // 复位信号,低电平有效

input wire cs_n, // 片选信号,低电平有效

input wire sclk, // SPI时钟信号

inout wire sdo, // SPI数据输出

output wire sdi, // SPI数据输入

// 其他内部使用的信号和接口

// ...

);

// 模块内的信号定义

reg [7:0] data_out;

wire [7:0] data_in;

reg [15:0] config_reg; // 配置寄存器

// 实现模块的逻辑

// ...

endmodule

```

### 3.1.2 时序控制和信号同步

在与AD7175通信的过程中,确保时序正确是非常关键的。这涉及到所有与AD7175的交互活动都需要在适当的时钟边沿发生,确保数据能够准确无误地被发送和接收。

信号同步是另一个需要特别注意的点,特别是在与片外设备通信时。由于可能存在不同的时钟域,所以需要确保所有信号在被处理前都已经被正确地同步。

```verilog

// 时序控制的简单示例

always @(posedge clk or negedge reset_n) begin

if (!reset_n) begin

// 复位逻辑

end else begin

if (!cs_n) begin

// 片选信号激活时,执行SPI通信相关的操作

// ...

end

end

end

// 信号同步示例

// 假设有一个异步信号asyn_in,需要同步到本模块的时钟域

reg [1:0] sync_reg;

always @(posedge clk or negedge reset_n) begin

if (!reset_n) begin

sync_reg <= 2'b00;

end else begin

sync_reg <= {sync_reg[0], asyn_in};

end

end

wire synched_signal = sync_reg[1];

```

## 3.2 实现AD7175的初始化和数据采集流程

### 3.2.1 配置寄存器的编程方法

为了使AD7175工作在预期的状态,第一步是对其进行初始化。这涉及到对一系列内部配置寄存器的编程。比如,可以设置采样速率、输入通道、增益等参数,以适应特定的应用需求。通过SPI接口发送适当的命令和数据可以完成这些设置。

在编写代码时,需要确保遵循AD7175的数据手册中指定的寄存器地址和位定义。下面的代

0

0