【HyperBus时序模拟工具】:提升设计效率与系统效益的秘诀

发布时间: 2024-12-26 01:46:49 阅读量: 5 订阅数: 7

# 摘要

HyperBus作为一种高效率的内存接口技术,近年来在高性能系统设计中得到广泛应用。本文首先介绍HyperBus技术及其应用场景,随后深入探讨了其时序理论基础,包括协议特点、信号与时序图分析、时序参数的重要性以及时序优化策略。接着,文中详细说明了HyperBus时序模拟工具的使用方法和技巧,并通过模拟案例分析展示了其在问题诊断和解决中的应用。进一步地,本文阐述了模拟工具在自定义测试、故障排查与性能调优、集成与自动化测试方面的高级应用。最后,对HyperBus技术的未来展望与挑战进行了讨论,包括发展趋势、系统效益作用以及当前所面临的挑战和应对策略。整体而言,本文旨在为设计人员提供全面的HyperBus技术知识和应用指南,以便在现代系统设计中有效利用这一技术。

# 关键字

HyperBus技术;时序理论;模拟工具;故障排查;性能调优;未来展望

参考资源链接:[HyperBus技术详解:高性能DDR总线的信号优化](https://wenku.csdn.net/doc/6n51i2v3ts?spm=1055.2635.3001.10343)

# 1. HyperBus技术简介与应用场景

## 1.1 概述

HyperBus是一种先进的存储接口技术,专为高性能、低延迟的内存访问而设计。这种技术广泛应用于需要快速、稳定数据传输的场景,如高端计算、移动设备以及物联网等领域。

## 1.2 技术特点

HyperBus最大的特点在于它的高速数据吞吐能力和低延迟特性。其采用的双线制和差分信号技术使得它在信号完整性与稳定性方面表现出色。

## 1.3 应用场景

具体的应用场景包括但不限于高分辨率图像和视频处理、高速缓存、以及高速数据采集系统。通过HyperBus接口,这些应用场景能够实现更加高效的数据通信。

这一章节介绍了HyperBus技术的基础知识和它的主要应用场景,为读者提供了对HyperBus技术的初步认识。随后的章节将对时序理论、模拟工具应用、高级应用以及未来展望进行详细讨论。

# 2. HyperBus时序理论基础

## 2.1 HyperBus协议概述

### 2.1.1 协议的主要特点

HyperBus是一种高性能的内存接口标准,最初由Cypress Semiconductor推出,旨在简化内存接口设计,提高数据传输速率。与传统的并行接口相比,HyperBus具有以下几个显著的特点:

- **高速串行通信**:HyperBus采用高速串行接口,相比于传统并行接口,能够在更少的引脚数下实现更高的数据传输速率。

- **简单的硬件接口**:通过减少所需的信号线数量,简化了硬件设计,降低了系统成本。

- **灵活的时钟管理**:提供灵活的时钟控制选项,包括时钟极性(CPOL)和时钟相位(CPHA)配置,以支持不同类型的微控制器(MCU)。

- **协议兼容性**:设计者可以根据需要选择不同级别的协议版本,包括HyperBus和HyperRAM。

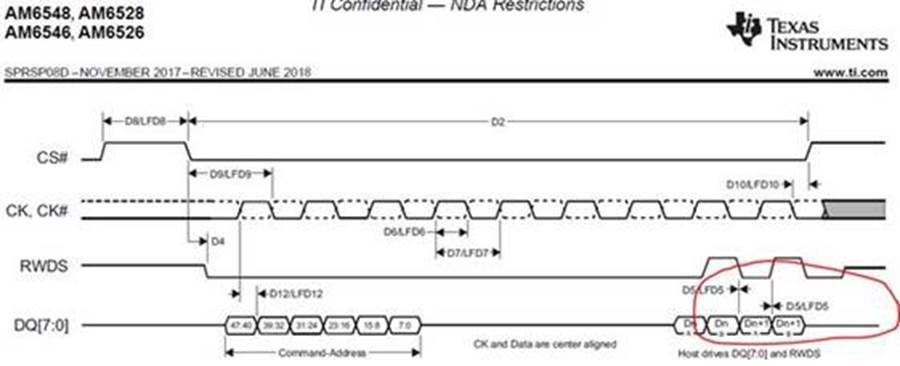

### 2.1.2 信号与时序图分析

在HyperBus协议中,关键信号包括:

- **CLK(时钟信号)**:用于同步数据传输。

- **CS#(片选信号)**:用于选通特定的存储器设备。

- **RWDS(读/写数据选通信号)**:在写操作时用于数据掩码,在读操作时用于延迟调整。

- **DQ(数据/地址/命令总线)**:用于传输数据、地址和命令信息。

时序图是一个非常有用的工具,用于理解数据如何在各个信号上随时间变化。下面是典型的写操作时序图的分析:

- **时钟信号(CLK)**:通常由控制器产生,频率可以达到166MHz。时钟信号是高电平和低电平交替出现的方波。

- **片选信号(CS#)**:在进行写操作时,CS#信号必须被激活(变为低电平),表明存储器设备已被选中。

- **数据/地址/命令总线(DQ)**:数据在CLK的上升沿和/或下降沿传输。数据传输的速率取决于CLK频率以及在数据传输期间CS#信号的状态。

```mermaid

sequenceDiagram

participant CLK

participant CS#

participant DQ

Note over CLK,CS#: Start of write operation

CS#->>-CLK: CS# is pulled low

Note over DQ,CLK: Data setup before rising edge

CLK->>-DQ: Data transferred on the rising edge of CLK

Note over DQ,CLK: Data hold after the edge

```

## 2.2 时序参数与要求

### 2.2.1 时序参数的意义

时序参数在任何高速通信协议中都是至关重要的,它们定义了信号必须满足的严格时间限制。对于HyperBus来说,这些参数包括但不限于:

- **tDSU (Data Setup Time)**:数据在时钟上升沿之前必须稳定设置的时间。

- **tDH (Data Hold Time)**:数据在时钟上升沿之后必须保持稳定的时间。

- **tCSSU (CS# Setup Time)**:片选信号在时钟上升沿之前必须稳定设置的时间。

- **tCSH (CS# Hold Time)**:片选信号在时钟上升沿之后必须保持稳定的时间。

### 2.2.2 时序参数在设计中的影响

在设计时,正确理解和遵守时序参数至关重要,因为任何违反时序要求的情况都可能导致数据传输错误。例如:

- **违反tDSU和tDH**:如果数据没有在时钟上升沿之前或之后保持足够时间的稳定状态,接收器可能无法正确地采样数据。

- **违反tCSSU和tCSH**:如果片选信号没有在正确的时钟边沿之前或之后稳定,可能造成设备无法正确识别或响应命令。

了解和设计这些时序参数的最有效方法是使用时序分析工具,这些工具可以在设计的早期阶段预测和纠正潜在的时序问题。

## 2.3 时序优化理论

### 2

0

0