【HyperBus时序规范测试与验证】:关键步骤与方法指南

发布时间: 2024-12-26 02:14:39 阅读量: 5 订阅数: 7

HyperBus时序规范:低信号计数,高性能DDR总线

# 摘要

HyperBus技术作为一种高速内存接口技术,在现代电子系统设计中扮演着关键角色。本文首先介绍了HyperBus的基本概念和时序基础,然后深入探讨了其时序规范的理论知识,包括接口标准、时序参数以及系统设计中的时序规范。接着,本文详细说明了HyperBus时序规范的测试步骤和实践操作,包括测试环境搭建、时序参数测量、数据比对规范以及测试结果的验证和报告编制。文章最后深入探讨了时序规范的高级应用,包括自动化测试、持续集成以及特殊应用场景下的时序挑战和适应性,为HyperBus时序优化和系统性能提升提供了实践指导和策略。

# 关键字

HyperBus技术;时序规范;接口标准;参数测量;系统设计;性能优化;自动化测试

参考资源链接:[HyperBus技术详解:高性能DDR总线的信号优化](https://wenku.csdn.net/doc/6n51i2v3ts?spm=1055.2635.3001.10343)

# 1. HyperBus技术概述与时序基础

在现代IT架构中,存储接口技术是保障数据传输效率和系统稳定性的关键。HyperBus作为一种高性能的存储接口,广泛应用于高速度、高数据吞吐量的场合。本章首先介绍HyperBus技术的基础知识,然后深入分析其时序基础,为后续章节中对HyperBus时序规范的深入探讨打下基础。

## 1.1 HyperBus技术简介

HyperBus技术是一种专为高速存储接口设计的协议,能够支持高达333MB/s的数据传输率。它通过一个简化的设计来优化性能,具有较少的引脚数量和低功耗特性。这种接口广泛应用于各种嵌入式系统和移动设备中,尤其适合与闪存和动态随机存取存储器(DRAM)等内存类型的接口。

## 1.2 时序基础与重要性

在电子工程和计算机科学中,时序指的是信号和事件的相对时间关系。对于HyperBus这样的高速接口来说,精确的时序控制至关重要。它确保数据能够准确无误地在控制器和存储器之间传输,任何时序上的偏差都可能导致数据错误或性能瓶颈。因此,在设计和测试HyperBus系统时,对时序参数的理解和测量是一个核心环节。

## 1.3 本章小结

通过本章内容,我们了解了HyperBus技术的基本概念和应用场景,并强调了时序控制在其中的重要角色。接下来,我们将深入探讨HyperBus时序规范的具体内容,以及如何在实际应用中对这些时序参数进行测量和优化。

# 2. HyperBus时序规范理论知识

### 2.1 HyperBus接口标准与特性

#### 2.1.1 HyperBus的物理和电气特性

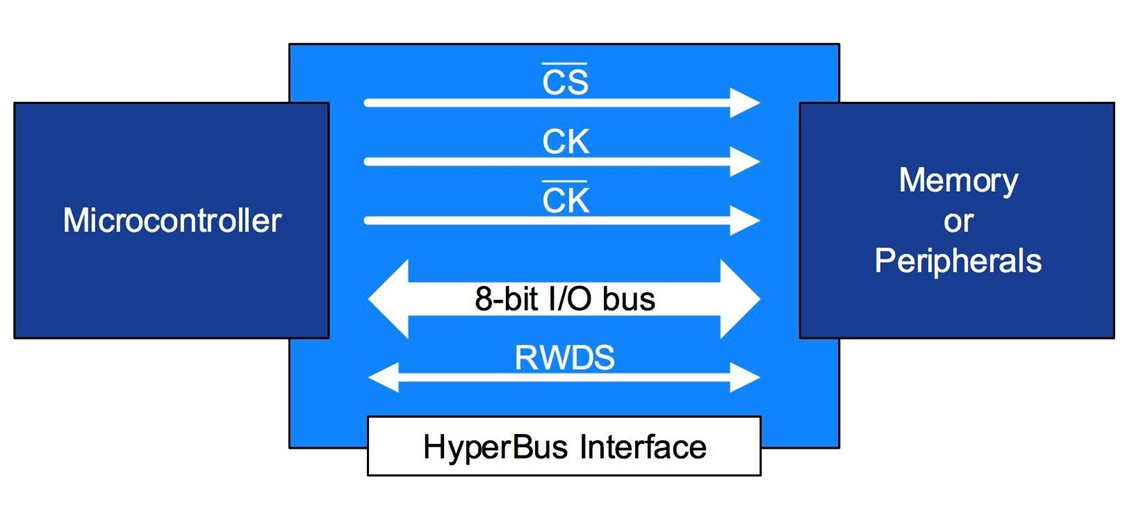

HyperBus是由Cypress Semiconductor公司推出的高速内存接口技术,设计用于低引脚数、高性能、高数据吞吐率的应用。HyperBus接口标准支持多种内存类型,如HyperFlash和HyperRAM,提供比传统SPI接口更优的性能。其物理特性包括:

- **8位数据宽度**:一次传输8位数据,支持并行数据传输。

- **双通道操作**:支持数据和命令通道分离,进一步提升性能。

- **低引脚数**:相较于其他高速接口,HyperBus只需要很少的引脚进行通信。

- **最大时钟频率**:目前版本支持最高166MHz,适用于低功耗和高性能应用。

电气特性方面,HyperBus采用CMOS逻辑电平标准,并通过精确的时序控制来确保数据传输的稳定性与速度。这种接口的电气特性包括:

- **低电压差分信号(LVDS)**:使用LVDS来提高信号完整性和降低电磁干扰。

- **上拉/下拉电阻**:要求外部电路提供适当的上拉/下拉电阻来稳定信号电平。

- **电源管理**:支持多种电源模式,包括低功耗模式和睡眠模式,以适应不同的节能需求。

#### 2.1.2 HyperBus的协议特性与优势

HyperBus协议通过一系列的控制信号来管理数据传输,其中包括:

- **时钟信号** (`CLK`): 控制数据的采样时间点。

- **控制信号** (`CS#`, `RESET#`, `RWDS`): 用于控制数据流的开始、结束、方向以及数据宽/窄模式。

- **地址/命令信号** (`DQ[7:0]`): 用于传输地址或命令信息。

其主要优势在于:

- **低延时**:相比传统SPI接口,具有更低的命令到数据的访问延迟。

- **高速数据吞吐**:能够实现高达1.6Gbps的速率。

- **高效的内存访问**:由于命令和数据可以并行处理,因此读写操作更加高效。

- **简化设计**:简单的信号和较低的引脚数量,使得硬件设计和布线更加简单。

### 2.2 时序参数与容限分析

#### 2.2.1 时序参数的定义和重要性

在数字电路设计中,时序参数是确保数据正确传输和同步的关键因素。对于HyperBus接口,时序参数包括但不限于:

- **时钟周期(T)`CLK`**:时钟信号从一个上升沿到下一个上升沿的时间间隔。

- **建立时间(tSU)**:数据稳定出现在数据线上的时间,必须早于时钟信号的捕获边缘。

- **保持时间(tH)**:数据必须在时钟捕获边缘之后保持稳定的时间。

- **数据传输时间(tD)**:从发送设备到接收设备的数据传输延迟。

- **总线占用时间(tO)`CS#`**:片选信号的持续时间。

这些参数的准确性对于保证接口的稳定性和性能至关重要。若时序参数设置不当,可能导致数据传输错误、系统不稳定甚至崩溃。

#### 2.2.2 时序参数的容限和测量方法

在实际应用中,由于硬件设备的公差和环境因素,每个时序参数都有一定的容限值。HyperBus规范会定义这些参数的最坏情况容限,以确保在各种条件下接口的可靠运行。测量这些参数通常需要高速示波器等精密测试设备,以下是测量的基本步骤:

- **测试设备的校准**:确保所有测试设备的准确性和精确性。

- **信号捕获**:捕获时钟、数据和控制信号。

- **波形分析**:使用示波器软件分析信号波形,测量各时序参数。

- **数据记录**:记录测量数据,用以分析和调整时序设置。

通过这些步骤可以验证时序参数是否满足HyperBus规范的要求。

### 2.3 时序规范的理论基础

#### 2.3.1 时序规范在系统设计中的角色

在系统设计中,时序规范是确保各个组件能够正确配合工作的重要保证。接口的时序规范可以影响到数据的完整性和系统的整体性能。在设计阶段,工程师需要考虑以下几个方面:

- **同步机制**:必须确保数据同步在全系统范围内的一致性。

- **时钟域交叉**:在多时钟域系统中,需要特别注意时钟域之间的同步问题。

- **信号完整性**:保证信号在传输路径上不受干扰,且到达目的地时仍保持可辨识的逻辑状态。

时序规范在整个设计流程中起到了至关重要的作用,它不仅指导了硬件设计,还影响了软件的开发,比如驱动程序和应用层的时序配合。

0

0