【DSP与FPGA协同】:TMS320F28004x与FPGA系统集成技术解析

发布时间: 2024-12-25 17:58:38 阅读量: 5 订阅数: 10

单片机与DSP中的DSP+FPGA结构在雷达模拟系统中的应用

# 摘要

本文针对数字信号处理器(DSP)与现场可编程门阵列(FPGA)的协同设计进行了深入探讨。首先概述了DSP与FPGA协同的背景及其重要性,随后详细介绍了TMS320F28004x DSP的基础知识,包括其架构、编程模型以及实时性能分析。接着,文章转向FPGA的基础知识、设计开发流程以及硬件调试与验证技巧。在此基础上,进一步深入探讨了DSP与FPGA间接口技术、实时数据交换与同步问题。最后,通过具体案例分析,展示了DSP与FPGA协同设计在嵌入式系统设计和硬件加速优化策略中的应用,并提出了系统集成与性能优化的策略。本文旨在为工程技术人员提供一套完整的DSP与FPGA协同设计解决方案,以增强系统集成的兼容性、优化性能并提升整体可靠性。

# 关键字

DSP;FPGA;协同设计;实时性能;接口技术;系统集成

参考资源链接:[TI C2000系列DSP TMS320F28004x中文手册:详细3407页指南](https://wenku.csdn.net/doc/mo6x440pot?spm=1055.2635.3001.10343)

# 1. DSP与FPGA协同概述

数字信号处理器(DSP)和现场可编程门阵列(FPGA)是现代电子系统设计中常用的两种关键组件。在许多应用中,两者被协同使用来发挥各自的优势:DSP强大的数值计算能力和FPGA卓越的并行处理能力。本章将对DSP与FPGA协同工作的方式和优势做一个概述。

## 1.1 协同工作原理

DSP擅长执行复杂的数值计算和算法,适合处理数字信号。FPGA能够以非常低的延迟处理大量并行数据流,非常适合实现硬件加速和定制的逻辑功能。通过协同工作,FPGA可以作为DSP的前端,进行数据预处理和预过滤,减轻DSP的负担,并加速整个系统的响应时间。

## 1.2 协同设计的优势

当DSP与FPGA协同设计时,设计者可以将算法的高性能部分映射到FPGA上,而将控制和决策部分交给DSP来处理。这种分工不仅提高了系统的运算速度,也优化了功耗和成本。此外,FPGA的灵活性允许设计者在硬件层面调整和优化算法,使得系统具有很好的扩展性和可升级性。

## 1.3 协同设计的应用实例

在无线通信基站、医疗成像设备、高速数据采集系统等多个领域,DSP与FPGA的协同设计得到了广泛应用。例如,在4G/5G基站的基带处理中,FPGA可以负责复杂的物理层处理任务,而DSP则可以处理协议栈和用户数据处理,这样的搭配极大地提高了数据处理的效率和系统的整体性能。

通过这一章节的概览,我们了解了DSP和FPGA协同工作的重要性以及带来的优势,并且通过实例展示了这种技术在实际应用中的价值。在后续章节中,我们将深入探讨DSP和FPGA的技术细节,以及如何更有效地实现它们之间的协同设计。

# 2. TMS320F28004x DSP基础

### 2.1 TMS320F28004x DSP架构介绍

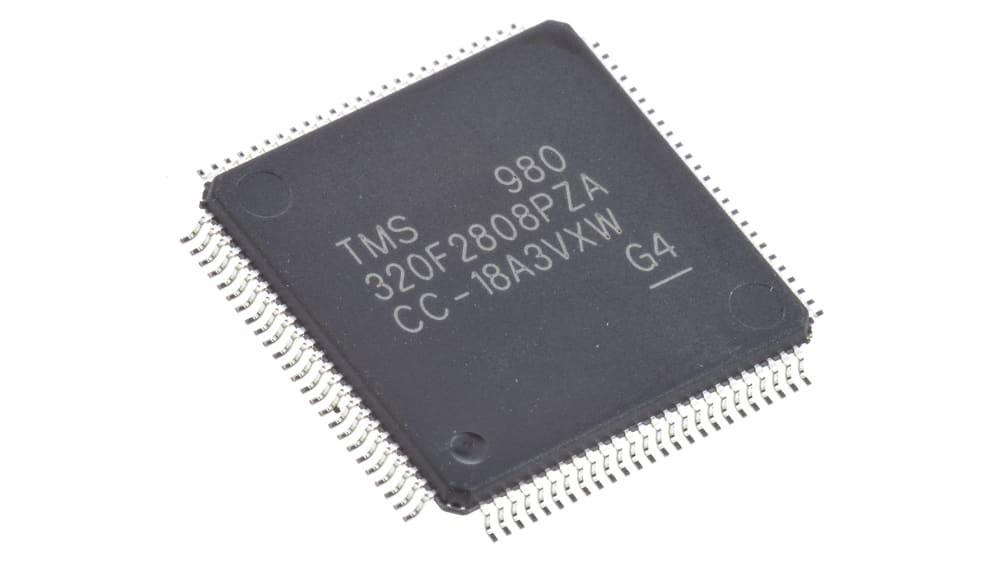

#### 2.1.1 核心特性和性能参数

TMS320F28004x系列是德州仪器(Texas Instruments,简称TI)推出的高性能、低功耗的数字信号处理器(DSP),主要针对工业控制系统和电机控制等应用场景。它采用了32位RISC架构,具有快速的浮点运算能力,并集成了高精度的模拟信号处理组件,例如12位模数转换器(ADC)和脉宽调制器(ePWM)。

核心特性包括:

- 高速CPU时钟,可以达到60MHz,使得处理任务更加迅速。

- 丰富的外设集成,包括CAN模块、串行通信接口(SCI)、串行外设接口(SPI)等。

- 片上内存,提供高达128KB的闪存以及18KB的RAM,减少了外部存储器的依赖,降低系统成本。

性能参数方面,TMS320F28004x系列DSP能够提供快速中断响应,具有高度灵活的事件管理功能,以及先进的电源管理选项。

#### 2.1.2 存储器和外设接口

在存储器方面,除了核心的RAM和Flash之外,TMS320F28004x系列DSP还提供了一定数量的闪存和RAM作为局部数据存储,这有助于优化内存使用和提高系统的整体性能。

对于外设接口,此系列DSP提供了丰富的外设接口,允许开发者轻松扩展系统功能。例如,支持多个SCI和SPI接口,这使得DSP能够方便地与各种传感器和通信模块相连接。此外,ePWM模块则为精确控制电机和开关电源提供了强大的工具。

### 2.2 TMS320F28004x DSP的编程模型

#### 2.2.1 CPU和指令集概览

TMS320F28004x系列DSP的CPU基于C28x内核,支持32位整数和浮点运算。指令集采用改进型哈佛架构,这意味着数据和指令在不同的存储空间,可实现并行读取,提高了指令执行的效率。在DSP指令集中,特别优化了数字信号处理算法,例如快速傅里叶变换(FFT)、数字滤波器等,这使得该系列DSP在信号处理领域表现出色。

#### 2.2.2 开发环境和工具链

开发TMS320F28004x系列DSP,通常使用TI提供的Code Composer Studio(CCS),这是一个集成开发环境(IDE),支持代码编辑、编译、调试和性能分析。此外,开发者可以利用Code Generation Tool(CGT)进行算法优化,并使用Xilinx的Vivado等第三方设计工具实现FPGA的协同设计。

#### 2.2.3 程序设计和调试技巧

在程序设计方面,开发者需要注意以下几点:

- 利用中断服务例程来处理时间敏感的任务,以减少系统开销。

- 合理规划内存使用,避免内存泄漏,使用RAM缓存来提高数据访问速度。

- 在编程时要考虑到算法的并行性和数据流的优化,以充分利用DSP的多指令并行处理能力。

调试技巧方面,开发者可以通过串口打印调试信息,使用实时数据观察功能,以及利用CCS内置的逻辑分析器等工具进行调试。在硬件层面,通过JTAG接口可以实现全速调试和非侵入式数据访问。

### 2.3 TMS320F28004x DSP的实时性能分析

#### 2.3.1 中断系统和任务调度

TMS320F28004x系列DSP具有一个高度灵活的中断系统,支持128个中断源,能够处理各种不同优先级的任务。在多任务实时操作系统中,中断服务例程(ISR)的执行效率至关重要,因此,合理配置中断优先级,以及使用中断嵌套和中断屏蔽,对于保证系统的实时性能至关重要。

任务调度方面,可以利用实时操作系统(RTOS)来管理任务切换,或者通过编写自定义的任务调度算法,来确保关键任务能够得到及时执行。在关键任务中,重要的是考虑到上下文切换的成本,合理安排任务优先级和执行时间。

#### 2.3.2 定时器和计数器的应用

在DSP系统中,定时器和计数器是不可或缺的组件,它们可以用于实现任务的时间控制、频率测量、事件计数等。TMS320F28004x系列DSP提供了多个高精度的定时器模块,开发者可以根据需要配置定时器的模式(例如周期模式、连续模式、单次模式等),并设置相应的中断。

计数器通常用于计算事件发生的次数,或者用来实现脉冲宽度测量。在设计时,应当注意定时器和计数器的配置对系统响应时间和资源使用的影响,以保证实时性能。

#### 2.3.3 电源管理和低功耗设计

由于许多DSP应用领域对功耗有着严格的要求,因此电源管理成为设计中不可或缺的部分。TMS320F28004x系列DSP提供了多种低功耗模式,包括睡眠模式、空闲模式和多种深度睡眠模式,能够针对不同的应用场景进行功耗优化。

电源管理的设计关键在于理解系统的功耗需求,并合理地切换DSP的工作状态。例如,在不需要处理高速数据时,可以将DSP置于低功耗模式,而在需要时快速唤醒。此外,还可以通过优化算法,减少不必要的CPU计算,以降低功耗。

在本章节中,我们了解了TMS320F28004x DSP的基本架构、核心特性和性能参数,以及如何进行编程模型设计和实时性能分析。通过这些知识,开发者可以更好地为各种高性能信号处理应用选择合适的DSP芯片,并开发出高效、可靠的系统。

在下一章节中,我们将探索FPGA的基础知识和设计流程,这将为读者提供进一步的硬件设计能力。

# 3. FPGA基础与设计流程

## 3.1 FPGA技术原理和优势

### 3.1.1 可编程逻辑器件简介

可编程逻辑器件(PLD)是FPGA(现场可编程门阵列)的基础,其核心思想是通过硬件描述语言(HDL)编程来实现复杂的逻辑功能,而无需改动实际的硬件电路。FPGA在这一概念上更进一步,提供了更高的灵活性和性能,是现代电子设计中不可或缺的组成部分。

FPGA采用的是基于查找表(LUT)和触发器的架构,能够通过编程实现各种逻辑功能和存储器功能。它们通常包含大量的基本逻辑单元(如逻辑块或逻辑单元),并通过可编程互连资源进行连接。这些资源可以是可编程的输入/输出块(IOBs)、可编程的互连开关矩阵等。

逻辑单元可以被编程为实现组合逻辑(如与门、或门、非门等)和时序逻辑(如触发器和锁存器),提供极大的灵活性。通过编程,FPGA可以被配置成几乎任何数字逻辑电路,包括微处理器、DSP、通信接口、数据处理单元等。

FPGA相比于传统微控制器或ASIC(应用特定集成电路)有很多优势。首先,FPGA在设计周期内可以多次编程和修改,这大大减少了设计周期时间和成本。其次,FPGA具有并行处理能力,适合于处理高速信号处理和复杂算法。最后,FPGA在功耗和热管理上通常优于传统的CPU或GPU解决方案。

### 3.1.2 FPGA与其它PLD的比较

可编程逻辑器件(PLD)分为不同的类别,包括简单可编程逻辑设备(SPLD)、复杂可编程逻辑设备(CPLD)和现场可编程门阵列(FPGA)。在这些类别中,FPGA在可编程性和灵活性上具有显著优势。

SPLD和CPLD通常具有固定的逻辑结构,适用于实现简单的逻辑功能。与之相比,FPGA能够提供更高的逻辑密度、更复杂的逻辑单元以及更多的配置选项。FPGA不仅能够实现简单的逻辑功能,还能够实现复杂的算法和处理器功能。

在性能方面,FPGA的并行处理能力使得其在数据吞吐率和延迟方面优于其他PLD。FPGA设计可实现自定义的硬件加速器,为特定任务提供优化的处理路径。对于需要高速数据处理的应用,FPGA相较于微处理器在性能上有很大的优势。

功耗和成本是另外两个在选择PLD时需要考虑的因素。尽管FPGA提供了更高的灵活性,但通常也意味着更高的功耗和成本,特别是当设计规模增大时。CPLD通常有更低的功耗和成本,但其可配置性、灵活性和性能不如FPGA。

FPGA与ASIC相比,具有快速原型开发和较低的前期投入成本优势。然而,对于大批量生产,ASIC在单位成本和性能上可能更经济。

总的来说,选择哪种PLD取决于特定应用的要求。对于需要快速上市时间、灵活性和可重新编程的应用,FPGA是更佳的选择。而对成本敏感、功耗要求严格且不需要频繁更改设计的应用,则可能会倾向于选择CPLD或ASIC。在实际应用中,FPGA和CPLD甚至ASIC有时也会被结合在一起使用,以达到最佳的性能和成本效益。

## 3.2 FPGA的设计与开发流程

### 3.2.1 设计输入和HDL编码

FPGA开发流程以设计输入开始,这是定义所需功能的过程。设计输入可以通过多种方式完成,包括使用硬件描述语言(HDL),如VHDL或Verilog,或利用图形化的设计工具如Xilinx的Vivado或Intel的Quartus Prime。

在使用HDL进行设计输入时,工程师首先需要根据设计需求编写相应的源代码。代码应该准确地描述硬件设备在电气逻辑层面应如何工作。HDL代码的编写通常包括信号声明、模块实例化、逻辑门描述、行为级和结构级的描述等内容。

一旦HDL代码被编写完成,便可以使用仿真工具来验证设计的逻辑正确性。仿真工具可以模拟FPGA的行为,允许设计者在实际硬件编程之前检查和修正错误。

在HDL编码的过程中,有几个重要的实践需要遵守,以确保设计的高效和成功。首先是代码的可读性和可维护性,良好的编码风格可以减少维护成本并提升后续开发的效率。其次是模块化和重用性,好的设计应该容易被分割成可重用的模块,这不仅可以加快开发速度,还可以提高设计的可靠性。

接下来,设计者需要根据设计要求进行综合,将HDL代码转换成FPGA可识别的门级网表。综合工具通常由FPGA制造厂商提供,并且包含优化算法来满足性能和资源使用的要求。

### 3.2.2 功能仿真和时序分析

功能仿真,通常也称为前仿真,是在综合过程之前对设计进行验证的步骤。它是通过模拟HDL代码的功能来确保逻辑功能的正确性。在这个阶段,设计工程师需要检查逻辑是否与原始规格完全一致。

仿真环境允许设计者模拟输入信号并观察输出信号,以验证设计的正确性。这时可以使用各种激励文件(测试台或测试向量),它们提供了输入信号和预期的输出信号。

然而,仅仅保证功能的正确性是不够的。FPGA中的逻辑门和触发器需要在给定的时间约束下工作,这涉及到时序分析。时序分析是检查设计中信号路径是否满足时序要求,比如设置时间(setup time)和保持时间(hold time)。如果设计没有满足时序要求,可能会出现不可靠的行为,比如信号冲突或数据丢失。

时序分析通常使用时序分析工具来完成,这些工具可以是综合工具的一部分,也可以是独立的工具,如Xilinx的Vivado Timing Analyzer或Intel的TimeQuest Timing Analyzer。时序分析工具检查所有的信号路径,并对违反时序要求的部分给出反馈。

如果发现时序违规,设计者需要进行时序约束,通过指导综合和布局布线过程来满足设计的时序要

0

0