嵌入式系统调试:JTAG引脚配置与性能优化策略(专家版教程)

发布时间: 2025-01-05 17:26:20 阅读量: 19 订阅数: 14

RK3399开发板配置JTAG接口教程-综合文档

# 摘要

JTAG技术作为一种广泛应用于电子系统测试和调试的标准接口,具有不可替代的作用。本文首先介绍了JTAG引脚功能与配置基础,随后深入解析JTAG协议架构,包括核心组件的工作原理和引脚详解。接着探讨了嵌入式系统中的JTAG调试实践,包括不同处理器平台的应用和调试工具的使用。文章进一步分析了JTAG性能优化策略,涉及性能监控、性能瓶颈的识别与调整,以及高级优化技术。最后,展望了JTAG技术在现代嵌入式开发中的创新应用,如物联网设备的远程调试和自动化测试集成,并预测了JTAG在新兴技术中的未来角色。本文旨在为读者提供一个全面的JTAG技术应用和优化指南。

# 关键字

JTAG引脚;协议架构;嵌入式系统;调试工具;性能优化;物联网设备;自动化测试;嵌入式开发

参考资源链接:[JTAG引脚定义详解:从10pin到20pin](https://wenku.csdn.net/doc/6498fd54f8e98f67e0b5ffd7?spm=1055.2635.3001.10343)

# 1. JTAG引脚功能与配置基础

## 1.1 JTAG引脚概述

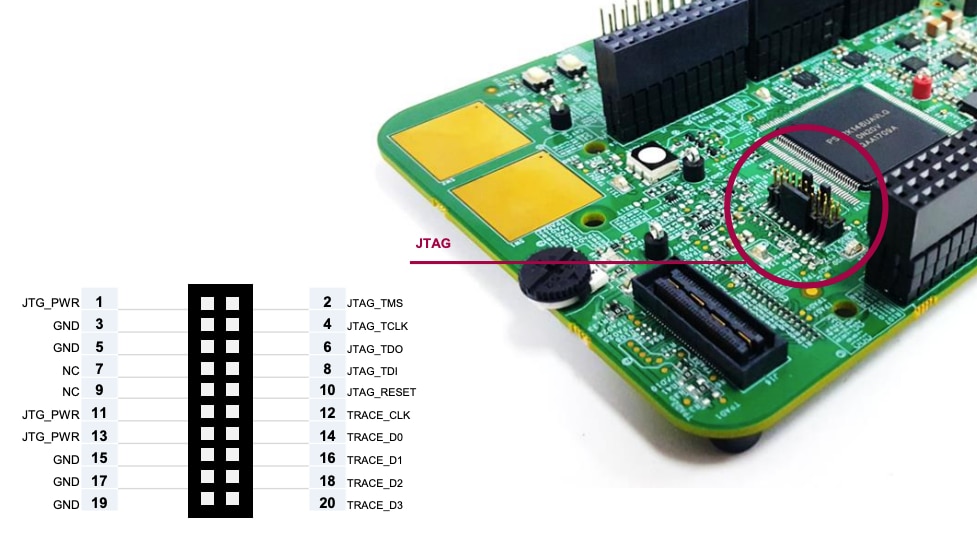

JTAG(Joint Test Action Group)接口是一种广泛应用于嵌入式系统的边界扫描技术。它最初设计用于测试电路板的连接,现已扩展到调试处理器和其他芯片内部逻辑。JTAG接口主要通过五个引脚实现通信:TDI(Test Data In)、TDO(Test Data Out)、TMS(Test Mode Select)、TCK(Test Clock)和TRST(Test Reset)。

## 1.2 TDI和TDO引脚

TDI是测试数据输入,用于将数据序列输入到芯片内部的测试逻辑。TDO是测试数据输出,用于从芯片内部测试逻辑输出数据序列。TDI和TDO两个引脚的配合工作,使得测试信号能够串行地通过设备中的每一个扫描单元。

## 1.3 TMS、TCK和TRST引脚

TMS(Test Mode Select)引脚用于控制JTAG测试逻辑的状态机,告诉设备下一步应该做什么操作。TCK(Test Clock)是测试时钟,同步所有JTAG操作。TRST(Test Reset)引脚用于异步复位JTAG状态机到已知状态,从而初始化测试环境。

在配置JTAG引脚时,通常需要确定它们在硬件连接上的正确性和电气特性的一致性。以ARM处理器为例,不同的ARM芯片可能需要特定的引脚电平和时序要求。因此,了解引脚功能和正确的配置方法是成功利用JTAG接口进行调试和测试的前提条件。

# 2. 深入理解JTAG协议架构

## 2.1 JTAG协议核心组件

### 2.1.1 TAP控制器的工作原理

TAP(Test Access Port)控制器是JTAG协议中实现边界扫描测试的关键组件。它的主要职责是通过一系列的输入信号来控制数据和指令的传输,以及与待测器件内部的测试逻辑进行交互。一个典型的TAP控制器包含以下几个主要状态:Test-Logic-Reset、Run-Test/Idle、Select-DR-Scan、Select-IR-Scan、Capture-DR、Shift-DR、Exit1-DR、Pause-DR、Exit2-DR、Update-DR、Capture-IR、Shift-IR、Exit1-IR、Pause-IR、Exit2-IR和Update-IR。

每个状态都有特定的功能,比如:

- `Test-Logic-Reset` 状态用于初始化TAP控制器并启用测试逻辑。

- `Run-Test/Idle` 状态用于在不执行特定测试时保持控制器在空闲状态。

- `Shift-DR` 和 `Shift-IR` 状态用于串行传输数据和指令。

TAP控制器通过TMS(Test Mode Select)信号来控制状态转换,而TDI(Test Data In)和TDO(Test Data Out)则分别用于输入和输出数据和指令。TRST(Test Reset)信号用于异步复位TAP控制器。

### 2.1.2 TDI、TDO、TMS和TRST引脚详解

- **TDI (Test Data In)**:这个引脚用于串行输入数据和指令,数据在每个时钟周期的上升沿被读取。

- **TDO (Test Data Out)**:数据通过TDO引脚输出,同样是在时钟周期的上升沿。

- **TMS (Test Mode Select)**:此信号用于引导TAP控制器在不同状态之间移动,依据时钟信号上升沿捕获TMS的当前值,以决定下一步状态。

- **TRST (Test Reset)**:此为复位信号,通常为低有效,用于将TAP控制器复位到初始状态。

这些引脚在JTAG通信中起到至关重要的作用,确保了测试数据和指令能够正确地在测试设备和被测设备间传输。

## 2.2 JTAG链和器件识别

### 2.2.1 多器件JTAG链配置

在多器件系统中,JTAG链的配置允许测试数据通过一系列的芯片。JTAG链上每个器件都包含一个TAP控制器,这些控制器串联形成一个链状结构。测试数据从链的顶端输入,依次经过每个器件的TAP控制器,最终数据可以从链的底部输出。

这种配置要求每个器件的TAP控制器正确地处理TDI、TDO、TMS和TRST信号,以确保数据可以正确地流入和流出。在配置多器件JTAG链时,通常需要设定每个器件的IR(Instruction Register)长度和DR(Data Register)长度,以便准确地串行访问每个器件内部的相应寄存器。

### 2.2.2 器件识别与边界扫描

JTAG协议允许使用边界扫描寄存器来识别链上的每个器件。每个器件的边界扫描单元都包含一个IDCODE寄存器,该寄存器包含制造商信息、器件型号和版本号。通过串行地访问每个器件的IDCODE寄存器,可以识别链上所有器件。

边界扫描测试可以利用链上器件的边界扫描单元来进行,这使得测试向量能够在不接触物理引脚的情况下被应用。在器件识别阶段,测试设备可以使用JTAG协议向链上发送IDCODE指令,并通过TDO引脚读取每个器件的ID信息。这个过程有助于确认系统中各个器件的配置和兼容性。

## 2.3 JTAG接口高级设置

### 2.3.1 JTAG速度与时序参数配置

JTAG接口的操作速度通常受到被测设备的时钟频率限制。为了确保可靠的数据传输,时序参数的配置至关重要。关键的时序参数包括:

- TCK频率:测试

0

0