精通FPGA设计

发布时间: 2025-01-05 14:17:04 阅读量: 3 订阅数: 9

# 摘要

本文系统性地介绍了FPGA的设计基础、原理、设计流程、实战技巧以及高级技术。首先,概述了FPGA设计的基础知识和原理,然后详细阐述了从需求分析到设计仿真与验证的设计流程。紧接着,深入探讨了FPGA实战中的时序约束与优化、资源管理与分配、以及IP核的使用与集成。进一步地,介绍了高级FPGA设计技术,包括高级编程技术、SoC设计与FPGA的应用,以及信号与电源完整性的分析与优化。最后,通过案例分析展示了FPGA在通信领域的应用,实时数据处理中的应用,以及定制化IP核开发的实例。本文旨在为FPGA设计人员提供全面的指导和参考,帮助他们有效地进行FPGA设计,并提升设计的质量和性能。

# 关键字

FPGA设计;硬件描述语言;仿真验证;时序优化;资源管理;SoC设计;信号完整性;电源完整性;IP核集成;数据处理;通信协议

参考资源链接:[Altera FPGA RapidIO(srio, 串行快速IO协议)IP核用户手册](https://wenku.csdn.net/doc/6412b793be7fbd1778d4acaf?spm=1055.2635.3001.10343)

# 1. FPGA设计基础与原理

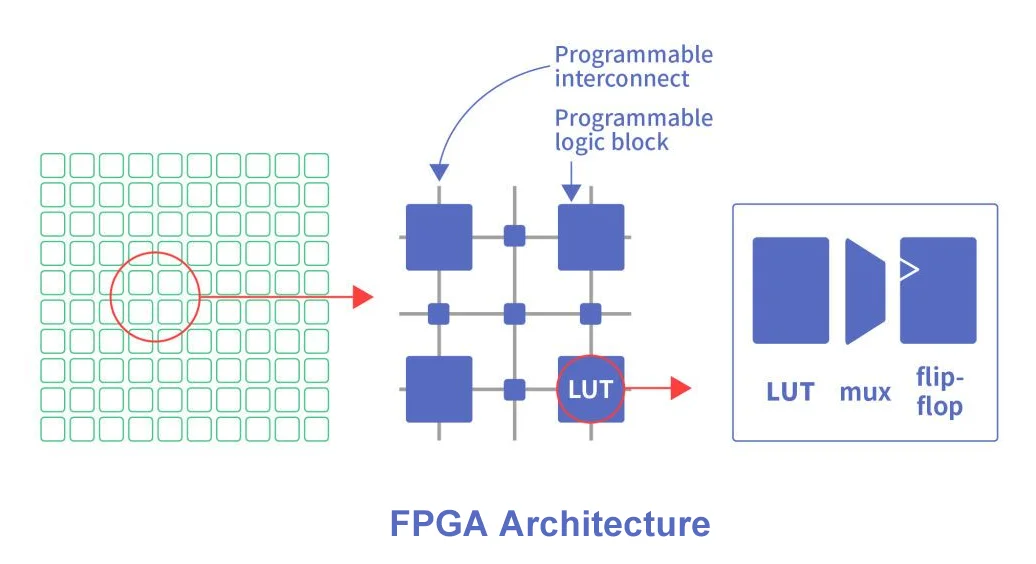

在当今数字电子设计领域中,FPGA(现场可编程门阵列)已经成为了不可或缺的一部分。它是通过编程来配置其内部逻辑功能的一种半导体设备,具有高度的灵活性和定制性。学习FPGA设计,不仅可以帮助工程师快速实现复杂算法的硬件加速,而且对提高系统的性能和降低功耗也有显著效果。

## 1.1 基本概念

FPGA由大量的可编程逻辑单元(如查找表、寄存器等)组成,这些单元通过可编程的互连资源相互连接。通过使用硬件描述语言(HDL),比如VHDL或Verilog,工程师可以描述硬件电路的功能,然后通过综合工具将这些描述转换为FPGA内部的逻辑单元配置。

## 1.2 工作原理

FPGA的每个逻辑单元可以配置为实现各种数字电路功能,比如组合逻辑、时序逻辑、算术运算等。通过编程,可以灵活地改变逻辑单元之间的连接关系,从而实现不同的电路设计。这一特性使得FPGA在原型开发、产品迭代和复杂算法的硬件加速等方面具有独特优势。

## 1.3 应用领域

FPGA被广泛应用于通信、军事、航天、消费电子、工业控制等多个领域。它能够提供高性能的信号处理能力,并且在开发周期短、定制化需求高的项目中表现尤为突出。随着技术的进步,FPGA的性能和容量都有了大幅提升,它正逐渐成为硬件设计中的主要力量。

# 2. FPGA设计流程详解

## 2.1 设计需求分析

### 2.1.1 理解客户需求

在开始FPGA设计之前,与客户的交流至关重要。客户的需求往往决定了设计的方向、规模和性能参数。了解客户需求需要对客户的应用场景进行深入分析,确定设计应该满足的功能、性能以及成本等因素。

1. **功能需求**: 详细询问客户对于FPGA功能的具体要求。例如,是否需要高速信号处理、数据采集、特定协议的实现等。

2. **性能参数**: 确定客户对性能的具体要求,例如工作频率、功耗、时序、延迟等。

3. **接口与协议**: 明确需要支持的外部接口标准和通讯协议。

4. **成本预算**: 客户对成本的承受范围将直接影响设计选材和规模。

5. **时间表**: 设计项目的时间线和关键节点,以确保满足客户的时间要求。

与客户的交流过程中,需要详细记录关键点,并转化为可以量化的技术指标,这将作为后续设计工作的基础。

### 2.1.2 功能规格的定义

将客户的需求转化为具体的功能规格,这一步是设计流程中的核心。功能规格定义需要明确:

1. **输入输出**: 明确FPGA设计的输入输出接口和信号。

2. **逻辑功能**: 详细描述FPGA需要实现的逻辑功能,包括数据处理、控制逻辑等。

3. **性能指标**: 定义时钟频率、数据吞吐率、处理速度等性能参数。

4. **环境要求**: 环境因素例如温度范围、电磁兼容性等。

5. **安全和可靠性**: 系统运行时的安全要求,如故障恢复机制和异常处理。

6. **可维护性**: 提出系统的可维护性要求,如易于调试和升级。

功能规格的定义需要准确无误,因为它是设计流程中其他阶段的基础。如有必要,可以使用表格、流程图等工具来详细阐述和记录功能规格。

## 2.2 硬件描述语言(HDL)介绍

### 2.2.1 VHDL与Verilog基础

硬件描述语言(HDL)是用文本方式来描述数字逻辑电路的语言,FPGA设计中常用的是VHDL和Verilog。

1. **VHDL**: 具有面向对象的特性,可以用来描述复杂的硬件结构和行为。VHDL支持强类型系统,有助于避免设计中的逻辑错误。

2. **Verilog**: 相对VHDL来说语法较为简洁,易于编写,同时拥有大量库支持。Verilog非常灵活,常用于快速原型设计。

两种语言都有其适用场景,VHDL适合复杂系统设计,Verilog则更适合快速开发和修改。选择合适的语言对于后续设计工作的效率至关重要。

### 2.2.2 设计模块的编写

设计模块编写是将功能规格转化为HDL代码的过程。设计模块应该满足以下要求:

1. **模块化**: 确保每个模块有明确的输入输出,并在不同模块之间有良好的接口定义。

2. **可重用**: 编写的代码应尽可能模块化,方便重用和维护。

3. **可测试**: 设计模块时应考虑到测试的便利性,确保每个模块都能被单独测试。

4. **文档**: 提供清晰的文档说明每个模块的功能和使用方法。

下面是Verilog模块的一个简单例子:

```verilog

module adder (

input [3:0] a,

input [3:0] b,

output [4:0] sum

);

assign sum = a + b;

endmodule

```

在这个例子中,定义了一个名为`adder`的加法器模块,它接受两个4位宽的输入`a`和`b`,输出一个5位宽的和`sum`。

编写模块的代码块后面,必须有对应的逻辑分析和参数说明。在此示例中,`assign`语句用于描述组合逻辑的加法操作,而`[3:0]`和`[4:0]`表示数据的位宽。

## 2.3 设计的仿真与验证

### 2.3.1 单元测试与功能仿真

在FPGA设计完成后,第一步验证工作通常是功能仿真。功能仿真主要确保设计的功能符合预期:

1. **单元测试**: 对单个模块进行测试,确保其逻辑正确。

2. **集成测试**: 将多个模块组合在一起进行测试,检查各模块间的接口和数据流是否正确。

3. **测试向量**: 编写针对特定功能的测试向量集,以实现全面的测试覆盖。

4. **覆盖率分析**: 使用覆盖率分析工具评估测试的全面性。

下面是一个简单的VHDL测试台的示例:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity testbench is

-- 测试台无需端口

end testbench;

architecture behavior of testbench is

-- 定义输入输出信号

signal a : std_logic_vector(3 downto 0);

signal b : std_logic_vector(3 downto 0);

signal sum : std_logic_vector(4 downto 0);

begin

-- 实例化待测试模块

uut: entity work.adder

port map (

a => a,

b => b,

sum => sum

);

-- 测试向量应用过程

process

begin

-- 测试向量初始化

a <= "0000"; b <= "0000"; wait for 10 ns;

a <= "0010"; b <= "0001"; wait for 10 ns;

a <= "1010"; b <= "0110"; wait for 10 ns;

-- 测试完成

```

0

0