【Logisim进阶之路】:构建复杂逻辑门电路的秘诀

发布时间: 2024-12-23 07:01:28 阅读量: 7 订阅数: 7

计算机结构与逻辑设计:第三章 门电路.pdf

# 摘要

本文系统回顾了Logisim的基础知识,并深入探讨了逻辑门电路的设计原理与构建技巧,特别是复杂电路的设计、规划、优化及子电路模块化的设计与应用。文章详细介绍了电路复杂度评估、逻辑门数量的减少、电路速度的提高与功耗的降低方法,以及Logisim高级功能在分析和仿真方面的技巧。通过案例分析,展示了如何在实际项目中应用Logisim解决复杂逻辑门电路设计的问题,并提供了创新思路。最后,本文为读者提供了Logisim的扩展学习资源,包括高级功能探索、组件定制以及社区和论坛交流等信息,旨在帮助读者进一步深化学习和应用。

# 关键字

Logisim;逻辑门电路;电路设计;电路优化;模块化设计;电路仿真

参考资源链接:[Logisim 实验二:运算器设计与头歌关卡实践](https://wenku.csdn.net/doc/2qo2ruw1tq?spm=1055.2635.3001.10343)

# 1. Logisim基础知识回顾

## Logisim简介

Logisim是一个易于使用的教育工具,用于设计和模拟数字逻辑电路。它的用户界面直观,允许用户通过拖放方式添加和连接各种逻辑门和组件。

## 基础操作

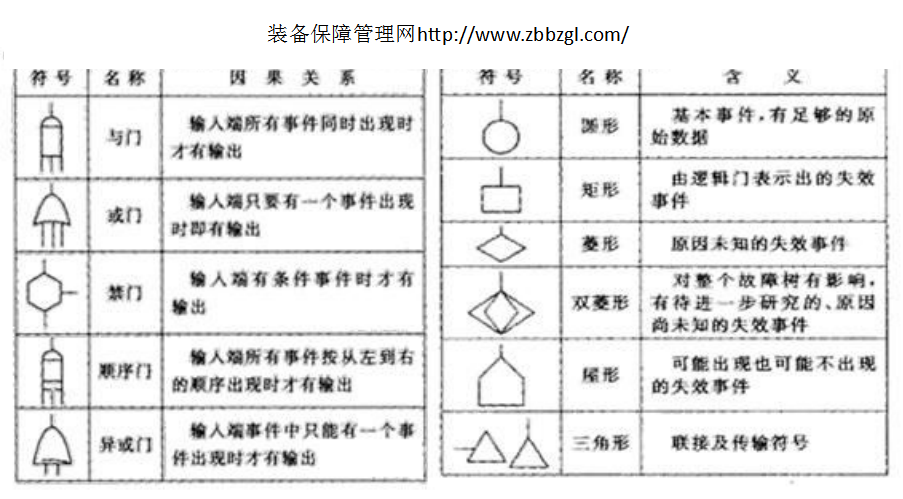

用户首先需要熟悉Logisim的基础操作,比如如何打开Logisim,创建一个新项目,以及如何使用基本的逻辑门(例如与门(AND)、或门(OR)、非门(NOT)等)。这包括如何放置组件,以及如何连接它们来构建简单的电路。

## 电路模拟与测试

Logisim支持电路的实时模拟,用户可以立即看到逻辑门操作的结果。此外,基础章节还将介绍如何使用Logisim的仿真功能来测试电路,并观察不同输入组合对电路输出的影响。这为后面章节深入探讨电路设计打下基础。

在下一章节,我们将深入探讨逻辑门电路的设计原理,探索构建和优化复杂电路的策略。

# 2. 逻辑门电路的设计原理

在电子工程领域,逻辑门电路是构建数字系统的基本组件。逻辑门电路的设计原理不仅关系到数字逻辑电路的正确性,还影响到电路的效率和性能。在这一章节中,我们将深入探讨逻辑门电路的设计原理,包括基本逻辑门的工作机制、逻辑门电路的布局布线原则、以及如何运用这些原理进行实际的电路设计。

## 3.1 复杂逻辑门电路的规划

### 3.1.1 电路设计的前期准备

在设计复杂的逻辑门电路前,前期准备至关重要。首先,需要对电路的功能和性能要求有一个明确的认识。这意味着要详细阅读技术规格说明书,了解电路应实现的逻辑功能,并对性能指标如速度、功耗等有所预期。其次,准备工作还包括对所涉及逻辑门类型的熟悉程度,以及可能用到的其他组件如触发器、计数器等的了解。

接下来,需要选择合适的绘图工具进行电路设计。在本节的上下文中,我们将讨论如何使用Logisim进行复杂逻辑门电路的设计,因为Logisim提供了直观的界面和丰富的组件库,适合教学和小型项目设计。设计开始之前,应先熟悉Logisim的用户界面,掌握基本的绘图工具、组件的添加和删除等操作。

### 3.1.2 电路复杂度的评估与管理

在逻辑门电路设计中,电路的复杂度是一个不可忽视的因素。一个过于复杂的电路可能会导致设计难度增加、布线困难、调试时间延长,甚至可能影响电路的性能。因此,评估和管理电路复杂度是设计规划阶段的一个重要方面。

评估复杂度可以从以下几个方面进行:

- **逻辑功能的分解**:将复杂的逻辑功能分解为若干个子功能,每个子功能由相对简单的逻辑门电路实现。例如,一个全加器可以被分解为半加器加上一个异或门电路。

- **模块化设计**:采用模块化设计有助于提高电路的可维护性和可扩展性。在本章的后续部分,我们还将详细讨论如何使用子电路来实现模块化设计。

- **电路优化**:利用逻辑代数和卡诺图等工具简化逻辑表达式,减少所需逻辑门的数量,这样可以降低电路复杂度并提高电路性能。

评估电路复杂度后,接下来是进行有效管理。管理复杂度主要依赖于良好的设计流程和文档记录。文档应记录设计的每一步骤,确保设计的可追溯性。此外,设计的测试和验证过程也应详细记录,这样可以快速定位并解决问题。

## 3.2 逻辑门电路的优化方法

### 3.2.1 减少逻辑门的数量

在逻辑门电路中,减少逻辑门的数量不仅有助于降低电路的成本,还可以提高电路的可靠性。优化的基本方法是通过逻辑简化来实现。逻辑简化的工具包括逻辑代数和卡诺图(Karnaugh Map)。

在进行逻辑代数简化时,我们应用诸如合并同类项、分配律、吸收律等基本代数规则。例如,对于逻辑表达式 A(B+C)+ABC,我们可以利用合并同类项和分配律将其简化为 AB。

```text

原表达式: A(B+C)+ABC

使用合并同类项: AB+AC+ABC

应用分配律: AB(1+C)+ABC

由于1+C总是为真,故可进一步简化为: AB

```

卡诺图简化则提供了一种视觉化的方法,通过图形化的方式识别可以合并的项,进而简化表达式。卡诺图在简化3变量或4变量的逻辑表达式时特别有用。

### 3.2.2 提高电路的运行速度

电路的运行速度受限于信号在逻辑门间传播的延迟。因此,优化的关键在于减少逻辑门的级数和减少单个逻辑门的负载。

减少逻辑门级数可以通过逻辑门电路的重排和重组来实现。例如,使用逻辑电路中的德摩根定律来重组表达式,有时可以达到减少逻辑级数的效果。同时,采用快速逻辑门,如具有较小传输延迟的门电路,也可以提高电路的运行速度。

### 3.2.3 降低电路的功耗

在便携式电子设备日益普及的今天,降低电路功耗显得尤为重要。在逻辑门电路设计中,可以通过以下策略来降低功耗:

- 减少不必要的逻辑门数量和负载。

- 使用CMOS(互补金属氧化物半导体)技术的逻辑门,因为CMOS电路在逻辑状态稳定时几乎不消耗功率。

- 在电路中引入时钟控制,通过关闭不活动电路部分的时钟信号来减少功耗。

## 3.2 逻辑门电路的优化方法的表格展示

| 优化目标 | 优化策略 | 具体措施 | 效果评估 |

| --- | --- | --- | --- |

| 减少逻辑门数量 | 逻辑代数简化 | 合并同类项、应用逻辑代数规则 | 减少组件数量 |

| | 卡诺图简化 | 识别并合并卡诺图中的项 | 减少逻辑级数 |

| 提高电路速度 | 减少逻辑级数 | 优化逻辑门顺序 | 减少信号传播时间 |

| | 减少负载 | 使用具有较少负载的逻辑门 | 提高电路响应速度 |

| 降低电路功耗 | 使用CMOS技术 | 使用CMOS门电路 | 减少静态功耗 |

| | 时钟控制 | 关闭不活动部分的

0

0