【存储组件建造者】:Logisim中触发器与寄存器的实践

发布时间: 2024-12-23 07:17:25 订阅数: 7

C#设计模式之建造者模式实例:各大佬打造取经人,观音找到光头的唐三藏和中分的悟空

# 摘要

本文首先介绍了Logisim软件及其在数字逻辑设计教学中的作用,特别关注了触发器的基础知识及其在Logisim中的设计与应用。接着,文章深入探讨了寄存器的工作原理、设计方法和性能优化,并展示了如何在Logisim中实践这些理论。第四章重点介绍了触发器和寄存器在构建复杂数字系统组件(如计数器和数据路径)中的应用,并提供了一个自定义存储组件的创新实验案例。最后,文章展望了触发器与寄存器在现代计算机架构中的应用以及Logisim在教育和研究领域的潜力,同时提出未来可能的功能改进方向。

# 关键字

Logisim;触发器;寄存器;数字逻辑设计;性能优化;教育应用

参考资源链接:[Logisim 实验二:运算器设计与头歌关卡实践](https://wenku.csdn.net/doc/2qo2ruw1tq?spm=1055.2635.3001.10343)

# 1. Logisim简介与触发器基础

Logisim 是一款功能强大的电路设计与模拟软件,它提供了一个直观的图形用户界面,允许用户轻松设计、测试和演示各种逻辑电路。对于 IT 专业人士和学生来说,Logisim 是一个学习和探索数字逻辑电路设计的理想工具,无论是基本的门电路还是复杂的微处理器系统。

## 1.1 触发器的基本概念

在数字电路中,触发器是存储数据的基本单元,它可以保存一个比特的二进制信息。它们在时钟信号的控制下工作,用于构建存储器、计数器等设备。触发器种类繁多,最基础的包括 D 触发器、T 触发器和 JK 触发器。

```mermaid

graph LR

A[触发器] --> B[D触发器]

A --> C[T触发器]

A --> D[JK触发器]

```

## 1.2 触发器的作用与重要性

理解触发器对于深入学习数字逻辑电路设计至关重要。它们是构成更大电路组件的基础,如寄存器和计数器,它们也是更高级数据处理单元的核心部件。掌握触发器的工作原理是构建高效、可靠数字系统的必备技能。

在下一章中,我们将深入探讨触发器在 Logisim 中的设计与应用,为您提供从基本到高级的触发器构建过程,以及如何测试和验证其功能的详细步骤。

# 2. ```

# 第二章:触发器在Logisim中的设计与应用

## 2.1 触发器的工作原理和分类

### 2.1.1 D触发器的设计原理

D触发器(Data Trigger)是数字电路中最常见的触发器类型之一,它能够存储一个位的信息。D触发器的设计原理涉及在时钟信号的上升沿或下降沿捕获输入D的值,并将其存储到输出Q上。

在Logisim中设计D触发器,首先需要放置一个时钟源,随后添加触发器组件。D触发器通过设置数据输入(D),输出(Q)以及时钟控制(Clock)来完成基本工作。一个典型的D触发器设计逻辑,可以在Logisim中通过以下步骤实现:

1. 打开Logisim程序。

2. 创建一个新的电路,选择合适的布局方式。

3. 从侧边栏中选择时钟组件,并将其放置在画布上。

4. 选择触发器组件,找到D触发器,并将其放置在画布上。

5. 将时钟组件连接到触发器的时钟输入端。

6. 添加输入和输出引脚,连接到D触发器的数据输入端(D)和输出端(Q)。

7. 测试触发器的功能,观察D输入和Q输出之间的关系。

在Logisim中进行仿真测试,可以观察到,当触发器的时钟输入从低电平跳变到高电平时,D触发器输出Q会捕获D输入端的值,并保持到下一个时钟周期。

### 2.1.2 T触发器和JK触发器的特点

T触发器(T Flip-Flop)和JK触发器是D触发器之外的其他两种常见触发器类型。它们各自具有独特的特性和应用场景。

- T触发器通常用于切换状态,即每当接收到一个时钟脉冲,输出就会从0变到1或从1变到0。T触发器在设计二进制计数器时非常有用。

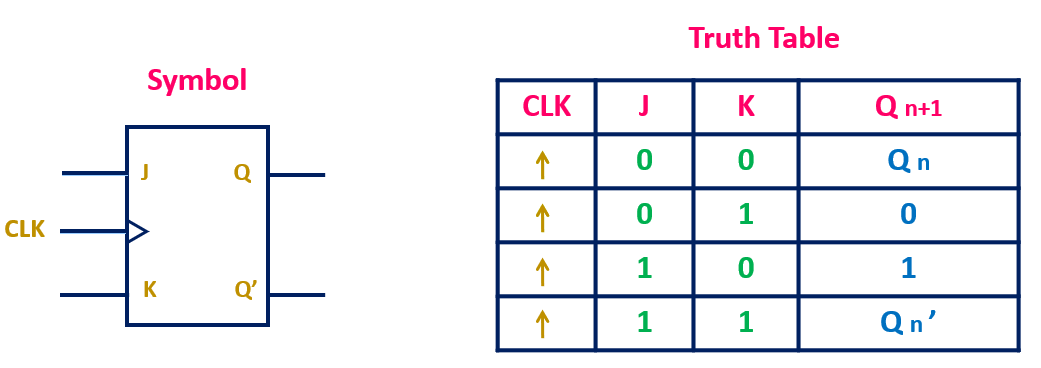

- JK触发器是最通用的触发器类型,它是T触发器和D触发器的扩展。JK触发器引入了两个输入(J和K),可以根据不同输入组合进行复位、置位或翻转操作。

在Logisim中设计T触发器和JK触发器,需要使用不同的逻辑门配置来实现它们的特殊行为。JK触发器通常通过D触发器前的额外逻辑来构建,而T触发器则可以通过连接D触发器的输入端到其反向输出(非Q)来创建。

## 2.2 触发器的构建过程

### 2.2.1 在Logisim中搭建基本D触发器

在Logisim中搭建基本D触发器的步骤相对简单。设计D触发器首先需要关注其内部逻辑结构。D触发器的关键在于如何在时钟信号的控制下,将数据输入端的值稳定地传递到输出端。以下是搭建基本D触发器的详细步骤:

1. 打开Logisim,创建一个新的电路文件。

2. 选择并放置一个时钟组件,设置好时钟参数。

3. 选择并放置一个D触发器组件。

4. 将时钟组件的输出连接到D触发器的时钟输入端(Clock)。

5. 添加两个输入引脚:一个标记为D,另一个标记为D的非(非D)。

6. 将输入引脚D连接到触发器的D输入端。

7. 将非D引脚连接到一个非门组件,再将该非门的输出连接回触发器的D输入端,形成一个反馈回路。

8. 添加一个输出引脚,标记为Q,连接到触发器的输出端。

9. 启动仿真,观察触发器的行为是否符合预期。

在搭建过程中,可以利用Logisim提供的多种工具来检查电路的正确性。通过反复切换时钟信号,检查输出端Q的值是否能正确地反映出输入端D的值。

### 2.2.2 高级触发器的构建技巧

构建高级触发器如JK触发器或T触发器时,需要更复杂的逻辑设计。高级触发器通常涉及到多个D触发器的组合以及额外的逻辑门电路。以下是构建JK触发器的步骤:

1. 在Logisim中,首先构建一个基本的D触发器。

2. 然后,添加两个额外的输入引脚,分别标记为J和K。

3. 使用与门(AND gates)和或门(OR gates)来创建J和K输入对D触发器的影响逻辑。

4. J和K的逻辑可以简单地表示为:如果J=1且K=1,则下一个状态为D触发器的反向输出;如果J=1且K=0,则下一个状态为1;如果J=0且K=1,则下一个状态为0;如果J=0且K=0,则保持当前状态不变。

5. 将这些逻辑门组合的输出连接到D触发器的D输入端。

6. 完成构建后,通过设置不同的J和K输入值,测试JK触发器的功能。

这种构建技巧利用了Logisim的灵活性,可以模拟复杂的数字逻辑设计。高级触发器的构建不仅增加了电路的复杂性,也为理解数字逻辑的高级概念提供了平台。

## 2.3 触发器的测试与验证

### 2.3.1 创建测试环境

为了测试与验证触发器的功能,在Logisim中需要创建一个合适的测试环境。测试环境的设计应该能够允许触发器在不同的输入条件下运行,并能够清晰地观察到输出结果。以下是创建测试环境的步骤:

1. 打开Logisim并载入之前搭建的触发器电路。

2. 选择“模拟”菜单,然后选择“分析”子菜单中的“逻辑分析仪”。

3. 在逻辑分析仪中,添加D触发器的输入和输出信号线路。

4. 将逻辑分析仪设置为

```

0

0