FPGA项目中的74LS160模拟指南:为何使用及如何操作

发布时间: 2024-12-21 16:35:27 阅读量: 4 订阅数: 9

FPGA开发实战指南:从入门到项目实现

# 摘要

本文旨在探讨在FPGA项目中使用74LS160计数器的实践和优势。首先,文章介绍了74LS160的基本功能与在FPGA中的应用背景,随后比较了其与其他现代数字集成电路的性能与适用性。第二章详细阐述了74LS160的基本操作原理,以及其在FPGA模拟实践中的步骤和代码实现。高级功能实现与优化方面,文章讨论了同步清零、使能控制、并行加载及计数模式的模拟,并提出了性能优化策略。最后,通过具体项目案例分析,本文展示了74LS160模拟在FPGA项目中的实际应用,并分享了项目执行过程中的教训与经验。本文为FPGA开发者提供了一个关于如何有效利用74LS160进行项目设计的全面参考。

# 关键字

FPGA;74LS160;硬件描述语言;模拟实践;性能优化;项目案例分析

参考资源链接:[74LS160: LSTTL同步十进制计数器(直接清零)详解](https://wenku.csdn.net/doc/4mu5vcjm4b?spm=1055.2635.3001.10343)

# 1. FPGA项目中的74LS160介绍

在数字电子设计的历史长河中,74LS160这一经典同步十进制计数器芯片,即便在现代FPGA(现场可编程门阵列)项目中,依然占有一席之地。本章节将简要介绍74LS160的基本功能,以及它在FPGA项目中的定位和作用。

## 1.1 74LS160简介

74LS160是一个4位的同步二进制计数器,它能够进行从0到9的十进制计数。它属于TTL(晶体管-晶体管逻辑)系列,广泛应用于70年代和80年代的数字电路设计中。尽管现代FPGA已经集成了更先进的计数器和状态机设计,但74LS160以其成熟、稳定的特性仍然在某些特定场合得到应用。

## 1.2 74LS160在FPGA中的应用

在FPGA设计中,虽然原生的74LS160硬件已不再直接使用,但其原理和功能在硬件描述语言(HDL)中能够被精确模拟。这种模拟可以为FPGA项目带来额外的灵活性和可重用性。下一章节将深入探讨为何在FPGA项目中还特别提及74LS160这一经典组件。

# 2. 为何在FPGA项目中使用74LS160

### 2.1 74LS160的应用背景

#### 2.1.1 FPGA项目的硬件需求分析

FPGA(现场可编程门阵列)项目通常要求硬件具有高度的可定制性、并行处理能力和高速的处理速度。在构建数字电路时,工程师往往需要使用各种计数器和寄存器来实现特定的逻辑功能。74LS160作为一款经典的同步十进制计数器,在FPGA项目中以其简洁的硬件设计和易于集成的特点,满足了这些需求。

它能够实现从0到9的十进制计数,并在达到最大值后循环回到0,这对于需要精确计数和时序控制的FPGA应用来说是非常有用的。74LS160还能通过简单的逻辑设计来实现诸如频率分频、脉冲序列生成等复杂功能,这些功能在FPGA项目中是十分常见的需求。

#### 2.1.2 74LS160的功能与优势

74LS160具备如下特点:

- 采用4位二进制计数,能够覆盖0到15的范围;

- 同步设计,所有输出端口在时钟信号的边沿同时更新;

- 可通过控制输入端实现计数器的启动、停止、同步清零以及并行加载;

- 具有输出使能端,可以在不改变计数器内容的情况下使输出保持稳定。

这些功能对于FPGA设计来说是极其实用的。例如,同步计数功能减少了因异步操作带来的不确定性,确保了整个系统的稳定性。同时,输出使能功能增加了输出信号控制的灵活性,便于设计者根据需要进行信号处理。

### 2.2 74LS160与其他硬件的对比

#### 2.2.1 与现代数字集成电路的对比

虽然74LS160是一款较早的集成电路,与现代的FPGA设计相比,其功能和性能已有所落后,但其简洁性和易于实现的特点在某些情况下仍有其独特优势。例如:

- **简洁性**:74LS160作为分立器件,能够简单地通过引脚连接实现功能,适合快速原型制作和小型项目。

- **成本效益**:由于其设计成熟,制造成本较低,对于成本敏感的项目而言,是理想的解决方案。

- **教育和学习工具**:在教学和自学硬件设计时,74LS160可以作为一个很好的工具,帮助理解数字逻辑和时序电路的基础。

#### 2.2.2 在FPGA项目中选择74LS160的理由

在特定的应用场景下,选择使用74LS160而不是FPGA内部资源的理由有:

- **资源优化**:在资源受限的FPGA中,使用74LS160可以释放FPGA内部的逻辑单元,用于其他更复杂的处理任务。

- **速度和效率**:74LS160的硬件设计可以提供比软件实现更高的速度和更高效的资源使用。

- **可靠性**:外置的硬件组件通常经过严格的测试,具备较高的可靠性,可以作为系统的关键部分提供稳定的计数和控制功能。

通过这些对比,我们不难发现,在追求简单快速开发、成本和资源优化的场合,74LS160仍然是一个值得考虑的选项。

# 3. 74LS160的基本操作和原理

## 3.1 74LS160的基本功能和引脚描述

### 3.1.1 74LS160的功能特点

74LS160 是一款 4 位同步十进制计数器,广泛应用于数字电路设计中。它具备同步清零、同步加载和使能功能,能够实现计数、分频和计时等操作。相较于异步计数器,同步计数器的响应速度更快,计数稳定,并且易于控制。

### 3.1.2 74LS160的引脚布局及功能

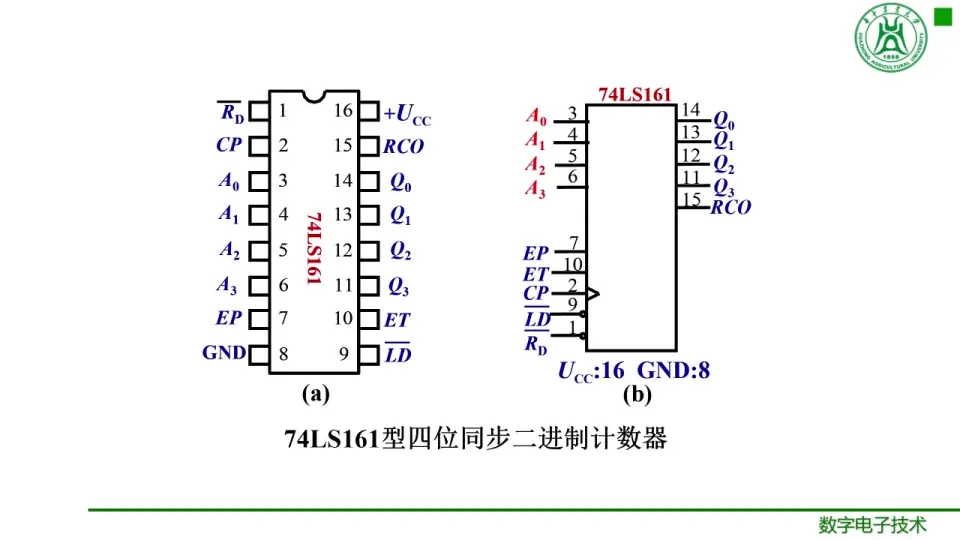

74LS160 的引脚定义如下:

- **P0 - P3(输入)**:并行数据输入端,用于同步加载计数值。

- **CLR(输入)**:高电平有效的同步清零端,用于将计数器清零。

- **LOAD(输入)**:高电平有效的同步加载端,用于载入并行数据。

- **ENT(输入)**:计数使能端,当该端为高电平时,计数器才可计数。

- **ENP(输入)**:另一个计数使能端,通常与 ENT 一起控制计数。

- **CLK(输入)**:时钟脉冲输入,上升沿触发计数。

- **Q0 - Q3(输出)**:二进制计数器的输出,用于输出当前计数值。

- **RCO(输出)**:进位输出,当计数器从 9 计数到 10 时输出高电平信号。

## 3.2 74LS160的工作原理

### 3.2.1 同步十进制计数器的工作机制

74LS160 工作在十进制模式下,其计数序列从 0 计数到 9,然后回到 0 并产生一个进位信号。计数器在时钟信号的每个上升沿检测使能信号

0

0