计数器大比拼:74LS160与其它计数器的终极选择攻略

发布时间: 2024-12-21 15:17:38 阅读量: 9 订阅数: 9

应用74LS160实现28进制计数器

# 摘要

数字计数器作为基础电子元件,在多种电子系统中发挥着关键作用。本文首先介绍了数字计数器的基本原理和应用,随后重点分析了74LS160计数器的内部结构、操作方法及性能参数,并将其与其他竞争计数器进行了详细比较。文章还探讨了计数器在现代电子系统中的应用,包括数字逻辑设计、通信系统及测试测量设备。最后,本文展望了74LS160的替代方案及其未来发展趋势,包括集成电路技术进步对计数器的影响以及技术创新可能带来的新方向。

# 关键字

数字计数器;74LS160;集成电路;应用案例;替代方案;技术创新

参考资源链接:[74LS160: LSTTL同步十进制计数器(直接清零)详解](https://wenku.csdn.net/doc/4mu5vcjm4b?spm=1055.2635.3001.10343)

# 1. 数字计数器的基本原理与应用

数字计数器是现代电子系统中不可或缺的组件,它通过计数脉冲信号的个数来进行时间测量、频率控制或数据统计等操作。在基本原理上,计数器通常由一系列的触发器组成,这些触发器在接收到时钟脉冲信号时改变其状态,从而实现计数功能。计数器的应用范围广泛,从简单的计数任务到复杂的系统时序控制,都能找到它们的身影。在实际应用中,计数器可以帮助实现定时器、频率分频、数据统计和排序等多种功能。本文将对数字计数器的基本原理进行阐述,并讨论其在实际应用中的多样性和灵活性。

# 2. 74LS160计数器详解

## 2.1 74LS160的内部结构与工作原理

### 2.1.1 逻辑电路组成

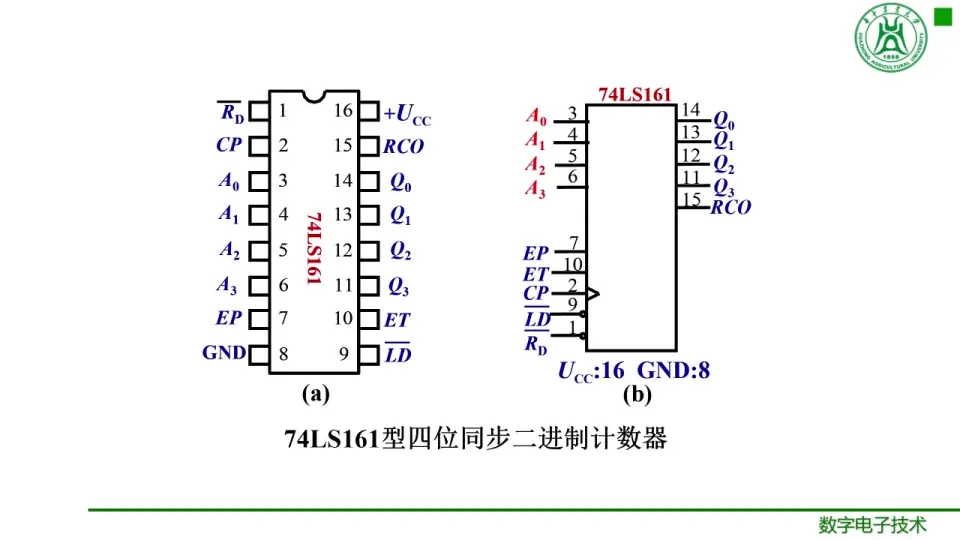

74LS160是一个4位的同步二进制计数器,含有同步清零和同步加载功能。其内部结构主要包括四个计数单元、一个时钟输入端、一个清零端、一个计数使能端、一个同步加载端和四个输出端。

每个计数单元是一个触发器,这些触发器通过特定的逻辑电路连接在一起,形成一个能够进行同步计数的系统。每个触发器有Q和Q非输出端,能够反映当前计数位的状态。当计数使能信号有效时,计数器在时钟脉冲的上升沿增加计数;而当同步清零信号有效时,计数器的所有输出立即清零。

逻辑电路的核心是四个触发器,它们通过与时钟信号、计数使能信号以及同步加载信号的组合逻辑,协调工作以实现计数功能。清零逻辑部分则是利用门电路实现对计数器的初始状态进行快速置零。

### 2.1.2 工作模式与特性

74LS160具有两种工作模式:计数模式和加载模式。在计数模式下,每个时钟脉冲会使计数器的状态增加一个单位;而在加载模式下,可以在一个时钟脉冲周期内将任意预设的值加载到计数器中。

74LS160的特性还包括其“进位输出”功能。当计数器从最大值溢出回到零时,进位输出端会输出一个脉冲信号,这个信号可以用于触发下一个更高位的计数器或者作为其他控制信号使用。

## 2.2 74LS160的操作方法与性能参数

### 2.2.1 引脚功能与配置

74LS160的引脚配置如下:

- **Vcc** 和 **GND**:分别为正电源和地线引脚。

- **P0-P3**:并行数据输入端,用于在同步加载时直接设置计数器的初始值。

- **CLR**:低电平有效的同步清零端,用于立即清零计数器。

- **LOAD**:低电平有效的同步加载端,用于将P0-P3的值同步加载到计数器中。

- **ENT** 和 **ENP**:计数使能端,当两个端均为高电平时,计数器才能计数。

- **CLK**:时钟输入端,上升沿触发。

- **RCO**:进位输出端,用于级联更高位的计数器或作为外部信号输出。

### 2.2.2 计数模式与触发方式

计数模式下,74LS160在**ENT**和**ENP**均为高电平时,根据时钟信号**CLK**的上升沿进行计数。计数器开始计数前,需要将**LOAD**置为高电平以使能计数器。

触发方式主要依赖于时钟信号,因为74LS160是上升沿触发的计数器,所以计数值的变化发生在时钟信号的上升沿。计数器的计数是同步进行的,意味着所有触发器的状态变化都在同一时刻完成,确保了计数的一致性和准确性。

### 2.2.3 电源与频率参数

74LS160工作电源电压一般在4.75V到5.25V之间,工作频率可以达到几兆赫兹。在供电条件下,需保证电源供应稳定,以避免产生噪声或其他干扰。

频率参数是计数器的重要性能指标,影响了计数器的最大计数速率。74LS160的典型计数速率可以在较高频率下稳定工作,但具体性能会受到供电电压、温度和其他电路条件的影响。

## 2.3 74LS160在数字电路中的应用案例

### 2.3.1 基本计数器应用

在基本计数器应用中,74LS160可以作为一个简单的频率计数器。例如,假设有一个方波信号源,通过控制**CLK**端可以将方波作为计数器的时钟信号输入,74LS160将会统计在一定时间内上升沿的次数。

```verilog

module freq_counter(

input clk_signal, // 输入信号

input clk, // 时钟信号

input reset, // 同步清零信号

input load, // 同步加载信号

input [3:0] preset, // 并行数据输入

output reg [3:0] count, // 计数器输出

output reg rco // 进位输出

);

always @(posedge clk or negedge reset) begin

if(!reset)

count <= 4'b0000; // 同步清零

else if(load)

count <= preset; // 同步加载

else if(ENP && ENT) begin

if(count == 4'b1111)

count <= 4'b0000; // 计数溢出时回零

else

count <= count + 1; // 正常计数

end

end

// 进位输出逻辑

assign rco = (count == 4'b1111) && ENP && ENT;

endmodule

```

### 2.3.2 与其他数字芯片的接口应用

74LS160可以与其他数字芯片如译码器、多路选择器等接口应用,以实现更复杂的逻辑功能。例如,可以使用74LS160作为地址生成器,生成连续的地址

0

0