CMOS门电路电源管理:权威指南与优化策略

发布时间: 2025-01-03 12:28:58 阅读量: 10 订阅数: 19

星之语明星周边产品销售网站的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

# 摘要

CMOS门电路作为集成电路设计的核心组件,其电源管理技术对于电路性能和功耗具有决定性影响。本文综述了CMOS门电路的理论基础,包括晶体管工作特性及门电路的逻辑功能与结构,深入探讨了电源消耗问题,涵盖了静态与动态功耗的来源、计算与优化方法。同时,本文分析了电源管理对电路性能的影响,特别是电源电压与电路速度的关系以及电源噪声对信号完整性的影响。实践部分介绍了电源管理的设计技巧、低功耗设计策略以及电源管理的模拟与仿真技术。案例分析章节展示了优化策略的理论基础及应用实例,并对成功的设计案例进行了评估。最后,本文展望了CMOS门电路在物联网、新型半导体材料、绿色电子和可持续发展方面的未来趋势,强调了能效标准在其中的重要作用。

# 关键字

CMOS技术;电源管理;功耗优化;性能影响;低功耗设计;模拟仿真

参考资源链接:[CMOS门电路解析:与非门与或非门的原理与版图](https://wenku.csdn.net/doc/iea7xrfo6a?spm=1055.2635.3001.10343)

# 1. CMOS门电路电源管理概述

随着集成电路的快速发展,CMOS(互补金属氧化物半导体)技术已成为现代电子设计的基石。CMOS门电路作为一种实现逻辑功能的基础元件,在电源管理方面扮演着至关重要的角色。电源管理不仅关系到电路的功耗和效率,还直接影响到电路的性能和可靠性。在设计CMOS门电路时,电源管理需要考虑多种因素,包括静态功耗、动态功耗以及电源电压对电路速度和信号完整性的影响。本章将为读者提供CMOS门电路电源管理的全面概述,为深入了解后续章节内容打下基础。

# 2. CMOS门电路的理论基础

## 2.1 CMOS技术的工作原理

### 2.1.1 CMOS晶体管的工作特性

CMOS(Complementary Metal-Oxide-Semiconductor)技术是现代集成电路中最为广泛使用的一种半导体技术。它依赖于两种类型的晶体管:n型MOS和p型MOS晶体管,它们在逻辑电路中互为补充。

n型MOS晶体管在阈值电压(Vth)以上时导电,而p型MOS晶体管则在Vth以下时导电。这种互补特性意味着在CMOS电路中,任何时刻只有一种类型的晶体管导通,从而实现了低静态功耗。

CMOS晶体管的工作特性可以通过其电流-电压(I-V)特性曲线来分析,这在设计和分析CMOS电路时至关重要。I-V曲线显示了晶体管的导通电流与两端电压之间的关系。在导通区域内,晶体管呈现低阻抗状态;而在截止区域内,则呈现高阻抗状态。

### 2.1.2 CMOS门电路的逻辑功能与结构

CMOS门电路由一个nMOS晶体管网络和一个pMOS晶体管网络组成,它们分别负责构建逻辑中的"真"和"假"路径。这些晶体管通过适当的布局和互联来实现各种逻辑功能,如与门(AND)、或门(OR)、非门(NOT)等。

CMOS逻辑门的基本结构通常包括一个输入逻辑部分和一个输出驱动部分。输入逻辑部分负责根据输入信号的逻辑状态调整晶体管的导通/截止状态,而输出驱动部分则在逻辑部分的基础上输出稳定的逻辑高或低电平。

一个简单的CMOS反相器(NOT门)由一个nMOS晶体管和一个pMOS晶体管组成,它们的源极分别接地和供电,漏极相连作为输出。当输入为逻辑高时,pMOS晶体管关闭,nMOS晶体管打开,输出为逻辑低;反之,当输入为逻辑低时,nMOS晶体管关闭,pMOS晶体管打开,输出为逻辑高。

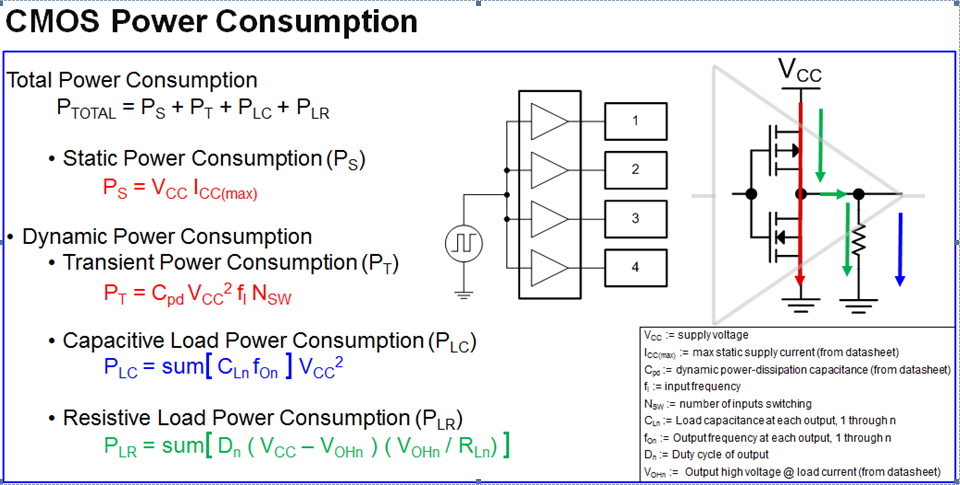

## 2.2 CMOS门电路的电源消耗

### 2.2.1 静态功耗的来源与计算

静态功耗(也称为漏电功耗)是在没有切换活动的静态条件下,CMOS电路消耗的功率。漏电功耗主要来源于晶体管的亚阈值漏电流和反型层漏电流。

亚阈值漏电流是指当MOS晶体管的栅源电压低于其阈值电压时仍然存在的漏电流。反型层漏电流是在晶体管导通时,由于源极和漏极间的势垒区而产生的电流。

静态功耗的计算涉及对电路中所有晶体管的漏电流进行求和。在实际的CMOS电路中,晶体管数量众多,因此,静态功耗的计算也相对复杂,需要借助电路仿真工具进行准确评估。

### 2.2.2 动态功耗的机理与优化方法

动态功耗发生在CMOS电路中的逻辑状态切换时。它主要由充放电电流引起,每当输出电容上的电荷被重新分布时,就会产生动态功耗。

动态功耗的表达式为 P = αCLOADVDD^2f,其中α代表活动因子,CLOAD为负载电容,VDD为电源电压,f为电路的工作频率。从这个表达式可以看出,动态功耗与电路的工作频率、电源电压的平方和负载电容成正比。

优化动态功耗的方法包括降低电源电压、减少负载电容、减少活动因子以及设计高效的时钟网络等。

## 2.3 电源管理对性能的影响

### 2.3.1 电源电压与电路速度的关系

电源电压直接影响CMOS电路中晶体管的开关速度,电压越高,晶体管的开关速度越快,从而使得电路的运行速度提高。但是,增加电源电压会增加功耗,尤其是在动态功耗方面。

电路速度和功耗之间的关系通常是折衷的,设计者必须在高速度与低功耗之间找到一个平衡点。在设计电源管理策略时,通常采用DVFS(Dynamic Voltage and Frequency Scaling)技术来动态调整电压和频率,以适应不同的工作负载。

### 2.3.2 电源噪声与信号完整性的分析

电源噪声是电源电压在电路中的变化,这会直接影响信号的完整性。由于信号路径中的电流变化,电源线上会产生电压降,从而引起噪声。

为了解决电源噪声问题,设计者会使用去耦电容(decoupling capacitors)和电源平面(power planes)来提供足够的电源和地平面,以减少电源线上的电阻和电感效应。通过仿真工具进行电源完整性分析,可以预测和解决可能出现的电源噪声问题。

| 参数 | 描述 |

| --- | --- |

| VDD | 电源电压 |

| CLOAD | 负载电容 |

| α | 活动因子 |

| f | 电路工作频率 |

| P | 功耗 |

接下来,我们将进一步探讨CMOS门电路电源管理的实践应用。

# 3. CMOS门电路电源管理实践

## 3.1 电源管理的设计技巧

### 3.1.1 电源线的布局与设计

在CMOS门电路设计中,电源线的布局与设计至关重要。它不仅关系到芯片的电源供应稳定性,还影响到电路的电磁兼容性和信号完整性。在设计过程中,需遵循以下原则:

- **最小化电阻和电感:

0

0