CMOS门电路功耗分析:揭秘与非门与或非门的功耗差异

发布时间: 2025-01-03 12:07:12 阅读量: 14 订阅数: 14

单片机与DSP中的MOS管与最简单CMOS逻辑门电路

# 摘要

CMOS门电路作为现代数字逻辑设计的基础,其功耗特性直接关系到集成电路的性能和能耗。本文首先概述了CMOS门电路的功耗问题,然后深入分析了与非门和或非门的静态和动态功耗原理。通过比较这两种基本逻辑门的功耗差异,探讨了各自在工程实践中的应用策略。进一步地,文章详细讨论了低功耗CMOS设计的技术手段,包括多阈值CMOS、体偏置技术和动态电压频率调整等高级低功耗技术。最后,对未来的CMOS技术发展趋势,特别是在材料科学和量子计算领域的潜在变革进行了展望,并探讨了CMOS技术在绿色计算和可持续发展中的作用。本文旨在为集成电路设计者提供深入的功耗管理知识,促进CMOS技术的绿色进步。

# 关键字

CMOS门电路;功耗分析;静态功耗;动态功耗;低功耗设计;绿色计算

参考资源链接:[CMOS门电路解析:与非门与或非门的原理与版图](https://wenku.csdn.net/doc/iea7xrfo6a?spm=1055.2635.3001.10343)

# 1. CMOS门电路功耗概述

随着集成电路的快速发展和小型化趋势,CMOS门电路的功耗管理已成为设计和优化过程中不可或缺的一部分。本章我们将从宏观层面概述CMOS门电路的功耗问题,为后续章节的深入分析打下基础。

## 1.1 CMOS门电路功耗的重要性

在芯片设计领域,功耗一直是影响集成电路性能和应用范围的关键因素之一。CMOS(互补金属氧化物半导体)技术因其在功耗管理方面的优越性能而成为主流。CMOS门电路在静态和动态情况下都会消耗能量,理解这些功耗的来源及降低它们的策略是提高芯片能效、延长电池寿命的重要步骤。

## 1.2 CMOS门电路功耗的构成

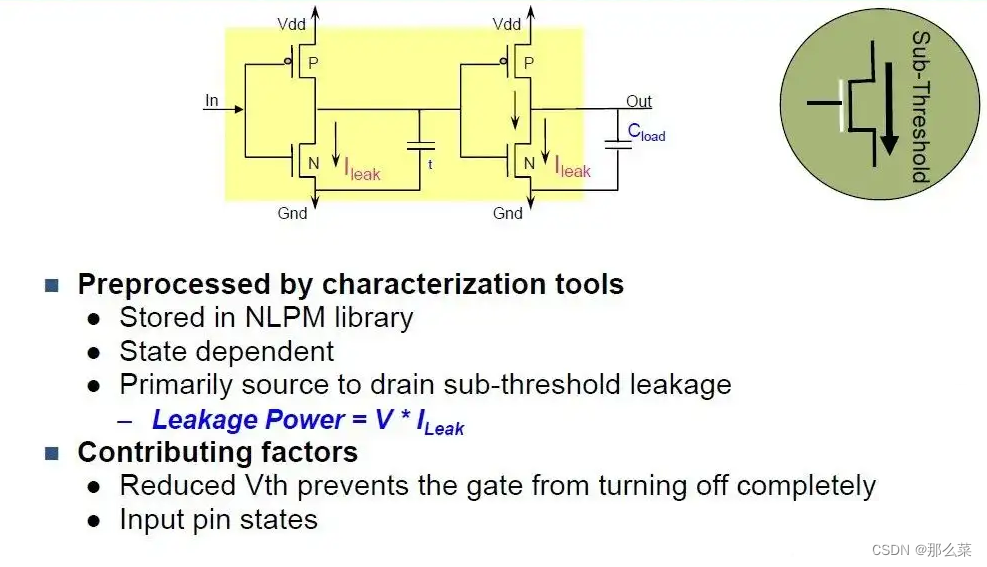

CMOS门电路的功耗主要由两部分组成:静态功耗和动态功耗。静态功耗在电路不工作时依然存在,它与晶体管的漏电流直接相关;动态功耗发生在开关操作时,与电路的开关频率、负载电容和电源电压等因素密切相关。

## 1.3 CMOS门电路功耗的影响因素

CMOS门电路的功耗受多个因素影响,包括制造工艺的精细程度、晶体管的尺寸、电路的工作频率、电源电压和负载条件等。为了有效管理功耗,设计者需要综合考虑这些因素,并根据应用场景选择合适的功耗优化策略。

## 1.4 本章小结

在本章中,我们简要介绍了CMOS门电路功耗的重要性、构成及其影响因素。接下来的章节将深入探讨与非门与或非门的功耗原理,并且分析如何优化这些功耗问题,确保在满足性能要求的同时,尽可能降低功耗。

# 2. 与非门的功耗原理

## 2.1 与非门电路结构与工作原理

### 2.1.1 与非门的基本电路组成

与非门(NAND gate)是数字逻辑电路中最基本的门电路之一,它主要由一系列的晶体管组成。在CMOS技术中,与非门通常由一对P型和N型MOSFET(金属-氧化物-半导体场效应晶体管)组成,这使得它们在逻辑"0"和"1"状态时可以实现几乎无功耗的状态。基本的与非门电路由两个N型MOSFET串联以及两个P型MOSFET并联组成。当输入端同时为高电平时,输出为低电平;如果输入端存在至少一个低电平,输出则为高电平。

为了深入理解与非门的工作原理,我们可以考虑以下简化的电路模型:两个输入端分别为A和B,输出端为Y。当A和B均处于高电平状态时,两个P型MOSFET关闭,两个N型MOSFET导通,形成低电平输出。反之,只要A或B中有一个是低电平,就会使一个P型MOSFET导通,两个N型MOSFET关闭,输出被拉高到高电平。

### 2.1.2 与非门的逻辑功能与实现

与非门的逻辑功能可以用其真值表来描述,当输入A和B均为1时,输出Y为0;在所有其他输入组合下,输出Y均为1。这可以用布尔代数表示为:Y = NOT (A AND B)。其逻辑功能可以用以下伪代码表示:

```

IF A AND B

THEN Y = 0

ELSE Y = 1

```

在实际电路实现中,与非门通过精确控制MOSFET的阈值电压和设计合适的栅极驱动电路来实现上述逻辑功能。与非门的这种基础逻辑构造使其成为构建其他复杂逻辑门电路的基础,它在数字电路设计中得到了广泛应用。

## 2.2 与非门的静态功耗分析

### 2.2.1 静态功耗的来源与影响因素

静态功耗,又称为漏电流功耗,是由于晶体管的静态特性引起的功耗。在与非门中,静态功耗主要来源于PMOS和NMOS晶体管在截止状态下的漏电流。尽管这种电流很小,但由于晶体管数量巨大且数量众多的门电路在现代集成电路中会同时并行工作,因此整体的静态功耗不容忽视。

影响静态功耗的主要因素包括:

1. 晶体管的物理尺寸

2. 阈值电压(Vth)

3. 工作温度

对于与非门而言,为了降低静态功耗,设计者通常会选用高阈值电压的晶体管,并通过优化晶体管的尺寸来减少漏电流。同时,在芯片制造过程中,采用更为先进的制程技术也是减少静态功耗的有效手段之一。

### 2.2.2 减少静态功耗的策略与方法

为了减少与非门的静态功耗,可以采用以下策略和方法:

1. **采用高阈值电压晶体管**:提高晶体管的Vth可以显著降低其在截止状态下的漏电流。

2. **多阈值电压技术**:设计不同Vth的晶体管应用于电路的不同部分,高Vth晶体管用于逻辑状态不频繁变化的部分,而低Vth晶体管用于对速度要求较高的部分。

3. **功率门控技术**:通过在晶体管级添加电源控制电路,在与非门不活跃时切断电源,从而减少漏电流。

4. **优化晶体管尺寸**:合理设计晶体管的尺寸可以平衡速度与功耗之间的关系,防止过度设计造成的功耗增加。

5. **使用先进的制程技术**:随着半导体工艺的进步,晶体管的尺寸不断缩小,这有助于减少漏电流,从而减少静态功耗。

通过实施上述措施,可以有效降低与非门的静态功耗,并提高集成电路的整体能效。

## 2.3 与非门的动态功耗分析

### 2.3.1 动态功耗的产生机制

与非门的动态功耗是指在电路开关过程中,电路节点充放电造成的功耗。动态功耗的大小与电路负载电容、输入信号的频率和电路中电压摆幅直接相关。与非门在开关过程中,输入信号的变化会引起电容的充放电,每次充放电都伴随着能量的消耗。

具体来说,当输入信号改变时,晶体管交替导通或截止,由于电路存在寄生电容,比如输入电容、输出电容和互连电容等,这些电容上的电荷需要被充放电,而这个充放电过程就会消耗能量。

### 2.3.2 动态功耗优化的技术探讨

为了减少与非门的动态功耗,可以采取如下技术措施:

1. **降低工作电压**:降低电源电压可以减少每次充放电过程中的能量消耗,从而减少动态功耗。

2. **优化电路设计**:通过电路设计优化,可以减少电路中负载电容的大小。例如,通过合理布局和布线,可以减小互连电容。

3. **电源门控技术**:在非活动周期关闭电源,减少无效的充放电过程。

4. **多阈值电压CMOS技术**:如前所述,使用高Vth晶体管可以减少静态功耗,但也可以降低电路的开关速度,从而减少动态功耗。

5. **使用

0

0