Quartus II仿真中的信号完整性分析:确保设计质量的高级策略

发布时间: 2024-12-27 08:50:20 阅读量: 6 订阅数: 9

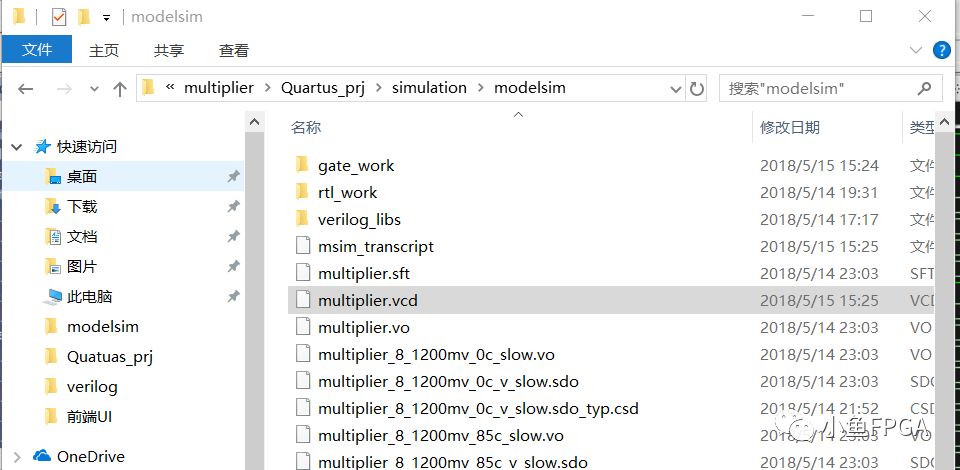

Quartus II 18.0 基于Modelsim仿真快速入门

# 摘要

本文对信号完整性基础知识进行了回顾,并详述了在Quartus II仿真环境下搭建实验平台的步骤。通过深入分析信号完整性问题产生的原因和分类,建立了理论模型,并探讨了仿真参数的配置与优化方法。文章重点介绍了信号完整性仿真工具的选择与配置,以及在时序分析、串扰、反射以及电源和地线完整性分析中应用的具体方法。此外,探讨了多层次信号完整性优化、设计迭代与仿真验证,以及集成电路制造过程中信号完整性的重要性与监控方法。本文旨在为电子工程领域的研究人员和工程师提供系统性的信号完整性分析和优化策略,帮助他们更有效地应对复杂电路设计中遇到的信号完整性挑战。

# 关键字

信号完整性;Quartus II;时序分析;串扰;反射;电源地线设计

参考资源链接:[Quartus_II教程:设置仿真时间和输入信号波形](https://wenku.csdn.net/doc/5tmcw8qvz2?spm=1055.2635.3001.10343)

# 1. 信号完整性基础知识回顾

在当今高速电子系统设计中,信号完整性(Signal Integrity,简称SI)已经成为不可忽视的因素之一。信号完整性指的是在高速电路和系统中,电信号能以预期的特性准确传输,不出现失真和干扰,是保证电子设备稳定运行的前提。

## 1.1 信号完整性的重要性

随着集成电路的工作频率不断提高,电子设备的尺寸持续减小,信号传输速度加快,对信号质量提出了更高的要求。良好的信号完整性可以减少误码率,提高系统的可靠性,降低功耗,延长设备寿命。

## 1.2 基本概念

信号完整性涉及的概念包括但不限于反射(Reflection)、串扰(Crosstalk)、电源/地线噪声(Power/Ground Noise)和时序(Timing)问题。这些因素共同决定了信号在电路板上的传播质量。

## 1.3 简单实例

举例来说,当高速数字信号在PCB(印制电路板)上通过一条导线传输时,由于导线电感和电阻的存在,信号在传输线上会引起反射。如果电路设计不当,这些反射信号有可能与原始信号叠加,导致信号失真,影响信号质量。

信号完整性问题的解决不仅需要扎实的理论基础,还需配合专业仿真工具和严格的测试验证。随着本章内容的深入,我们将逐步展开讨论信号完整性问题的理论基础、仿真工具的使用,以及解决策略的实践应用。

# 2. Quartus II仿真环境的搭建

## 2.1 Quartus II软件介绍与安装

Quartus II是由Altera公司(现为Intel旗下)开发的一款专业的FPGA和CPLD集成电路设计软件,广泛应用于电子工程领域。它支持设计输入、综合、仿真、定时分析、布局布线、器件配置以及验证整个设计流程。为了进行信号完整性的仿真分析,首先需要在计算机上安装Quartus II软件。

在安装Quartus II之前,需要确保计算机满足软件的系统要求,包括操作系统、内存、存储空间以及必要的驱动程序和依赖库。安装过程一般遵循以下步骤:

1. 从Altera官方网站下载Quartus II安装包。

2. 双击安装程序,开始安装向导。

3. 选择安装路径,确认同意许可协议。

4. 在组件选择界面中,根据需要选择合适的组件进行安装,如仿真工具ModelSim-Altera。

5. 点击“Next”,等待安装进度条完成。

6. 安装完成后,重启计算机以确保所有组件正常工作。

## 2.2 创建Quartus II项目

创建项目是开始任何设计流程的基础步骤。以下是创建Quartus II项目的步骤:

1. 打开Quartus II软件。

2. 在主界面上点击“File”菜单,选择“New Project Wizard”。

3. 按照向导指示,填写项目名称和位置。

4. 选择目标设备,即要将设计下载到的FPGA或CPLD芯片型号。

5. 选择项目类型,例如VHDL、Verilog HDL或Block Diagram/Schematic File等。

6. 最后,确认向导信息,点击“Finish”完成项目创建。

## 2.3 项目设计输入

设计输入是将设计意图转化为Quartus II能够理解的形式。可以采用多种方式来输入设计,如使用图形化的设计输入工具(如Block Diagram/Schematic Editor),也可以使用硬件描述语言(如VHDL或Verilog HDL)编写代码。例如,使用Verilog HDL编写一个简单的2输入与门(AND gate)代码如下:

```verilog

module and_gate(input a, input b, output c);

assign c = a & b;

endmodule

```

编写完成后,需要将设计文件添加到项目中。按照以下步骤操作:

1. 在Quartus II中点击“File”菜单,选择“New”创建一个新的设计文件。

2. 选择文件类型,如Verilog HDL File或VHDL File。

3. 编写或粘贴设计代码到文件中。

4. 保存文件,并将其添加到当前项目中(通过“Project Navigator”中的“Files”标签页)。

## 2.4 编译和构建项目

编译是将设计文件转换为可编程文件的过程,对于后续仿真和硬件实现都是必要的一步。按照以下步骤进行编译:

1. 在Quartus II中,点击“Processing”菜单,然后选择“Start Compilation”。

2. 等待编译过程完成,Quartus II会提供编译日志,显示编译过程中是否有错误或者警告。

3. 如果编译失败,需要根据日志中的提示修改设计文件,然后重新编译。

4. 成功编译后,可以在“Project Navigator”中查看项目文件和编译生成的其他文件,如网表文件、仿真模型等。

## 2.5 Quartus II仿真环境的配置

Quartus II支持多种仿真方法,包括内置的仿真工具和第三方仿真工具的集成。对于信号完整性分析,需要配置好仿真环境,并准备相应的测试台(testbench)。

1. 在Quartus II中,点击“Tools”菜单,选择“Run Simulation Tool”然后选择“RTL Simulation”或“Post-Fit Simulation”。

2. 如果使用ModelSim-Altera,需要配置ModelSim-Altera路径,Quartus II默认会自动检测安装路径。

3. 创建测试台文件,测试台文件是一个仿真文件,用于定义测试输入信号,并观察输出结果。

4. 在测试台文件中,编写激励代码(Stimulus code),用于生成所需的测试信号。

下面是一个简单的测试台代码示例:

```verilog

module and_gate_tb;

// 测试台信号声明

reg a, b;

wire c;

// 实例化待测试模块

and_gate uut(.a(a), .b(b), .c(c));

// 测试台任务

initial begin

// 初始化输入

a = 0; b = 0;

// 应用输入序列并观察输出

#10 a = 0; b = 1;

#10 a = 1; b = 0;

#10 a = 1; b = 1;

// 结束测试

#10 $stop;

end

endmodule

```

## 2.6 进行仿真并分析结果

仿

0

0