Altium ROOM DDR内存布线高级指南

发布时间: 2024-12-06 12:59:55 阅读量: 9 订阅数: 14

参考资源链接:[五步走 Altium ROOM 详细使用说明及其规则设置](https://wenku.csdn.net/doc/6412b516be7fbd1778d41e73?spm=1055.2635.3001.10343)

# 1. 高速内存技术与DDR标准概述

## 1.1 内存技术的演进

自从个人计算机问世以来,内存技术经历了从最初的DRAM到DDR、DDR2、DDR3、DDR4,乃至最新一代的DDR5的演进。这一过程中,内存的速度、带宽以及效率不断提升,以适应日益增长的性能需求。现代内存技术,特别是DDR(Double Data Rate)系列,已成为构建高速计算系统不可或缺的组件。

## 1.2 DDR标准的革新

DDR内存之所以能够成为主流,与其创新的数据传输方式密切相关。DDR标准以双倍数据速率传输数据,即在一个时钟周期内进行两次数据传输。这一改进大幅提高了内存的数据吞吐率,大大提升了计算机系统的整体性能。随着技术的发展,新的DDR标准不断涌现,每一代标准都具有更高的频率、更宽的数据带宽以及更优的电源效率。

## 1.3 DDR内存的应用领域

DDR内存因其高速性能,被广泛应用于各种计算密集型领域,包括服务器、高性能计算、游戏设备、移动设备等。随着物联网(IoT)设备的普及,以及5G技术的推动,对DDR内存性能的要求日益提高,推动了DDR技术的持续创新。高容量、高性能的DDR内存技术是当前和未来IT行业的关键支撑技术之一。

## 1.4 本章小结

在本章中,我们回顾了内存技术的演进历程,特别是DDR标准的发展和革新,并展望了其在现代IT领域的应用。接下来的章节中,我们将深入探讨DDR内存的技术细节以及在实际设计中的应用,为读者带来更丰富、深入的理解。

# 2. DDR内存布线理论基础

在现代电子系统设计中,DDR内存布线是实现高性能内存通信的关键步骤。本章节将深入探讨DDR内存布线的理论基础,包括其工作原理、布线设计的基本要求以及信号传输理论。

## 2.1 DDR内存的工作原理

### 2.1.1 DDR内存架构

DDR(双倍数据速率)内存是目前广泛使用的内存技术之一,其通过在时钟的上升沿和下降沿同时传输数据来提高数据传输速率。与传统SDR(单倍数据速率)内存相比,DDR内存可以在相同的时钟频率下,实现双倍的数据传输速率。

**核心组件:**

- 数据接口:包括数据总线、地址总线和控制信号。

- 内部逻辑:包含数据重排逻辑、命令解码和时钟管理。

- 信号引脚:用于数据传输、时钟、控制和电源等信号的接口。

**工作模式:**

- 激活模式(Active):读写操作前的准备阶段。

- 预充电模式(Precharge):完成数据传输后,关闭行地址并准备下一次激活。

- 自刷新模式(Self Refresh):内存在低功耗状态下的自我刷新过程。

### 2.1.2 信号完整性基础

信号完整性关注在高速信号传输过程中,信号的波形质量是否满足系统要求。为了保证信号的完整性,必须考虑以下几个方面:

**信号衰减:**随着信号沿传输线路传播距离的增加,信号幅度会逐渐衰减。通过布线设计中采用适当的线宽和线间距,以及使用高介电常数的介质材料,可以减少信号衰减。

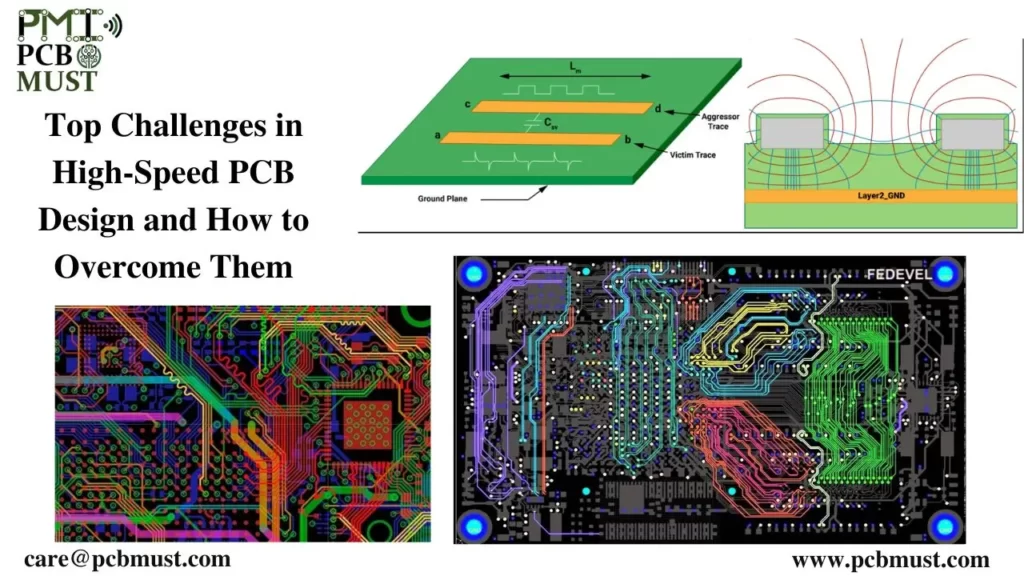

**串扰:**当一条传输线上的信号变化时,会在邻近的传输线上感应出电压,这就是串扰。适当的布线布局和线间距可以减少串扰。

**反射:**当信号在传输线终端遇到不匹配的阻抗时,会发生反射。阻抗匹配是减小反射的关键。

## 2.2 DDR布线设计的基本要求

### 2.2.1 时序和抖动控制

在高速内存系统中,时序的准确性和抖动的控制至关重要。DDR布线时,必须确保所有信号线上的传输时延匹配,以及整体布线满足内存规格书中的时序要求。

**时序分析:**

- 建立时间(Tsu):数据必须在时钟边沿之前稳定的时间。

- 保持时间(Th):数据必须在时钟边沿之后保持稳定的时间。

**抖动控制:**

- 时钟抖动:由于时钟信号不稳定导致的时间偏差。

- 数据抖动:由于数据信号不稳定导致的时间偏差。

### 2.2.2 电源和地线设计

为了保证内存系统的稳定性和性能,电源和地线的布线设计同样重要。

**电源平面和地平面:**应尽可能使用大面积的电源平面和地平面,以降低电源系统的阻抗并提高抗干扰能力。

**电源和地线的布局:**电源线和地线应靠近信号线布局,以提供有效的回流路径,减少电磁干扰。

## 2.3 DDR布线的信号传输理论

### 2.3.1 差分信号传输

DDR内存系统中常用差分信号传输技术,它通过成对的线路传输一个信号,一个线路传输正信号,另一个传输反信号。这种技术可以提高信号的抗干扰能力,增强传输的可靠性。

**差分信号的优势:**

- 抗干扰能力更强。

- 更好的抑制共模干扰。

- 高速传输下减少串扰。

### 2.3.2 阻抗匹配和反射问题

阻抗匹配是信号完整性的基础。阻抗的不匹配会导致信号反射,从而引起数据传输错误和系统不稳定。

**阻抗计算:**

阻抗的计算通常基于传输线的特性阻抗,需要考虑传输线的物理结构、介质材料以及线路周围的环境。

**解决反射问题:**

- 在信号源端和接收端使用终端匹配电阻。

- 使用阻抗匹配层。

- 优化信号的上升时间以减少反射。

在下一章节中,我们将深入 Altium Designer 这一工具在 DDR 内存布线中的应用与实践,如何将这些理论知识转化为实际的设计操作。

# 3. Altium Designer中的DDR布线实践

## 3.1 Altium Designer软件的布局布线准备

### 3.1.1 设计规则设置

在Altium Designer中进行DDR布线之前,合理的布局布线规则设置是至关重要的。设计规则是Altium Designer内一组用于指导PC

0

0