STM32管脚高级应用探索:解锁STM32管脚更多可能性,拓展应用场景

发布时间: 2024-07-03 05:08:41 阅读量: 75 订阅数: 39

# 1. STM32管脚基础**

**1.1 管脚功能介绍**

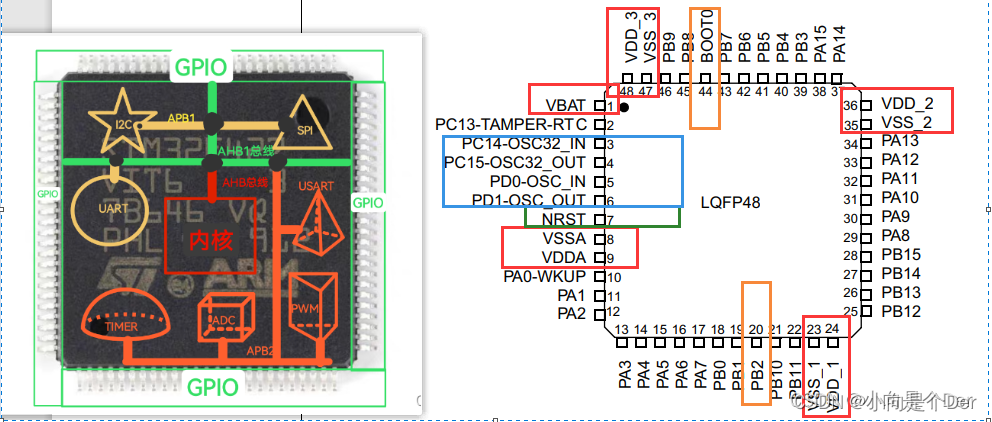

STM32微控制器拥有丰富的管脚资源,每个管脚都具有多种功能,包括:

* **通用输入/输出 (GPIO)**:可配置为输入或输出,用于连接外部设备或控制外围器件。

* **复用功能**:可配置为执行特定功能,如定时器、串行通信或模拟输入/输出。

* **中断触发**:可配置为在特定事件(如管脚状态变化)时触发中断。

**1.2 管脚配置与控制**

STM32管脚配置和控制通过寄存器进行,每个管脚都有对应的寄存器来设置其模式、速度和中断触发条件。

```c

// 设置管脚 PA0 为输出模式

GPIOA->MODER &= ~(3 << (0 * 2));

GPIOA->MODER |= (1 << (0 * 2));

// 设置管脚 PA0 为高电平

GPIOA->ODR |= (1 << 0);

```

# 2. 管脚高级配置技巧

STM32管脚除了基本的配置和控制功能外,还提供了一系列高级配置技巧,可以进一步拓展管脚的应用场景和可能性。本章将深入探讨管脚复用和多路复用、管脚中断和事件触发、管脚模拟功能与ADC/DAC以及管脚时序控制与定时器等高级配置技巧。

### 2.1 管脚复用和多路复用

管脚复用是指一个物理管脚可以映射到多个功能。例如,STM32的PA0管脚既可以作为GPIO,也可以作为USART1的TX引脚。管脚复用允许一个管脚同时服务于多个外设,从而节省宝贵的I/O资源。

多路复用是一种特殊的管脚复用形式,它允许一个管脚在多个功能之间动态切换。例如,STM32的PB10管脚可以多路复用为GPIO、USART3的TX引脚或I2C1的SCL引脚。多路复用提供了极大的灵活性,允许在运行时根据需要更改管脚的功能。

**代码示例:**

```c

/* 配置PA0管脚为USART1的TX引脚 */

RCC->APB2ENR |= RCC_APB2ENR_USART1EN;

GPIOA->CRH &= ~(GPIO_CRH_MODE0 | GPIO_CRH_CNF0);

GPIOA->CRH |= GPIO_CRH_MODE0_1 | GPIO_CRH_CNF0_1;

/* 配置PB10管脚为GPIO */

RCC->APB2ENR |= RCC_APB2ENR_IOPBEN;

GPIOB->CRH &= ~(GPIO_CRH_MODE10 | GPIO_CRH_CNF10);

GPIOB->CRH |= GPIO_CRH_MODE10_0 | GPIO_CRH_CNF10_0;

```

**逻辑分析:**

* 第一段代码配置PA0管脚为USART1的TX引脚。首先使能USART1时钟,然后清除PA0管脚的模式和配置位,最后设置PA0管脚为复用模式,配置为USART1的TX引脚。

* 第二段代码配置PB10管脚为GPIO。首先使能GPIOB时钟,然后清除PB10管脚的模式和配置位,最后设置PB10管脚为普通输入/输出模式。

### 2.2 管脚中断和事件触发

管脚中断和事件触发允许管脚在特定事件发生时产生中断或触发事件。例如,STM32的PC13管脚可以配置为在外部中断上升沿产生中断,或者在定时器2溢出时触发事件。

**中断示例:**

```c

/* 配置PC13管脚为外部中断上升沿触发中断 */

RCC->APB2ENR |= RCC_APB2ENR_SYSCFGEN;

SYSCFG->EXTICR[3] &= ~SYSCFG_EXTICR4_EXTI13;

SYSCFG->EXTICR[3] |= SYSCFG_EXTICR4_EXTI13_PC;

EXTI->IMR |= EXTI_IMR_MR13;

EXTI->RTSR |= EXTI_RTSR_TR13;

NVIC_EnableIRQ(EXTI15_10_IRQn);

```

**逻辑分析:**

* 该代码配置PC13管脚为外部中断上升沿触发中断。首先使能SYSCFG时钟,然后将PC13管脚映射到外部中断线13,再使能外部中断线13的中断和上升沿触发,最后使能外部中断15-10中断。

**事件触发示例:**

```c

/* 配置PA0管脚为定时器2溢出事件触发 */

RCC->APB1ENR |= RCC_APB1ENR_TIM2EN;

TIM2->CR1 &= ~TIM_CR1_CEN;

TIM2->PSC = 7200 - 1;

TIM2->ARR = 1000 - 1;

TIM2->EGR |= TIM_EGR_UG;

TIM2->DIER |= TIM_DIER_UDE;

```

**逻辑分析:**

* 该代码配置PA0管脚为定时器2溢出事件触发。首先使能定时器2时钟,然后停止定时器,设置定时器预分频器和自动重装载寄存器,再触发更新事件,最后使能溢出事件中断。

### 2.3 管脚模拟功能与ADC/DAC

STM32管脚还支持模拟功能,可以连接到ADC和DAC外设。例如,STM32的PA0管脚可以配置为模拟输入,连接到ADC1通道1,或者配置为模拟输出,连接到DAC1通道1。

**ADC示例:**

```c

/* 配置PA0管脚为ADC1通道1模拟输入 */

RCC->APB2ENR |= RCC_APB2ENR_ADC1EN;

ADC1->CR2 &= ~ADC_CR2_ADON;

ADC1->SQR1 &= ~ADC_SQR1_L;

ADC1->SQR1 |= ADC_SQR1_SQ1_0;

ADC1->CR2 |= ADC_CR2_ADON;

```

**逻辑分析:**

* 该代码配置PA0管脚为ADC1通道1模拟输入。首先使能ADC1时钟,然后关闭ADC,清除通道选择寄存器,再将PA0管脚映射到通道1,最后开启ADC。

**DAC示例:**

```c

/* 配置PA0管脚为DAC1通道1模拟输出 */

RCC->APB1ENR |= RCC_APB1ENR_DACEN;

DAC->CR &= ~DAC_CR_EN1;

DAC->SWTRIGR |= DAC_SWTRIGR_SWTRIG1;

DAC->DHR12R1 = 0x0FFF;

DAC->CR |= DAC_CR_EN1;

```

**逻辑分析:**

* 该代码配置PA0管脚为DAC1通道1模拟输出。首先使能DAC时钟,然后关闭DAC,设置触发软件触发更新,再设置输出数据寄存器,最后开启DAC。

### 2.4 管脚时序控制与定时器

STM32管脚还可以用于时序控制,通过连接到定时器外设。例如,STM32的PA0管脚可以配置为定时器2的输出比较通道1,用于产生PWM波形。

**PWM示例:**

```c

/* 配置PA0管脚为定时器2输出比较通道1 */

RCC->APB1ENR |= RCC_APB1ENR_TIM2EN;

TIM2->CR1 &= ~TIM_CR1_CEN;

TIM2->PSC = 7200 - 1;

TIM2->ARR = 1000 - 1;

TIM2->CCR1 = 500;

TIM2->CCMR1 &= ~TIM_CCMR1_OC1M;

TIM2->CCMR1 |= TIM_CCMR1_OC1M_1 | TIM_CCMR1_OC1M_2;

```

0

0