探索CDL网表导出原理图:原理图与逻辑验证的综合应用

发布时间: 2024-12-03 15:24:14 阅读量: 13 订阅数: 17

参考资源链接:[Virtuoso中CDL网表导入反相器电路详解及步骤](https://wenku.csdn.net/doc/6412b79cbe7fbd1778d4aeaa?spm=1055.2635.3001.10343)

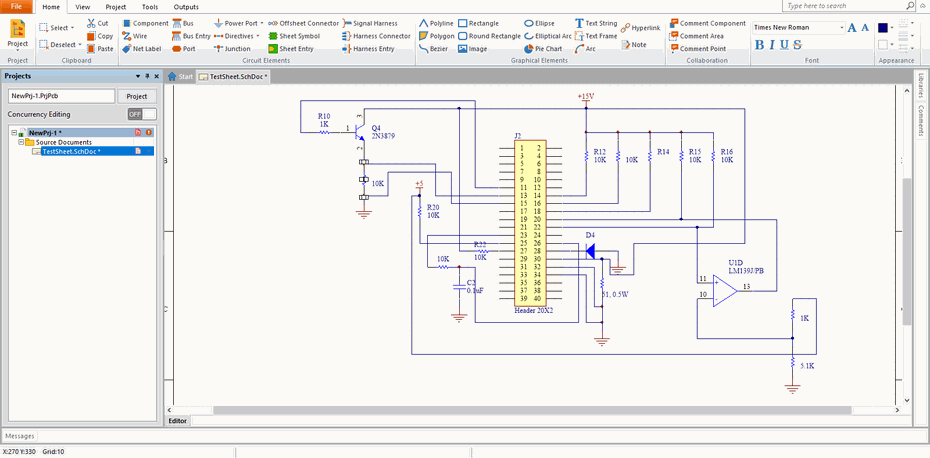

# 1. CDL网表导出原理图概述

在电子设计自动化(EDA)的世界里,CDL网表导出原理图是连接抽象电路设计与实际物理实现的关键步骤。CDL(Circuit Description Language)网表是一种用于描述电路连接关系的文本格式,它为电路设计的后续步骤,如布局布线和仿真测试提供了基础数据。

本章将概述CDL网表的基本概念,同时为读者揭示其在电路设计流程中的重要性。我们将探索从原理图转换到CDL网表的基本过程,并讨论该转换对于电路设计验证和优化的意义。此外,本章还将简要介绍CDL网表导出原理图的工具和技术,为后续章节中深入分析和实际操作打下坚实的基础。

随着对CDL网表导出原理图的理解加深,读者将能够掌握如何有效地利用这一关键步骤来提升电路设计的质量和效率。

# 2. CDL网表的基础知识

## 2.1 CDL网表的定义和作用

### 2.1.1 什么是CDL网表

CDL(Circuit Description Language)是一种用于描述电子电路的硬件描述语言,它能够以文本形式精确地表示电路的连接关系和元件属性。CDL网表通常被用于在集成电路设计中作为原理图和硬件描述语言之间的桥梁,以及在不同设计工具之间进行数据交换。

CDL网表的一个关键优势在于它的可读性和可维护性。与二进制格式的网表相比,CDL网表更容易被工程师理解和编辑,这对于电路的后期调试和维护具有重要意义。此外,由于它是一种标准化的格式,CDL网表可以在各种EDA(Electronic Design Automation)工具之间无缝转换,确保设计的兼容性和灵活性。

### 2.1.2 CDL网表在电路设计中的重要性

在现代电子设计自动化领域,CDL网表的主要作用体现在以下几个方面:

1. **设计数据交换**:CDL网表作为一种开放标准,可以被多数EDA工具所支持,使得不同的设计数据能够跨平台传输。

2. **原理图和网表互转**:设计师可以在原理图与CDL网表之间相互转换,方便进行设计的可视化和逻辑验证。

3. **设计验证**:通过将CDL网表导入仿真器,可以进行逻辑仿真,以验证电路设计是否满足功能和性能要求。

4. **后期优化和调试**:在电路的后续优化和调试阶段,工程师可以修改CDL网表来改变电路连接和元件参数,从而优化电路性能。

## 2.2 CDL网表的结构和组成

### 2.2.1 网表的基本语法和格式

CDL网表文件通常由一系列的语句组成,每个语句代表电路中的一个元件或者连接。基本的CDL网表格式遵循以下语法:

- **元件定义**:以关键字 `instance` 开始,后面跟元件名称,例如 `instance u1 AND2X1`。

- **端口连接**:使用 `net` 关键字定义电路的连接,如 `net vdd`。

- **属性赋值**:元件的属性(例如电源电压、扇出负载等)可以在定义元件时指定,如 `param vdd=5v`。

一个简单的CDL网表示例如下:

```

instance u1 AND2X1

net vdd

net gnd

net input1

net input2

net output

connection u1, 1, input1

connection u1, 2, input2

connection u1, 3, gnd

connection u1, 4, vdd

connection u1, 5, output

```

### 2.2.2 网表中的关键元素和特性

CDL网表中的关键元素包括元件实例、网络(net)、连接、参数和属性等。这些元素共同构成了电路的完整描述:

- **元件实例(Instance)**:表示原理图中的一个元件,如门电路、电阻、电容等。

- **网络(Net)**:表示电路中的连接线,用于连接元件的各个端点。

- **连接(Connection)**:表示元件实例和网络之间的物理连接关系。

- **参数(Param)**:用于定义元件实例的特定属性,如电源电压、温度系数等。

- **属性(Attribute)**:元件的额外描述信息,可能包括逻辑级别、扇出负载等。

通过这些关键元素的精确描述,CDL网表能够完整地表达电路的设计意图和功能,为电路设计和验证提供支持。

## 2.3 CDL网表的生成过程

### 2.3.1 从原理图到网表的转换流程

将原理图转换为CDL网表是一个将设计信息进行编码的过程,通常涉及以下步骤:

1. **原理图绘制**:首先使用EDA工具绘制电路原理图,此时设计以图形化的方式展现。

2. **生成内部网表**:EDA工具根据原理图自动生成内部网表,这个过程往往是自动的并且对用户不可见。

3. **转换为CDL格式**:将内部网表转换为CDL网表格式,这个过程中可能涉及到格式调整和优化。

4. **审查和修改**:生成的CDL网表需要被设计师审查,确认无误后才能用于后续的仿真和验证。

这一过程可以使用诸如Cadence Design Systems、Altera Quartus II等专业EDA工具来完成,它们提供了将原理图导出为CDL网表的选项,并支持进一步的编辑和验证。

### 2.3.2 网表编辑和验证的最佳实践

在CDL网表生成后,进行适当的编辑和验证是确保电路设计正确性的关键步骤:

- **维护一致性**:确保网表中的连接关系、元件参数和属性与原理图保持一致。

- **格式化和规范**:使用适当的编辑器进行格式化处理,以便于阅读和理解。对于复杂电路,保持网表的规范和组织性尤为重要。

- **验证检查**:运用EDA工具提供的网表检查功能,检查潜在的错误,如悬空端口、错误连接等。

- **仿真测试**:进行逻辑仿真和时序分析,确保网表导出的电路在功能和性能上满足设计要求。

通过上述流程,设计师不仅能够提高电路设计的效率,还能够在电路制造之前发现和修正潜

0

0