【布线工程挑战】:复杂系统中保证PCIe_SATA_USB等长布线的成功策略

发布时间: 2024-12-15 09:13:59 阅读量: 2 订阅数: 7

PCIE/SATA/USB等对间等长 布线指导

参考资源链接:[PCIe/SATA/USB布线规范:对内等长与延迟优化](https://wenku.csdn.net/doc/6412b727be7fbd1778d49479?spm=1055.2635.3001.10343)

# 1. PCIE_SATA_USB接口布线工程概述

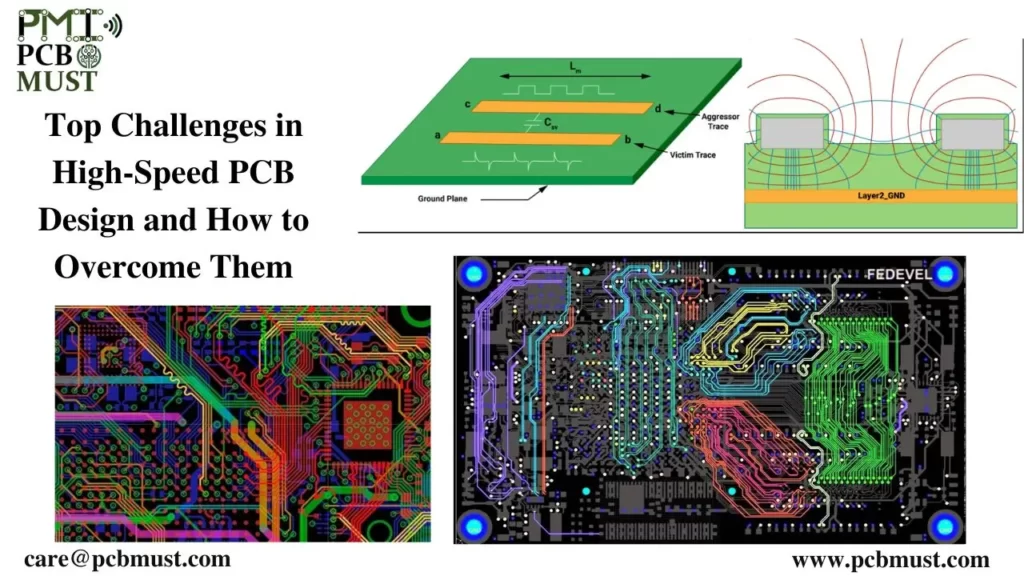

在现代信息技术领域,高速数据传输接口如PCI Express (PCIe)、Serial ATA (SATA)和Universal Serial Bus (USB)已成为设备互联互通不可或缺的部分。这些接口不仅需要高效率的数据处理能力,还需要稳定的物理布线支持以确保信息的可靠传输。本章将概述PCIE、SATA和USB接口布线工程的核心概念,包括接口的基础知识、布线设计的初步理解,以及如何在各类硬件系统中实现高效布线。

## 1.1 接口技术的发展背景

随着个人计算机、服务器、存储设备等数据密集型设备的需求不断增长,对高速接口技术的依赖变得越来越重要。高速接口技术的发展旨在解决数据传输速率与系统性能之间的瓶颈。在众多接口技术中,PCIe以其高带宽、低延迟和扩展性强的特点,在高性能计算领域占据主导地位。相比之下,SATA和USB接口则更多地应用于数据存储和通用外设的连接,尽管它们的传输速率比PCIe慢,但在普及度和兼容性方面表现优异。

## 1.2 布线工程的重要性

布线工程在实现接口技术的物理连接上扮演着关键角色。一个良好的布线设计能够有效降低信号损耗,减少电磁干扰,并保障数据传输的稳定性和可靠性。在设计布线时,工程师需要考虑到信号完整性、布线空间限制以及与系统其他组件的兼容性等因素,这些都是保障接口正常运作的基础。

## 1.3 接口布线的常见挑战

在实施布线工程的过程中,工程师面临多种挑战,如确保信号在长距离传输中保持完整性、防止由于阻抗不匹配引起的反射和串扰等问题。此外,随着设备复杂性的增加,布线设计还需兼顾系统的散热、维护性以及可能的电磁兼容问题。了解并应对这些挑战对于提高布线工程的性能至关重要。

# 2. 接口信号特性和布线要求

## 2.1 信号传输理论基础

### 2.1.1 PCIe信号特性及其传输要求

PCI Express(PCIe)作为一种高速串行计算机扩展总线标准,广泛应用于个人计算机、服务器和其他电子系统中。PCIe信号传输特性包括高速率、低电压、差分信号等关键要素。在设计布线时,PCIe信号的传输要求极为严格,因为任何布线的不规范都可能导致信号质量下降,从而引起数据错误或系统崩溃。

要保证PCIe信号的可靠性,必须确保阻抗匹配和信号完整性。阻抗不匹配会引起信号反射,从而损害信号的完整性和传输效率。在实际应用中,PCIe总线设计工程师通常会采用100欧姆差分阻抗匹配来最小化信号失真和反射。

```markdown

| 参数 | 值 | 解释 |

|----------|----------|--------------------------------------------------------------|

| 差分阻抗 | 100 欧姆 | 确保在传输路径中信号反射最小,提高传输效率。 |

| 传输速率 | 8 Gbps | 第一代PCIe的速度。后续版本会有更高传输速率如16Gbps、32Gbps等。 |

| 电压标准 | 0.8V | PCIe总线使用的低电压标准,有助于提高能效。 |

```

### 2.1.2 SATA信号特性及其传输要求

串行ATA(SATA)是另一种广泛用于硬盘驱动器等存储设备的接口技术。SATA信号的传输特点与PCIe有显著不同,主要是因为SATA设计最初考虑的是存储而非高速数据传输。SATA信号具有较低的传输速率,但依然需要保证良好的信号完整性来维持数据的正确读写。

SATA信号的布线要求中,主要是关注信号的时序和完整性。SATA的物理层在设计上更多地依赖于信号的时序控制来保证数据的稳定传输。布线过程中,应避免过长的走线以及过多的过孔,因为这些都可能导致信号时序问题。

### 2.1.3 USB信号特性及其传输要求

通用串行总线(USB)是一种非常普及的接口,支持热插拔和即插即用的特性。随着USB 3.0、USB 3.1等版本的推出,传输速率也达到了5Gbps甚至更高,因此对信号的质量和布线设计提出了更高要求。

USB信号要求较高的信号完整性以确保数据不出现错误。USB 3.0引入了新的信号线传输协议,并对布线提出了新的要求。例如,USB 3.0引入了包含高速差分信号线对和一个接地线的SuperSpeed信号对。因此,在USB 3.0及更高版本的布线设计中,必须考虑到信号的差分特性。

## 2.2 接口布线的电气性能要求

### 2.2.1 阻抗匹配与信号完整性

在PCB设计中,阻抗匹配是保证信号完整性的重要因素。阻抗失配可能导致信号反射,降低信号质量。PCB布线工程师需确保所有走线阻抗与源端及负载端阻抗一致,这对于高速信号尤其关键。

实现阻抗匹配的方法一般有以下几种:

- 选择合适的走线宽度和层叠结构设计。

- 使用特征阻抗控制软件对走线进行模拟优化。

- 在高速信号路径中增加匹配元件,如终端电阻。

### 2.2.2 串扰与反射的控制方法

串扰和反射是布线过程中常见的信号干扰问题。串扰是由相邻走线间的电磁干扰引起的,而反射则是由于信号阻抗不匹配导致。控制方法包括:

- 使用足够的走线间距以减少串扰。

- 在高速信号路径中使用差分对来提高抗干扰性。

- 在必要位置设置终端匹配,以减少信号反射。

```mermaid

graph TD

A[开始布线] --> B[优化走线间距]

B --> C[应用差分对]

C --> D[终端匹配]

D --> E[减少串扰和反射]

```

### 2.2.3 差分信号布线要求

差分信号布线在高速接口设计中扮演着关键角色。它通过传输成对的信号(正负)来减少外部电磁干扰的影响。设计差分信号布线时,需要注意以下几点:

- 确保两条差分信号线等长,以保持它们的相位一致性。

- 避免或最小化差分线对间距的变化。

- 对于高频率信号,考虑使用微带线或者带状线的布线方式。

## 2.3 PCB布线设计基本原则

### 2.3.1 层叠结构设计要点

PCB层叠结构的设计对高速信号的传输性能有着决定性影响。一个优化的层叠结构能提供良好的阻抗控制和电磁兼容性能。在设计时需要注意以下要点:

- 为高速信号层提供参考平面层,以减少信号辐射和回流。

- 选择合适的介电常数(Dk)和厚度(Df)的介质材料。

- 考虑信号层和电源层的布局,避免产生过多的噪声。

### 2.3.2 追踪布局与布线的间距

追踪布局与布线间距的设计对信号的串扰和阻抗匹配有很大影响。在设计时应遵循以下原则:

- 增加信号线间的间距以减少串扰。

- 在高频信号布线时,保持统一的线宽和间距以确保阻抗一致性。

- 避免布线的尖锐转角,使用较大圆弧过渡以减少高频信号损耗。

### 2.3.3 避免信号间干扰的最佳实践

信号间干扰会降低信号质量,严重时会影响系统稳定性。为了最小化信号间的干扰,以下是一些最佳实践:

- 对信号进行分类,将高速信号和低速信号分开布局。

- 使用地平面来隔绝不同的信号区域,减少信号干扰。

- 采用屏蔽层或隔离区来保护敏感信号免受干扰。

以上这些详尽的分析和实践,为设计可靠的PCB布线提供了基础性的指导原则。在实际操作过程中,布线工程师需根据具体的项目需求,灵活运用这些原则来优化设计,确保信号的传输品质和系统稳定性。

# 3. 复杂系统中的长布线策略

0

0