【XDMA IP核性能提升大法】:5大策略显著提高数据吞吐量

发布时间: 2024-12-15 10:14:52 阅读量: 4 订阅数: 5

xdma ip核中文手册

参考资源链接:[Xilinx DMA/Bridge Subsystem for PCIe中文手册](https://wenku.csdn.net/doc/4vnvp9w35r?spm=1055.2635.3001.10343)

# 1. XDMA IP核基础及性能考量

## 1.1 XDMA IP核简介

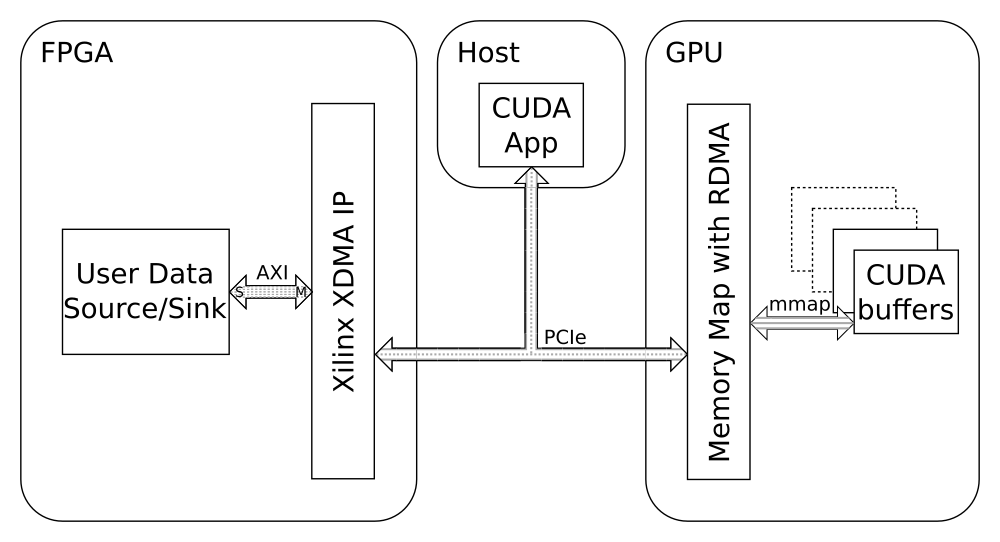

XDMA IP核是一种高性能的直接内存访问(DMA)控制器,专为满足FPGA与处理器间高速数据传输需求设计。它允许FPGA设备直接读写CPU的内存空间,大大降低CPU的负载并提升数据传输速率。理解XDMA的基本工作机制和关键性能指标是优化其应用的基础。

## 1.2 关键性能指标

在考虑XDMA IP核的性能时,需要关注几个关键指标:传输带宽、延迟和吞吐量。带宽决定了数据传输的最大速度,延迟是完成单次数据传输所需的时间,而吞吐量反映了在持续传输中系统能处理的数据量。优化这些指标是提高系统整体效率的重要环节。

## 1.3 性能考量与评估

评估XDMA IP核性能时,应首先建立基准测试环境,通过典型的测试用例来测量上述指标。此外,考虑实际应用场景中的并发操作、数据包大小和传输模式等因素对性能的影响也至关重要。通过逐步调整和测试,可以发现和解决性能瓶颈,充分发挥XDMA IP核的潜力。

# 2. 硬件设计策略优化

硬件设计的优化对于提高系统的整体性能至关重要。本章将深入探讨如何通过精确配置和优化XDMA IP核来提升硬件设计的效率。我们将从核心参数的调整到高速信号的布线与优化等方面,逐一讲解硬件设计的优化策略。

## XDMA IP核的配置与初始化

在硬件设计中,正确配置XDMA IP核是性能优化的第一步。本节将详细说明核心参数的调整方法以及缓冲区管理和优化策略,这些将直接影响到数据传输的效率和系统的稳定性。

### 核心参数调整

XDMA IP核的配置是通过一系列核心参数来完成的,包括但不限于数据宽度、最大传输长度以及请求和完成缓冲区的大小等。正确的参数设置能够最大限度地提高传输效率和减少资源消耗。

```verilog

// XDMA IP核参数示例配置

parameter DATA_WIDTH = 64; // 数据宽度为64位

parameter MAX_TRANS_LENGTH = 1024; // 最大传输长度为1024字节

parameter REQ_BUFFER_SIZE = 4; // 请求缓冲区大小为4

parameter COMP_BUFFER_SIZE = 4; // 完成缓冲区大小为4

```

在设置参数时,需要根据实际应用场景的需求来进行平衡。例如,增加数据宽度可以提高每次传输的数据量,但同时也会增加FPGA内部资源的占用。在实际配置时,应根据数据传输的实际需求和硬件资源限制来决定。

### 缓冲区管理和优化

在XDMA IP核中,缓冲区的管理是影响传输性能的关键因素之一。适当的缓冲管理可以有效减少数据传输的延迟,提高系统处理吞吐量。以下是一些优化缓冲区管理的策略:

- 预分配缓冲区:在系统启动时预先分配一定数量的缓冲区,这样可以减少动态分配缓冲区的时间开销。

- 缓冲池机制:利用缓冲池来管理缓冲区,可以减少内存碎片,提高内存利用效率。

- 读写分离:采用读写分离的缓冲区管理策略,可以同时处理读取和写入请求,提升吞吐率。

```c

// 缓冲区管理伪代码示例

void* bufferPool = malloc(sizeof(Buffer) * BUFFER_POOL_SIZE);

for (int i = 0; i < BUFFER_POOL_SIZE; ++i) {

bufferPool[i].size = BUFFER_SIZE;

bufferPool[i].next = NULL;

}

```

## 时钟域和信号完整性分析

时钟域交叉处理和信号完整性改善是硬件设计中不可忽视的环节,它们对于确保数据传输的准确性和硬件稳定性有着决定性的影响。

### 时钟域交叉处理

在多时钟域系统中,时钟域交叉是常见的设计问题。解决时钟域交叉的关键在于使用适当的同步机制和数据传输技术,如双触发器同步、异步FIFO等。

```verilog

// 双触发器同步示例代码

always @(posedge clk1) begin

sync_reg1 <= signal_in;

end

always @(posedge clk2) begin

sync_reg2 <= sync_reg1;

end

assign signal_out = sync_reg2;

```

### 信号完整性改善技巧

信号完整性问题可能会导致信号失真、误码率增加等问题。改善信号完整性可以通过以下方法:

- 采用终端匹配技术,如并联终端匹配或戴维宁终端匹配。

- 控制传输线路的阻抗,使其保持在特定的范围内,以减少反射和串扰。

- 合理布局和布线,避免长距离信号线,减少信号传输时延和干扰。

```mermaid

flowchart LR

A[信号源] -->|控制阻抗| B[传输线]

B -->|终端匹配| C[负载]

```

在硬件设计时,应综合考虑信号的路径、长度、阻抗以及与其他信号线路的相对位置等因素,从而优化整体信号传输的质量。

## 高速信号布线与优化

高速信号布线不仅关系到信号的传输质量,还直接影响到系统的性能和稳定性。有效的布线策略对于高速信号尤为重要。

### 线路阻抗匹配与传输线设计

高速信号布线时,阻抗的连续性和匹配性是必须考虑的问题。阻抗不匹配会导致信号反射,增加传输错误的概率。传输线设计需要确保阻抗在源端和负载端的一致性。

```mermaid

graph LR

A[源端阻抗] -->|连续一致| B[传输线]

B -->|阻抗匹配| C[负载阻抗]

```

在设计传输线时,还需要考虑线路的长度和形状,以避免过长的传输延迟和信号串扰。例如,蛇形线可以用于增加信号路径长度,但过密的蛇形线会增加串扰和信号损失。

### 高速信号的屏蔽与终结策略

为了减少信号的辐射和接收外部干扰,高速信号通常需要采取屏蔽措施。屏蔽可以通过使用屏蔽层、屏蔽罩或共模扼流圈等方式实现。同时,高速信号线的终结策略,如使用匹配电阻或终结IC,也是保证信号完整性的重要手段。

```verilog

// 匹配电阻终端示例

assign termination_resistor = 50; // 终端电阻值为50欧姆

```

高速信号的布线和优化对于硬件设计的性能有着直接的影响,因此,在设计过程中,工程师需要特别注意这些问题。

硬件设计策略的优化需要一个全面且细致的过程,涵盖从配置参数的微调到信号完整性的保障,再到高速信号布线的精心布局。通过对这些方面的深入理解和精心设计,可以显著提升硬件的性能,保证系统稳定可靠地运行。在下一章中,我们将进一步探讨软件驱动与固件策略的优化,以实现软硬件协同工作,进一步提升系统整体性能。

# 3. 软件驱动与固件策略优化

在数字系统设计中,软件驱动和固件编程是链接硬件与操作系统,确保系统性能与稳定性的重要环节。本章节将深入探讨驱动级性能调优、固件编程与资源管理,以及调试工具与性能监控的策略和方法。

## 3.1 驱动级性能调优

### 3.1.1 中断处理机制优化

在高性能系统中,中断处理机制的效率直

0

0