0.5μm CMOS工艺下高性能流水线ADC采样保持电路设计

102 浏览量

更新于2024-09-01

收藏 341KB PDF 举报

模拟技术中的用于流水线ADC采样保持电路的设计是一种关键电路单元,它在高速、高精度的数字信号处理中起着至关重要的作用。本文主要介绍了一种创新的电路结构,旨在提升流水线ADC的整体性能。

该电路的核心在于采用了电容翻转式电路结构。这种设计策略通过交替改变电容的充电状态,实现了快速的转换过程,从而提高了采样速度。这样做的好处在于避免了传统电容匹配可能导致的失真误差,确保了信号的准确转换。

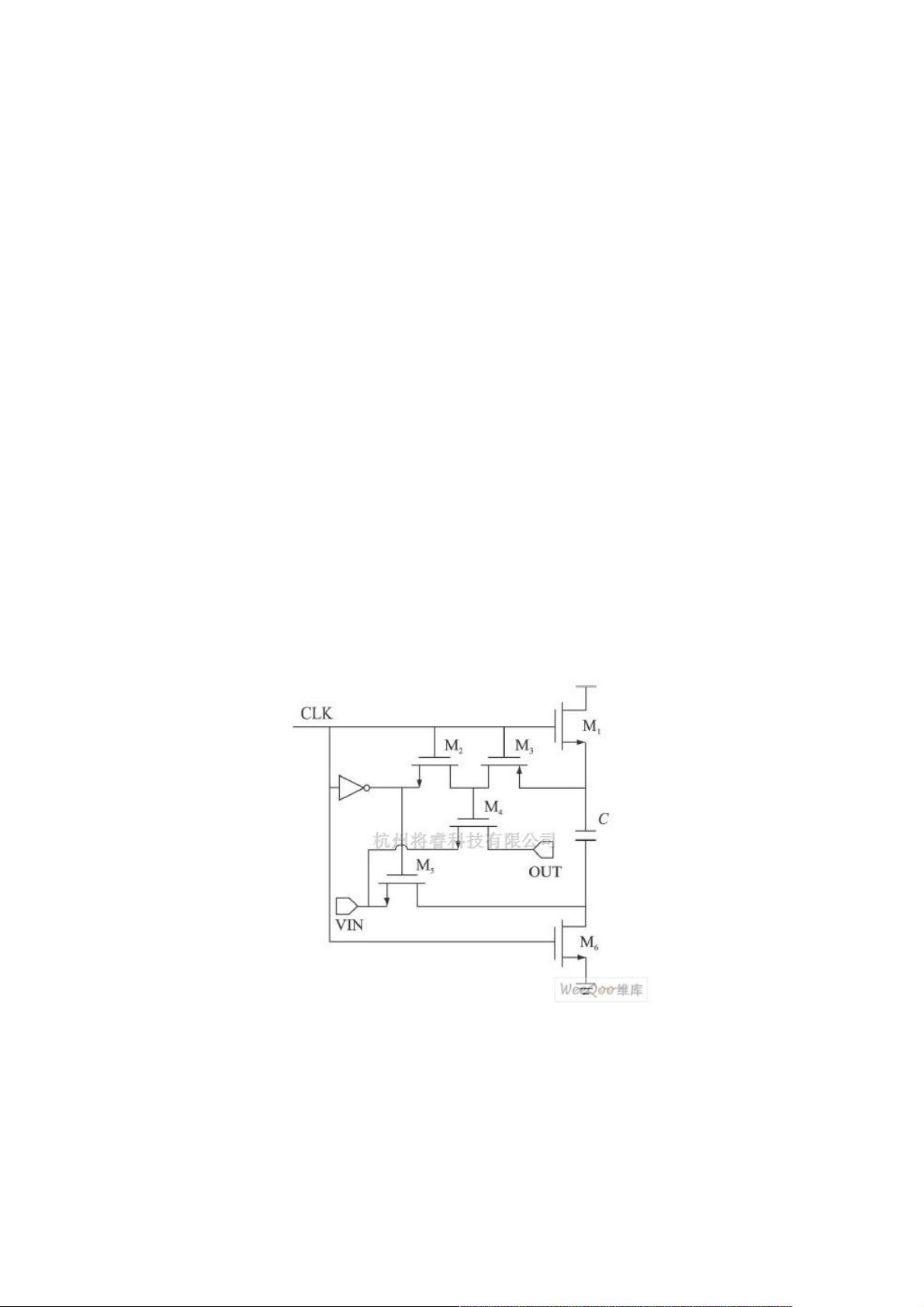

同时,为了减少时钟馈通和电荷注入效应,电路采用了栅压自举采样开关。栅压自举技术有效地解决了单沟道模拟开关导通电阻非线性和寄生电容带来的问题,提高了开关的线性度和稳定性,减少了信号在传输过程中的失真。

全差分运算放大器的应用进一步提升了电路的性能。这种放大器具有良好的共模抑制比,能够有效地抑制噪声,保证了信号的精确度和线性度,这对于提高整个ADC的动态范围至关重要。

电路设计在0.5微米CMOS工艺下完成,工作电源电压为5伏特,具有较高的采样频率,即10兆赫兹。当输入信号频率为1兆赫兹时,输出信号的无杂散动态范围(SFDR)达到73.4分贝,显示出优秀的抗干扰能力。此外,电路的功耗控制得相当低,仅为20毫瓦,这在追求能源效率的现代电子设备中是一项重要指标。

随着通信技术、图像处理和多媒体技术的发展,对ADC的性能要求日益提高,尤其是对于流水线ADC,其速度快、精度高、功耗低的特点使其在工业自动化等领域得到了广泛应用。采样保持电路作为ADC的关键部分,其优化设计对于整体系统性能的提升至关重要。

总结来说,本文介绍的采样保持电路通过创新的结构设计和元件选择,提升了ADC的性能,包括转换速度、失真抑制、噪声抑制和功耗控制,使其满足了现代数字信号处理系统对高质量信号处理的需求。

622 浏览量

1488 浏览量

353 浏览量

395 浏览量

353 浏览量

395 浏览量

551 浏览量

162 浏览量

390 浏览量

weixin_38729108

- 粉丝: 5

最新资源

- 武汉大学数字图像处理课程课件精要

- 搭建个性化知识付费平台——Laravel开发MeEdu教程

- SSD7练习7完整解答指南

- Android中文API合集第三版:开发者必备指南

- Python测试自动化实践:深入理解更多测试案例

- 中国风室内装饰网站模板设计发布

- Android情景模式中音量定时控制与铃声设置技巧

- 温度城市的TypeScript实践应用

- 新版高通QPST刷机工具下载支持高通CPU

- C++实现24点问题求解的源代码

- 核电厂水处理系统的自动化控制解决方案

- 自定义进度条组件AMProgressView用于统计与下载进度展示

- 中国古典红木家具网页模板免费下载

- CSS定位技术之Position-master解析

- 复选框状态持久化及其日期同步技术

- Winform版HTML编辑器:强大功能与广泛适用性