12位流水线ADC采样保持电路设计与分析

100 浏览量

更新于2024-09-02

1

收藏 227KB PDF 举报

"模拟技术中的适用于12 bit流水线ADC采样保持电路的设计"

在模拟电子技术中,模数转换器(ADC)是数字系统与模拟世界之间的关键接口,尤其是在图像传感器应用中。随着CMOS(互补金属氧化物半导体)技术的进步,CMOS图像传感器已经广泛应用于各种设备,如超微型数码相机和手机,得益于它们的高集成度、低功耗和成本效益。在这些系统中,流水线ADC因其高速度、低功耗和中高精度的特点,成为芯片级和列级A/D转换器的理想选择。

目前,国际上流水线ADC的先进水平已达到14位10MHz的采样速率,而国内多数产品停留在10位。这表明对于10位以上,特别是12位的高精度流水线ADC的研究仍有待深入。采样保持电路作为ADC的前端核心部分,其性能直接影响着整体ADC的转换精度和稳定性。

本文提出了一种全差分电荷转移型的采样保持电路设计方案,该电路能够有效解决电荷注入和时钟馈通问题,提高电路性能。电荷注入通常指的是在开关操作中,不必要的电荷进入电路,导致测量误差;而时钟馈通则是指时钟信号对信号路径的干扰。通过底极板采样技术和栅压自举电路,可以消除与输入信号相关或无关的电荷注入和时钟馈通,改善电路的线性度。

此外,设计中还采用了折叠式增益增强运算放大器,这种放大器能够减少由于有限增益和不完全建立时间带来的误差,从而提升系统的整体性能。在5V电源电压下,20MS/s的采样频率,当输入信号为奈奎斯特频率时,该采样保持电路实现了76dB的无杂散动态范围(SFDR),采样精度达到0.012%,满足12位精度的要求。

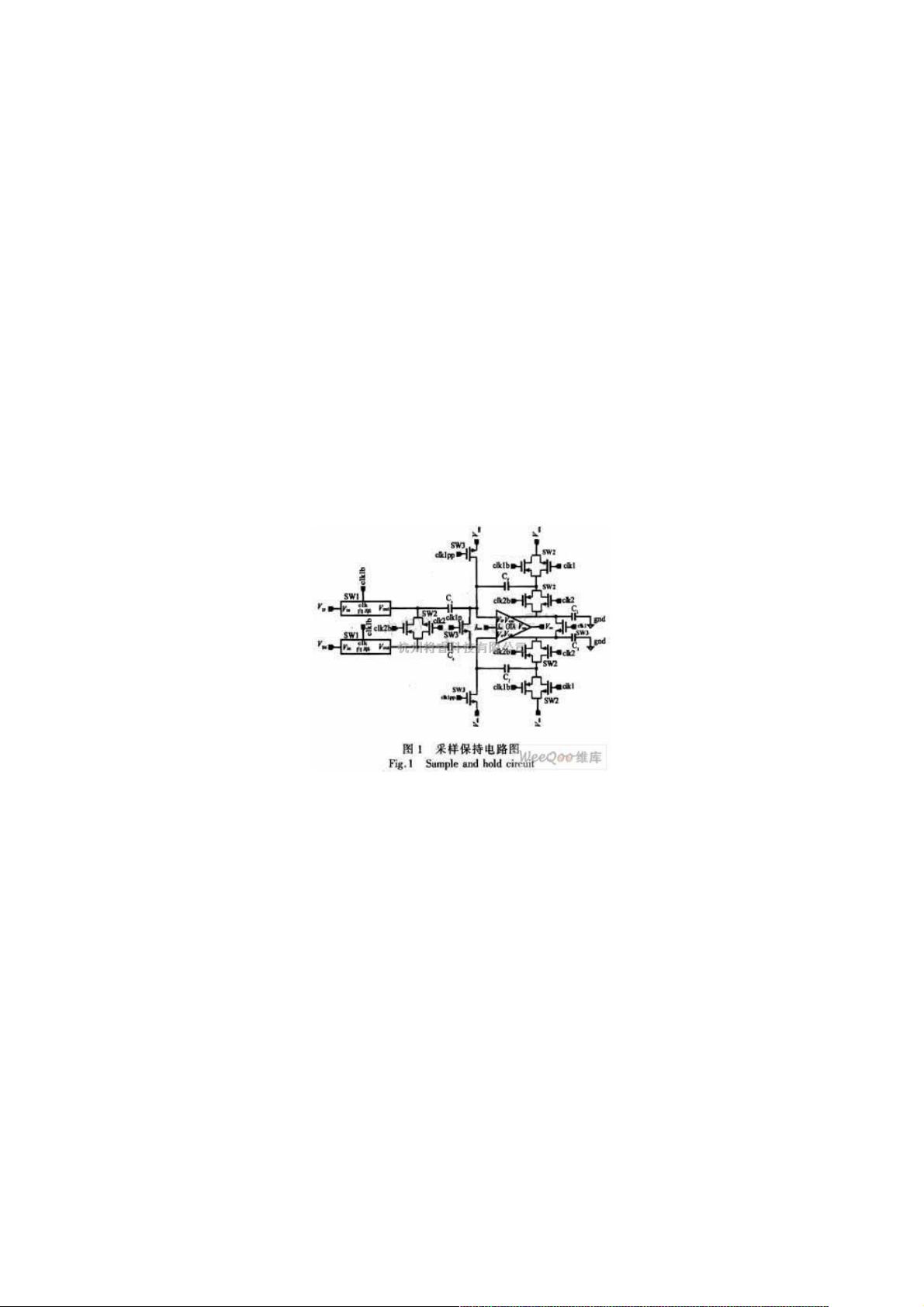

图1展示了本文设计的电荷转移型采样保持电路结构,其工作时序由两相不交叠时钟clk1和clk2控制,clkb为clk1的反相信号。在clk1高电平期间,电路进行采样,输入信号被存储在采样电容Cs上;当clk2高电平时,电路进入保持相,差分电荷转移至反馈电容Cf,以保持采样值不变,确保在ADC转换过程中输入信号的稳定。

这种全差分电荷转移型采样保持电路设计,结合了优化的电路架构和先进技术,旨在实现12位高精度流水线ADC所需的采样保持功能,这对于提升图像传感器的整体性能和应用范围具有重要意义。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-01-20 上传

2020-11-07 上传

2021-01-20 上传

2020-10-19 上传

2021-01-20 上传

2016-06-16 上传

weixin_38698943

- 粉丝: 2

- 资源: 899

最新资源

- CRUD-JS

- 这是一个简单弹出视图

- PruebaV-V_Verde:佛得角

- Extract data from an existing .fig file:Extract data from an existing matlab 2D or 3D figure-matlab开发

- 行业分类-设备装置-接触网整体吊弦恒张力预制平台.zip

- LiveSplit.GBA:BizHawk中GBA模拟器的通用自动拆分器

- 设计:Tidyverse设计原则

- analyze_mcmc.rar_Windows编程_FlashMX_

- matlab转换java代码-POSTaggerSML:Stanford-MATLAB词性标注器:MATLAB所采用的StanfordLog-

- p2pshaper-开源

- 参考资料-27建筑施工企成本管理办法.zip

- krautadmin:KrautAdmin-基于服务器的兄弟情谊应用程序

- 在应用添加AdMob广告案例

- myfifo.rar_VHDL/FPGA/Verilog_VHDL_

- angularJs-datatable

- SQLWeek3