12bit低功耗流水线ADC:采样保持与MDAC集成设计

135 浏览量

更新于2024-08-30

收藏 383KB PDF 举报

本文介绍了一种用于12位40MS/s低功耗流水线ADC的采样保持电路设计,该设计集成了MDAC功能,旨在优化功耗和芯片面积。

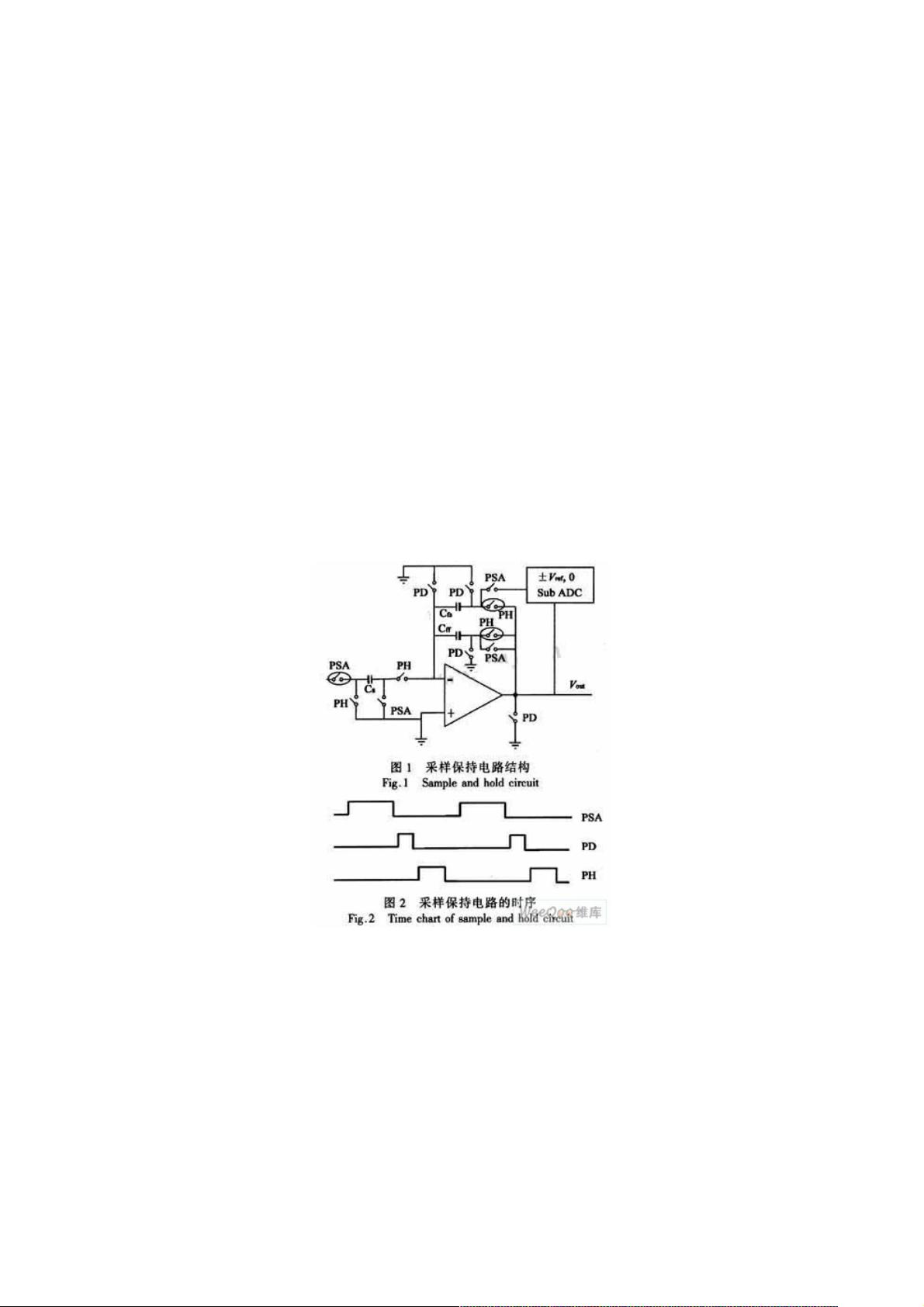

1. 流水线模数转换器(pipeline ADC)详解

流水线ADC是高精度和高速应用中的首选架构,它支持10到14位的分辨率和10到500MS/s的采样率,常见于通信系统、图像设备和视频处理等领域。这种ADC的关键组件——采样保持电路,对整体性能有着直接影响,特别是在功耗方面有严格要求。

2. 采样保持电路的作用与结构

传统的流水线ADC设计中,采样保持电路位于前端,随后连接MDAC级。该电路有助于减少因MDAC与子ADC之间采样信号不匹配导致的孔径误差。考虑到采样保持电路在ADC前级的位置,其对精度的需求较高,因此功耗也相对较大,约占ADC总功耗的20%至30%。为了降低功耗和芯片面积,本设计将采样保持与MDAC功能结合。

3. 采样保持与MDAC级的协同工作

流水线ADC采用双向非交叠时钟控制,使得相邻的采样保持电路和MDAC级交替处于采样或保持状态。这种工作模式允许采样保持电路和MDAC共用同一运算放大器,以实现功耗的节省和芯片面积的减少。

4. MDAC选择1.5位/级的理由

每级包含1位冗余,用于数字冗余修正,从而减轻比较器失调的影响。1.5位/级结构的增益为2,使得开关电容电路的负载电容减小,反馈因子增大,提高转换速度,同时保持较低的单级分辨率,以实现更高的总体性能。

5. 采样保持电路的工作原理与结构

设计中的采样保持电路由3相时钟控制,执行采样/放大、复位和保持三种操作。自举开关在特定时序点起作用,确保准确的信号传输和保持。

6. 性能优化

通过集成MDAC功能,本设计不仅提供了高速高精度的采样保持,还有效地降低了ADC的功耗,减少了芯片占用的空间,从而提升了整体系统的效能和效率。

总结,本设计提出的采样保持电路对于实现12位40MS/s低功耗流水线ADC至关重要,其创新之处在于结合MDAC功能,既满足了高速高精度的需求,又显著优化了功耗和芯片尺寸,为中高精度高速ADC的设计提供了一种有效方案。

2020-11-07 上传

2020-05-31 上传

点击了解资源详情

2021-01-20 上传

2021-01-20 上传

2020-11-07 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38741996

- 粉丝: 45

- 资源: 932

最新资源

- MPU6050.zip_微处理器开发_C/C++_

- Http抓包工具.zip

- imvijayps.github.io

- passwordmanager:使用烧瓶的密码管理器

- DTCMS网站内容管理系统 v2.0 Access版

- robotframework-pyspherelibrary:围绕pysphere的包装器,添加了连接缓存

- phpSmile-开源

- 植绒蜻蜓

- HackerRank:C#JavaC ++ Python中的HackerRank解决方案

- Freelancer Helper-crx插件

- OSSU-Computer-Science-Progress:我通过OSSU CS学位取得的进步

- shuffle-deck

- ezzy-config-setup:函数的类似于Java的配置

- MZRCFC.rar_按钮控件_Borland_C++_

- TheCSharp:演示了所有有趣的CSharp语言功能

- BUSA-8090