12位流水线ADC采样保持电路设计与分析

17 浏览量

更新于2024-08-30

收藏 289KB PDF 举报

"基于12 bit流水线ADC采样保持电路的设计"

在数字信号处理系统中,模数转换器(ADC)扮演着至关重要的角色,它将模拟信号转换为数字信号,便于后续的数字处理。流水线ADC是其中的一种高速、低功耗且具有中高精度的类型,尤其适用于图像传感器应用。随着CMOS工艺的进步,这种技术已经广泛应用于超微型数码相机和手机等设备中的图像采集。目前,国际上14位10 MHz的流水线ADC技术相对成熟,但在国内,大多数实现的是10位的版本,对于10位以上高精度的需求还有待进一步研发。

采样保持电路是ADC前端的关键组件,直接影响着整个ADC的性能。它负责在输入信号的特定时间点“采样”并“保持”信号值,以便ADC的后续级能够进行准确的量化和转换。在本设计中,采用了全差分电荷转移型结构的采样保持电路,这一设计的优势在于能有效消除与输入信号无关的电荷注入和时钟馈通问题,提高电路的线性度和稳定性。

全差分结构能够提供较高的共模抑制比(CMRR),降低噪声影响,并且通过底极板采样技术,可以进一步消除与输入信号相关的电荷注入,从而减少转换误差。此外,采用栅压自举电路可减少开关操作中的非线性效应,提升转换精度。同时,为了减少增益误差和不完全建立时间的影响,设计中还应用了折叠式增益增强运算放大器,这有助于在高速采样条件下保持高分辨率和低失真。

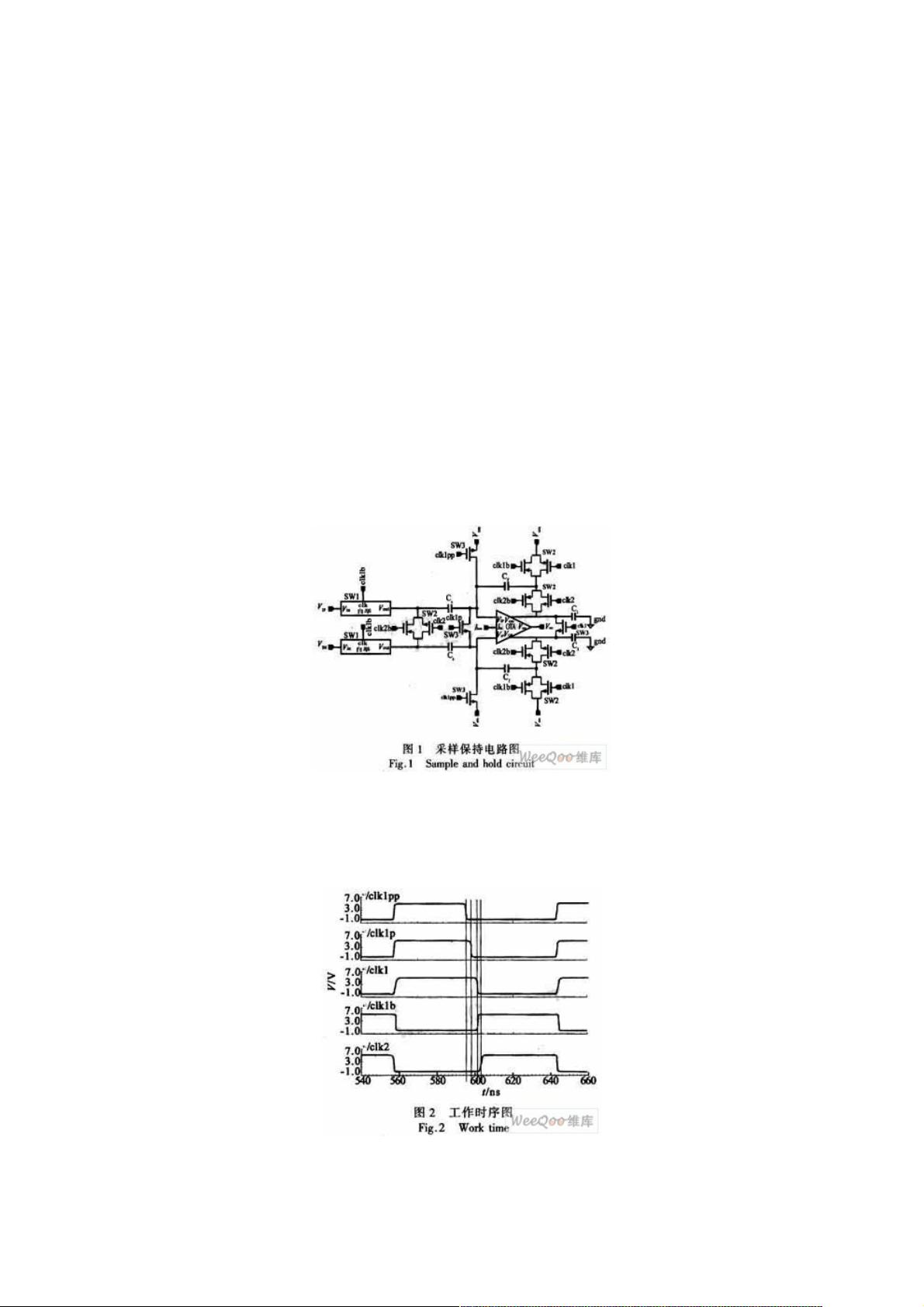

如图1所示的采样保持电路结构,其工作时序由两相不交叠的时钟clk1和clk2控制,分别对应采样和保持阶段。当clk1为高时,电路采样输入信号并将之存储在采样电容Cs上;而当clk2为高时,差分电荷被转移到反馈电容Cf上,进入保持阶段。这样的设计确保了在采样期间信号被精确捕获,而在保持期间信号的稳定。

在实际应用中,该12位采样保持电路在5V电源电压下,以20MS/s的采样频率工作,在处理奈奎斯特频率的输入信号时,表现出良好的性能:无杂散动态范围(SFDR)达到了76dB,表明其具有优秀的信噪比,而采样精度为0.012%,远超过12位ADC的精度要求。

该设计通过创新的全差分电荷转移型采样保持电路,解决了高精度流水线ADC中的一些关键挑战,实现了12位的转换精度,对于推动国内高精度ADC技术的发展具有重要意义。未来的研究方向可能包括优化电路布局以降低功耗,以及探索更高级别的位数以适应更复杂的图像处理需求。

2016-06-16 上传

2020-11-07 上传

2021-01-20 上传

2020-11-07 上传

点击了解资源详情

点击了解资源详情

2021-01-20 上传

2020-10-19 上传

点击了解资源详情

weixin_38680811

- 粉丝: 2

- 资源: 943

最新资源

- random

- Ajax+jsp+MySQL实现动态树形菜单

- AJAX_final

- jface:我的表盘

- Music and Lyrics-crx插件

- update

- Arduino-Eagle-Cad-Library:用于 Arduino Mini 和 Nano 的 Eagle Cad 库

- aabbtree-2.6.0-py2.py3-none-any.whl.zip

- Python3:Python 3项目

- seleniumKurs

- IterationBurndownAndScopeTracking:使用Lookback API构造燃尽图的Custom Rally应用程序,显示理想,最大和实际燃尽指标以及冲刺范围

- whiteboard::pencil:超简单共享白板

- 2013-2019年重庆理工大学817计算机基础综合考研真题

- 顶石2021

- worm

- WebUpd8-crx插件