数字电路:集成触发器详解

需积分: 15 147 浏览量

更新于2024-07-31

收藏 929KB PPT 举报

"该资源是关于数字电路的第五章,主要讲解了集成触发器的相关内容,包括基本RS触发器、同步RS触发器、主从触发器、边沿触发器以及不同功能触发器间的转换。课件适合学习数字电路的电子专业学生使用。"

在数字电路中,触发器是一种至关重要的基本逻辑单元,它具有记忆功能,能够存储一位二值信号。触发器的输出状态可以是0或1,并且当触发信号作用时,输出状态会发生变化。但触发信号消失后,其状态将保持不变,这就是触发器的记忆特性。触发器根据触发方式可以分为电平触发、脉冲触发和边沿触发,结构上可以分为基本RS触发器、钟控RS触发器、主从触发器和边沿触发器,功能上则有RS触发器、JK触发器、D触发器和T/T'触发器等。

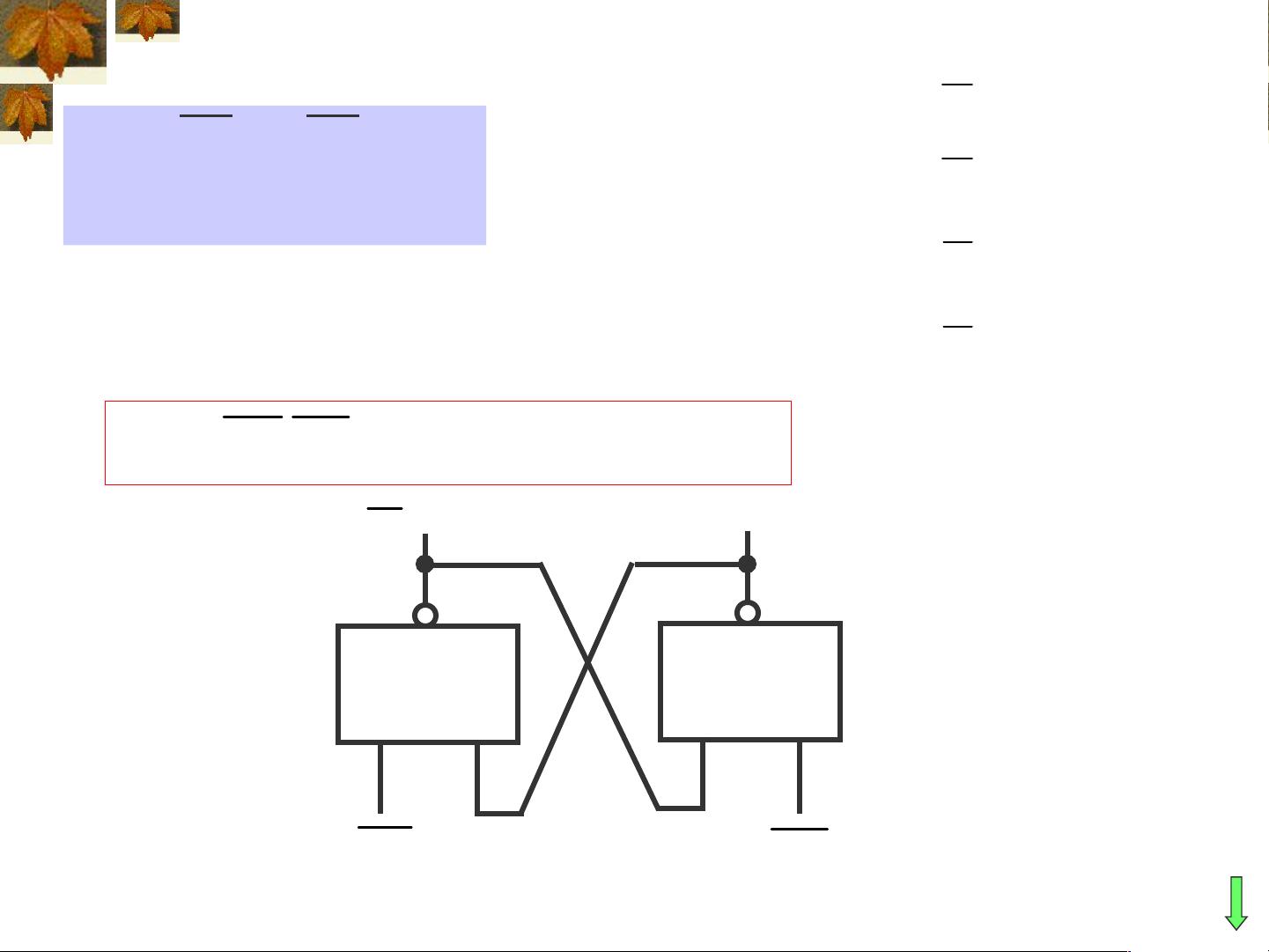

本章首先介绍了基本RS触发器,它是所有复杂触发器结构的基础。基本RS触发器由两个与非门交叉耦合组成,有两个触发输入端(R和S)和两个互补输出端(Q和Q')。当R和S都为1时,无论触发器原来的状态如何,输出都将保持不变,这被称为"禁止"或"不定"状态。如果R和S中的一个为0,另一个为1,触发器状态会根据原来的状态改变。例如,当R=1,S=0时,如果触发器原状态为1,则输出变为0;反之,如果原状态为0,输出变为1。

接着,章节讨论了同步RS触发器,这种触发器的R和S输入信号通常与时钟信号同步,以避免出现不定状态。主从触发器则通过时钟信号的上升沿或下降沿来决定触发器状态的变化,从而提高了抗干扰能力。边沿触发器则仅在时钟信号的边沿发生变化时更新其状态,这种方式能有效防止在时钟信号的高电平阶段和低电平阶段输入信号引起的错误翻转。

此外,章节还涉及了不同功能触发器间的转换,如如何通过适当逻辑操作将一个类型的触发器转换为另一种类型,以满足特定的应用需求。这为设计者提供了更大的灵活性,使他们可以根据系统要求选择最适合的触发器类型。

这一章深入探讨了集成触发器的各种类型及其工作原理,对理解和应用数字电路中的触发器具有非常重要的指导意义。对于学习电子和计算机工程的学生,掌握这些知识是进一步学习高级数字系统设计的基础。

2022-07-13 上传

2022-06-28 上传

点击了解资源详情

点击了解资源详情

论文

点击了解资源详情

点击了解资源详情

2023-06-02 上传

2023-06-06 上传

c1049615706

- 粉丝: 0

- 资源: 4

最新资源

- Hadoop生态系统与MapReduce详解

- MDS系列三相整流桥模块技术规格与特性

- MFC编程:指针与句柄获取全面解析

- LM06:多模4G高速数据模块,支持GSM至TD-LTE

- 使用Gradle与Nexus构建私有仓库

- JAVA编程规范指南:命名规则与文件样式

- EMC VNX5500 存储系统日常维护指南

- 大数据驱动的互联网用户体验深度管理策略

- 改进型Booth算法:32位浮点阵列乘法器的高速设计与算法比较

- H3CNE网络认证重点知识整理

- Linux环境下MongoDB的详细安装教程

- 压缩文法的等价变换与多余规则删除

- BRMS入门指南:JBOSS安装与基础操作详解

- Win7环境下Android开发环境配置全攻略

- SHT10 C语言程序与LCD1602显示实例及精度校准

- 反垃圾邮件技术:现状与前景