DDR2 Layout指南详解:嵌入式系统设计关键

需积分: 9 137 浏览量

更新于2024-07-23

收藏 787KB PDF 举报

DDR-layout指南是一种针对动态随机存取内存(Dynamic Random Access Memory, DDR)系列技术(包括DDR、DDR2、DDR3)的详细设计规范,这些技术在嵌入式系统中广泛应用,特别是在对速度有一定要求的场景。SDRAM常用于低端设备,而DDR/DDR2/DDR3随着技术的发展,以DDR2为主流,但DDR3正逐渐取代DDR2。

DDR/DDR2/DDR3的主要区别在于它们的内部“预取”(prefetch)技术,尽管外部接口(如clock、strobe、data、address、control和command线)的速率基本相似。理论上,当clock频率为266MHz时,data的频率也是266MHz,但需要注意的是,这个533MHz的比特率(BitRate)实际上指的是数据传输速率的一半,因为一个周期由两个时钟周期组成(即一个'0'和一个'1')。

布局指南提供了清晰的结构,通常包括 Micron 和 Freescale 的设计准则,着重于DDR2的设计要点。这些准则涵盖了信号组的划分,例如:

- 数字信号组:DQ(数据引脚)、DQS(差分时钟信号)、DM(数据管理信号),每个字节包含多个信号通道,如DQ0-DQ7、DQS0-DM0。

- 地址信号组:ADDRESS

- 命令信号组:CAS#(行地址选通)、RAS#(列地址选通)、WE#(写使能)

- 控制信号组:CS#(命令使能)、CKE(时钟使能)

- 时钟信号组:CK(主时钟)、CK#(子时钟)

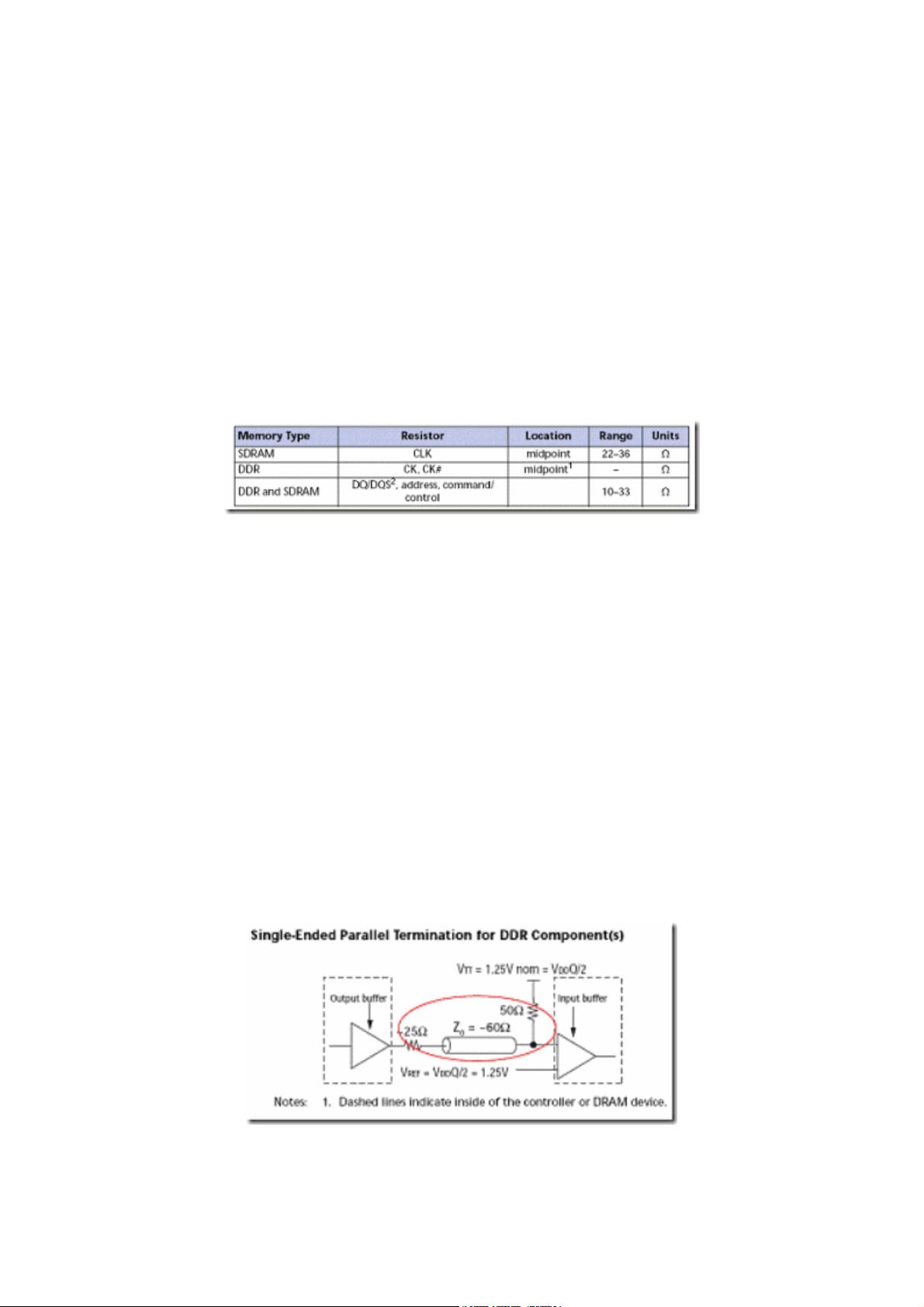

在PCB设计方面,推荐使用6层电路板,以控制阻抗在50~60欧姆范围内,保证信号的准确传输。电路板的厚度选择通常为1.5英寸,以确保足够的机械强度和信号完整性。此外,VSS(数字地)、VSSQ(信号地)、VDD(核心电源)和VDDDQ(DQ/I/O电源)的处理也很关键,除非另有说明,它们通常被视为等效的。

在使用这些指南时,可以参考lql-003-DDRDesignerChecklist文档,作为DDR设计的基础参考资料。通过遵循这些指导,设计师可以确保DDR芯片在嵌入式系统中的高效稳定运行。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-12-16 上传

2011-12-21 上传

2013-10-28 上传

2014-10-27 上传

103 浏览量

beibei_beibei

- 粉丝: 0

- 资源: 1

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南