理解静态时序分析(STA)在Xilinx FPGA中的应用

"该资源主要介绍了静态时序分析(Static Timing Analysis, STA)在Xilinx FPGA设计中的应用,强调了其在确保FPGA性能和时序正确性的重要性。"

在电子设计自动化领域,特别是FPGA设计中,静态时序分析是不可或缺的一个环节。静态时序分析是一种用于评估数字集成电路时序性能的技术,它不依赖于电路的实际动态行为,而是基于电路的逻辑结构和预定义的时序约束来分析信号的延迟。

FPGA,即现场可编程门阵列,其内部包含大量的逻辑单元和互连资源,可以灵活配置以实现各种复杂的数字电路。如同PCB板上的信号传输,FPGA内的信号传输也会产生延迟。这些延迟包括逻辑门延迟、互连资源延迟以及布线延迟等。因此,理解这些延迟对于确保FPGA设计满足时序要求至关重要。

静态时序分析的目的是确保系统满足设计者设定的时序规范,例如建立时间(setup time)和保持时间(hold time)。建立时间是指数据必须在时钟边沿之前到达目的地的时间,而保持时间是指数据必须在时钟边沿之后保持稳定的时间。如果这些时序要求不被满足,可能会导致数据错误,降低系统性能,甚至造成系统无法正常工作。

在进行静态时序分析时,设计者首先定义时序约束,如最大允许路径延迟。然后,利用专门的EDA工具,比如Xilinx的Vivado或ISE,进行分析。工具会模拟所有可能的信号路径,并计算每个路径的延迟。如果所有路径都满足约束,设计就被认为是时序收敛的;反之,如果不满足,工具会提供反馈,指导设计者优化设计,例如调整逻辑布局、缩短关键路径或改变时钟分配。

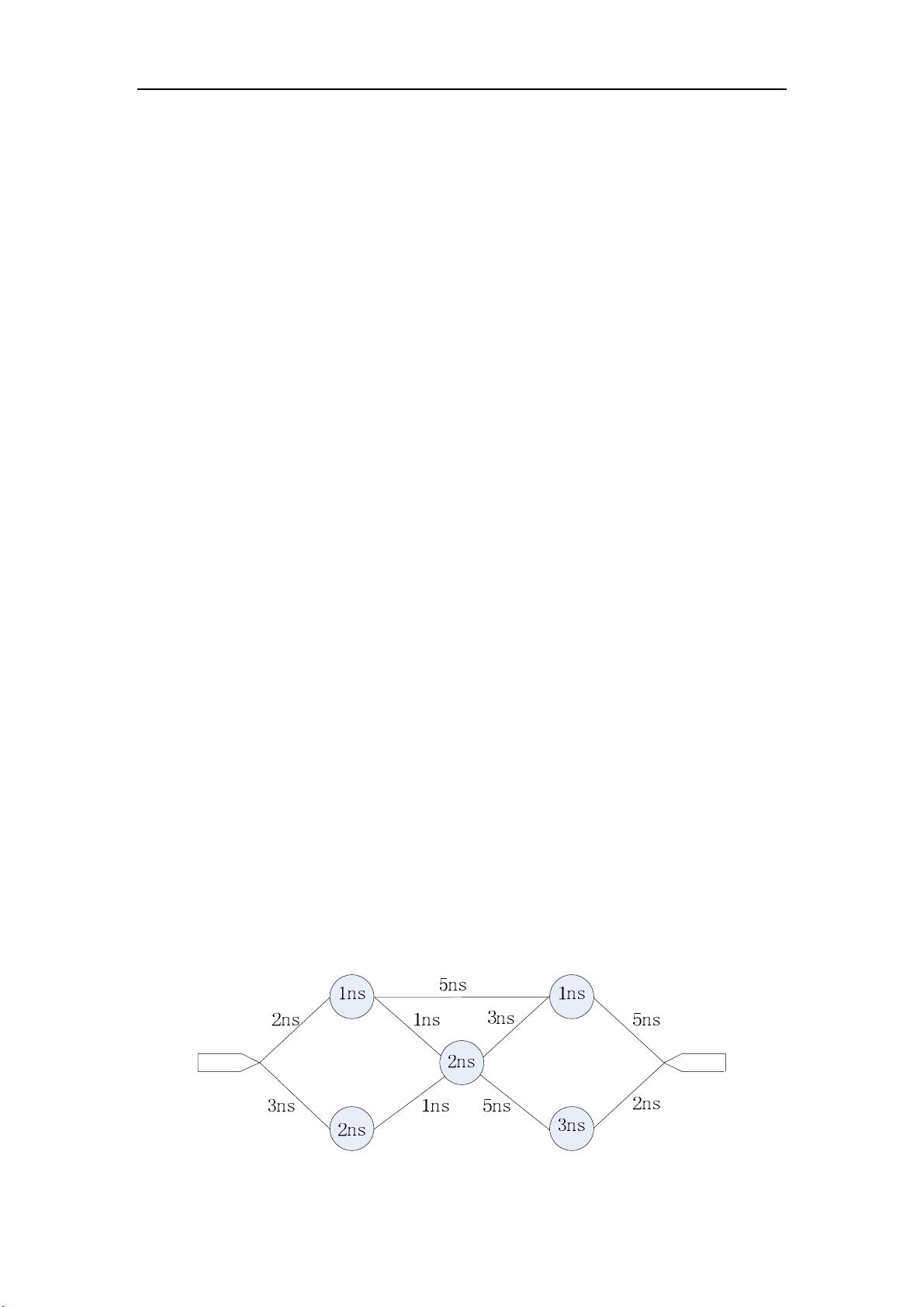

举例来说,如果一个信号在FPGA内部必须在15ns内从输入传递到输出,设计者会设定这个时序约束。静态时序分析工具会分析所有可能的路径,找出那些延迟不超过15ns的路径。在给出的例子中,有两个路径满足这个条件,工具会选择其中之一作为优化后的设计方案。

静态时序分析在FPGA设计中扮演着确保系统时序正确性和性能的关键角色。通过精确的时序分析,设计者能够优化设计,减少延迟,从而提高系统的运行速度和可靠性。在Xilinx FPGA设计中,熟练掌握静态时序分析技巧对于实现高效、高性能的数字系统至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-03-29 上传

2022-12-29 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

shenzhendaxue_zhang

- 粉丝: 0

- 资源: 1