"VLSI设计方法及ATPG介绍:可测试性设计与EDA工具应用"

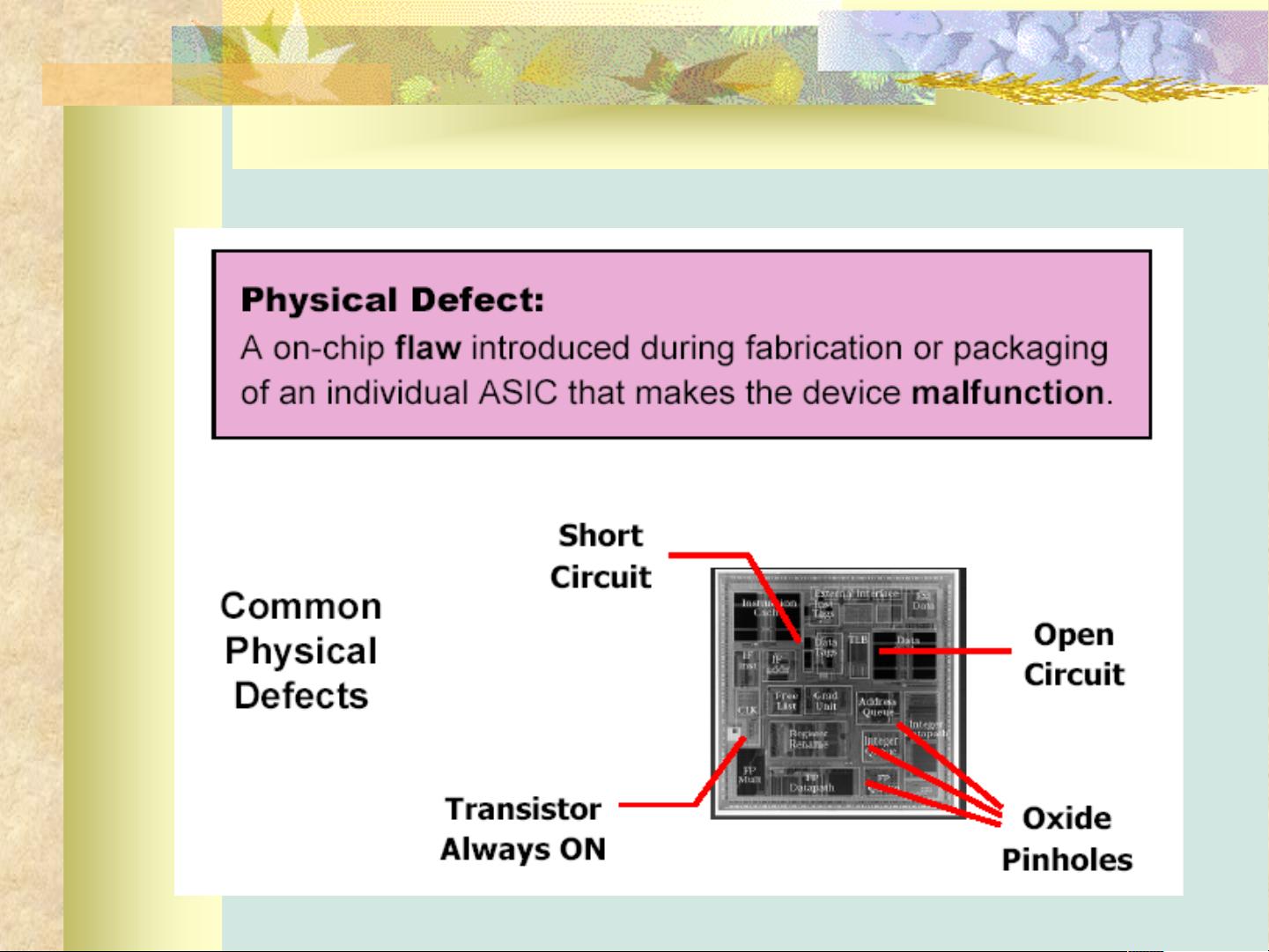

可测试性设计与ATPG(Automatic Test Pattern Generation)是VLSI设计方法中的一部分,旨在确保集成电路在制造之后能够通过测试,并保证其质量和可靠性。针对大规模集成电路的复杂性和规模,可测试性设计与ATPG是非常重要的。

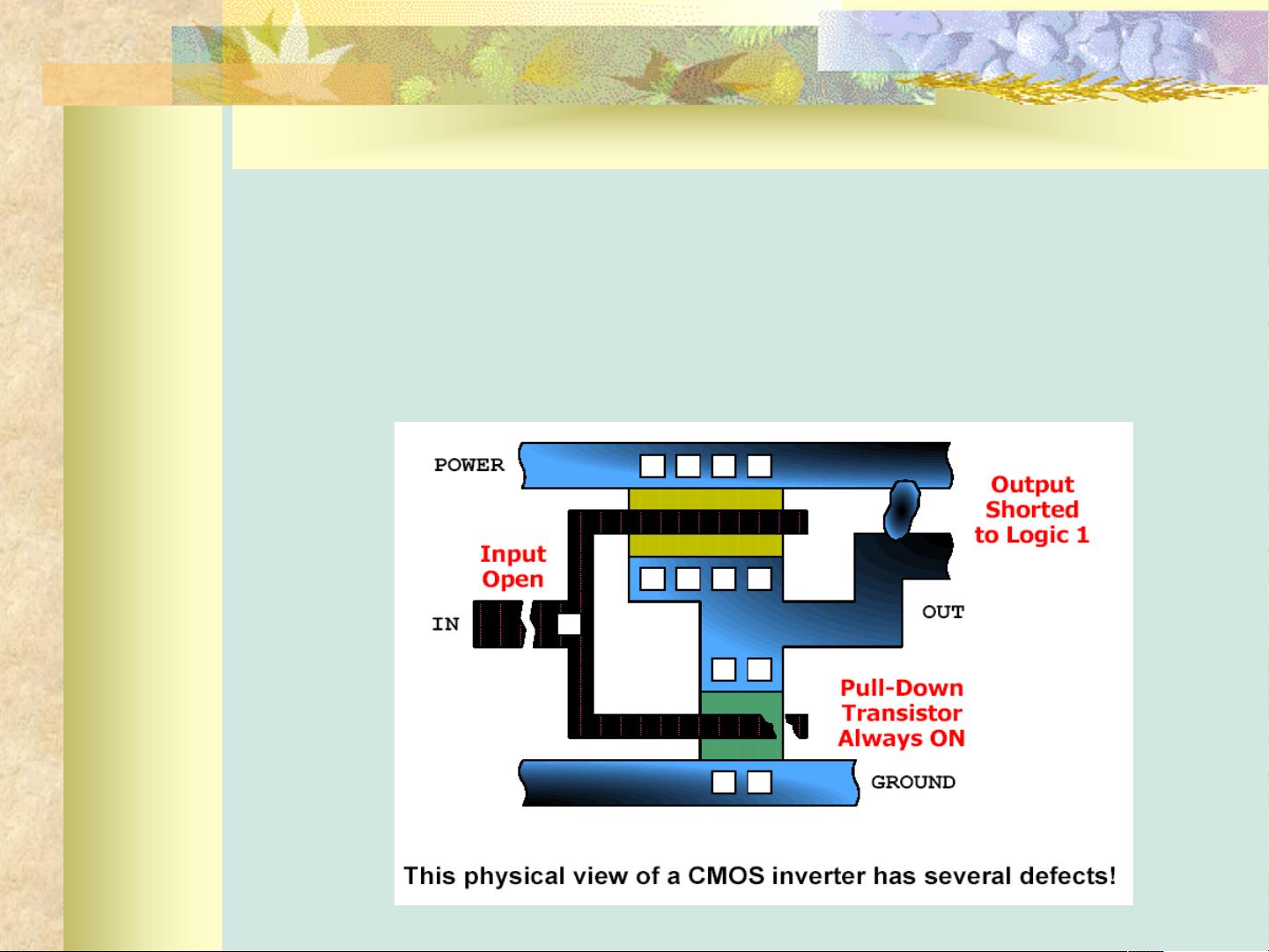

可测试性设计主要有两个方面的内容,即测试的可实现性和测试的有效性。测试的可实现性是指是否能够在设计的各个层次进行测试,包括系统级、逻辑级、电路级和物理级。测试的有效性是指设计能够通过测试并能够正确地检测到故障。

在VLSI设计中,设计抽象层次分为几个阶段,包括规格、可执行模型、RTL代码、门级网表和电路/互连级位图。不同的设计阶段有不同的测试要求和测试方式。

规格阶段是对设计需求和规格进行定义和描述的阶段,对测试而言,主要是对需求和规格进行测试用例的确定和生成。

可执行模型是在规格阶段基础上进行的功能模拟和验证,它能够实现设计的基本功能,并可以进行验证。在这一阶段,可以通过测试模块来测试可执行模型的正确性和可靠性。

RTL代码是硬件设计的实现代码,它是设计的逻辑描述和控制。在这一阶段,可以通过运行测试向量来验证RTL代码的功能和正确性。

门级网表是通过逻辑综合生成的,它是门电路和互连关系的描述。在这一阶段,可以通过测试向量来验证门级网表的正确性和可靠性。

电路/互连级位图是通过物理尺寸和排布信息生成的。在这一阶段,可以利用测试模块来测试电路/互连级位图的正确性和可靠性。

可测试性设计与ATPG中使用了许多工具和技术来提高测试的可实现性和有效性。常用的EDA工具包括Cadence和Synopsys等。

Cadence是一个综合性的EDA工具套件,它包括了从设计到验证的各个环节的工具。Cadence提供了用于逻辑设计、电路设计、芯片设计等各个方面的工具,可以帮助设计者进行可测试性设计和ATPG。

Synopsys是另一个著名的EDA工具提供商,它也提供了一系列的工具用于可测试性设计和ATPG。Synopsys的工具可以帮助设计师进行电路建模、仿真、综合和优化,从而提高测试的可实现性和有效性。

总之,可测试性设计与ATPG在VLSI设计方法中是非常重要的一部分。通过合理的设计,可以提高集成电路在制造之后的测试效率和质量,从而保证集成电路的可靠性和可用性。此外,使用合适的EDA工具也是非常关键的,可以帮助设计者进行可测试性设计和ATPG的各个步骤,并提供准确和可靠的测试策略和方法。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-05-10 上传

2024-05-09 上传

2021-06-25 上传

点击了解资源详情

2023-06-19 上传

冬泉谷的夏天

- 粉丝: 7

- 资源: 2

最新资源

- 毕业设计&课设--个人QT毕业设计项目 校园商铺.zip

- zharf:ZHARF项目

- lotus-openrpc-client:从OpenRPC定义生成的Typescript中的Lotus API客户端

- Excel模板客户信息登记表.zip

- system:简易易用的精简和快速的微型PHP系统库

- devrioclaro.github.io:DevRioClaro 没有 GitHub

- streams:应用程序可在体内传输清晰的视频。 Hecha en React con Redux

- automata.js:一个用于创建元胞自动机JavaScript库

- angular-course:使用angular的简单应用

- 毕业设计&课设--大学毕业设计,远程控制工具集,包含远程命令行,远程文件管理,远程桌面,已停止维护。.zip

- RMarkdown:分配

- 沙盒无服务器vpc-elasticearch

- Generative-Design-Systems-with-P5js:随附一系列视频的代码

- Data_analysis:使用JFreeChart库的Java数据分析程序

- Excel模板每日体温测量记录表.zip

- coppa:电晕进步和积极强化应用程序