Xilinx ISE 10.1 FPGA开发环境入门与行为仿真教程

需积分: 31 34 浏览量

更新于2024-07-26

收藏 733KB DOC 举报

ISE10.1使用教程简介

Xilinx ISE 10.1是一款广泛用于FPGA开发环境的工具,提供了全面的设计流程,包括项目创建、设计实现、仿真和编程。本教程将带你逐步了解如何在该环境下进行FPGA设计。

**步骤1:创建新项目**

首先,启动Xilinx ISE 10.1,通过桌面的快捷方式打开工程管理器(Project Navigator)。新建项目时,避免使用包含中文字符的工程名,以防止可能产生的兼容性问题。你需要填写工程名称和存储位置,选择适合的器件类型,例如本例中选择Virtex2P系列的XC2VP30,封装为ff896,速度等级设为-7。

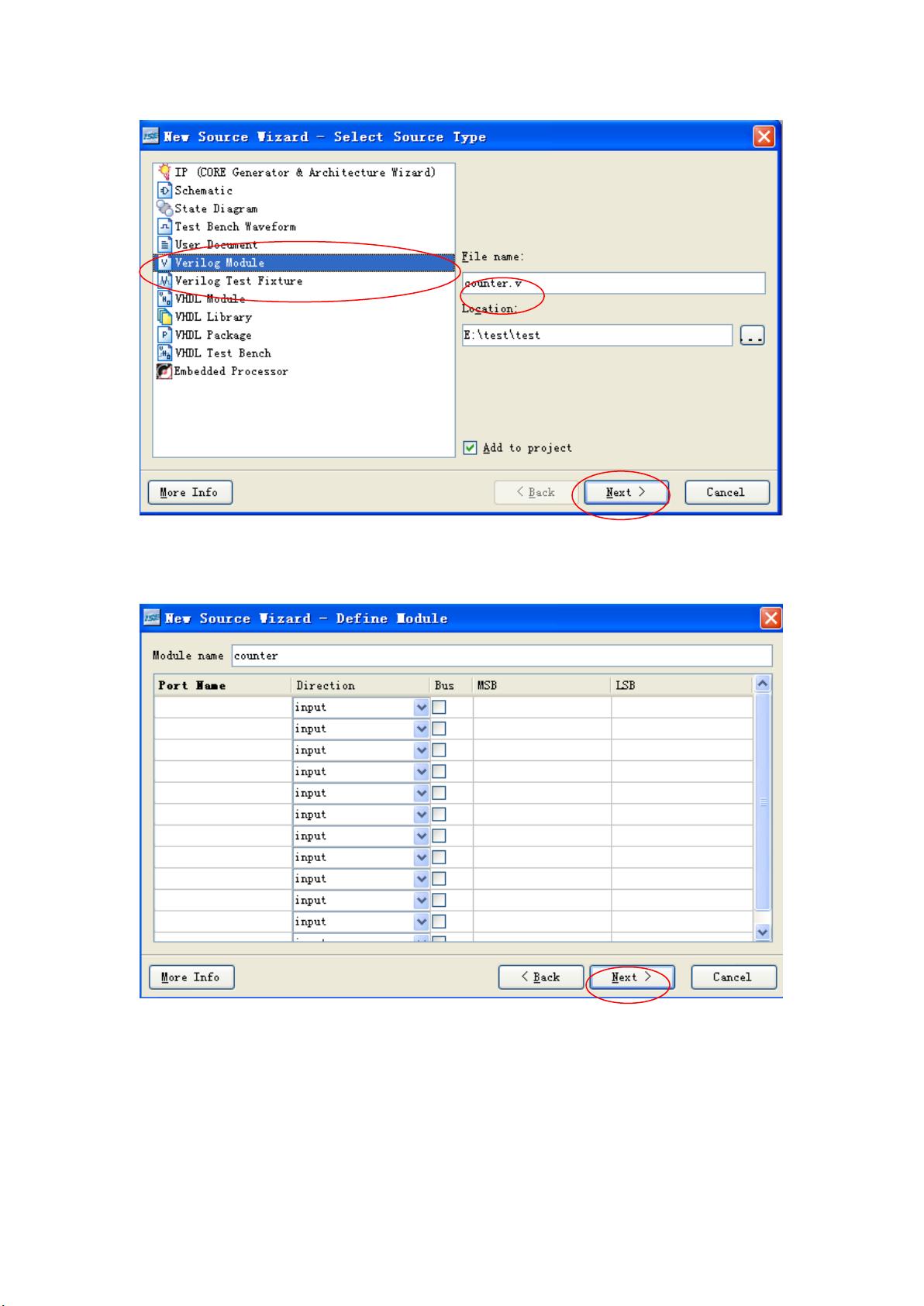

**步骤2:添加源文件**

进入项目后,点击"New Source",创建一个新的Verilog模块,如counter.v。在设置模块资源时,可以选择自动设置或手动配置输入输出端口。如果对默认设置满意,可以直接完成添加。

**步骤3:编写Verilog源代码**

在编辑器中双击添加的源文件,开始编写Verilog源程序,实现所需的逻辑功能。确保代码清晰、简洁,并遵循良好的编程习惯。

**步骤4:行为级仿真**

在Source窗口中,通过右键菜单选择"New Source",创建一个TestBench WaveForm用于行为级仿真。设置测试用例的对应源文件,并配置时钟参数,对于组合逻辑电路,确保在注释中明确说明时钟信号的处理。

**步骤5:设计约束设置**

在设计过程中,约束是至关重要的。通过点击相关选项,为设计过程设置适当的电气、功耗、性能等约束,确保编译后的硬件满足预期功能和性能要求。

**步骤6:综合设计**

完成上述步骤后,进入设计合成阶段(Synthesize),使用ISE 10.1的工具将Verilog源代码转换为FPGA硬件描述语言,生成适配目标器件的逻辑网表。

**步骤7:实施设计**

紧接着是布局和布线(Implement),将逻辑网表映射到实际的FPGA芯片上,生成硬件描述文件(bitstream)。

**步骤8:生成编程文件**

为了将设计加载到目标硬件,需要生成可编程文件,这一步通常涉及下载工具,如JTAG或ISP编程器。

**步骤9:使用ChipScope分析设计**

最后,利用ChipScope工具进行实时调试和性能分析,它允许用户观察FPGA内部信号的行为,帮助定位和解决问题。

总结,Xilinx ISE 10.1提供了完整的FPGA设计流程,从新项目创建到实际硬件验证,每个步骤都需要细心处理,以确保设计的正确性和效率。熟练掌握这些步骤,可以让你在FPGA开发领域游刃有余。

281 浏览量

点击了解资源详情

点击了解资源详情

281 浏览量

558 浏览量

1195 浏览量

2012-08-17 上传

440 浏览量

280 浏览量

aidongmingweizai

- 粉丝: 0

- 资源: 31

最新资源

- Homepare_App_1

- Cine-Data:使用TMDB API的电影搜索器和跟踪器

- brick:Brick Mag 原型

- 如何做好企业的培训(2个PPT)

- 企业大堂3D效果图模型

- 由Arduino提供支持的小吃自动售货机-项目开发

- dflex:JavaScriptJavaScript项目来操纵DOM元素

- Personal-Portfolio-Website:个人投资组合网站

- 集团管理及组织架构培训需求DOC

- color-file:根据模式和文件扩展名为迷你缓冲区中的文件着色

- Visual-Web:用于HTML,CSS和TypeScriptJavaScript的可视工具

- 电力设备新能源年月投资策略国内需求拉动下半年增长电网投资加速-36页.pdf.zip

- jdk-8u151-x64.zip

- doodle-jump

- OpenWrt-Newifi_D2:OpenWrt-Newifi_D2

- Spherium:运用 OpenGL 的力量,创造菊石、克莱因瓶和好奇的球体!-matlab开发