MPC8568EEC: Freescale Semiconductor 处理器规格

需积分: 9 95 浏览量

更新于2024-07-09

收藏 1.92MB PDF 举报

"MPC8568EEC.pdf是关于Freescale Semiconductor的MPC8568E和MPC8567E处理器的技术数据文档。文档主要涵盖了两者的主要特性,但重点可能会偏向MPC8568E,因为MPC8567E的不同之处会在特定部分被指出。MPC8567E相比MPC8568E缺少PCI-Express x8支持,没有eTSEC1、eTSEC2和TLU功能。文档结构包含了处理器的概述、电气特性、电源特性、输入时钟、复位初始化、DDR和DDR2 SDRAM接口、DUART、以太网接口和MII管理、本地总线、JTAG、I2C、PCI、高速串行接口(HSSI)、PCI-Express、串行快速IO、定时器、PIC、SPI、TDM/SI、UTOPIA/POS、HDLC、BISYNC、透明和同步UART、封装和管脚布局、时钟系统、热管理以及系统设计和订购信息等详细内容。"

本文档详尽阐述了MPC8568E和MPC8567E处理器的各项关键特性,为设计人员提供全面的技术指导。首先,MPC8568E概述部分将介绍处理器的基本架构、性能指标和核心功能。它可能包括PowerPC内核的详细信息,如处理速度、功耗优化以及指令集支持。

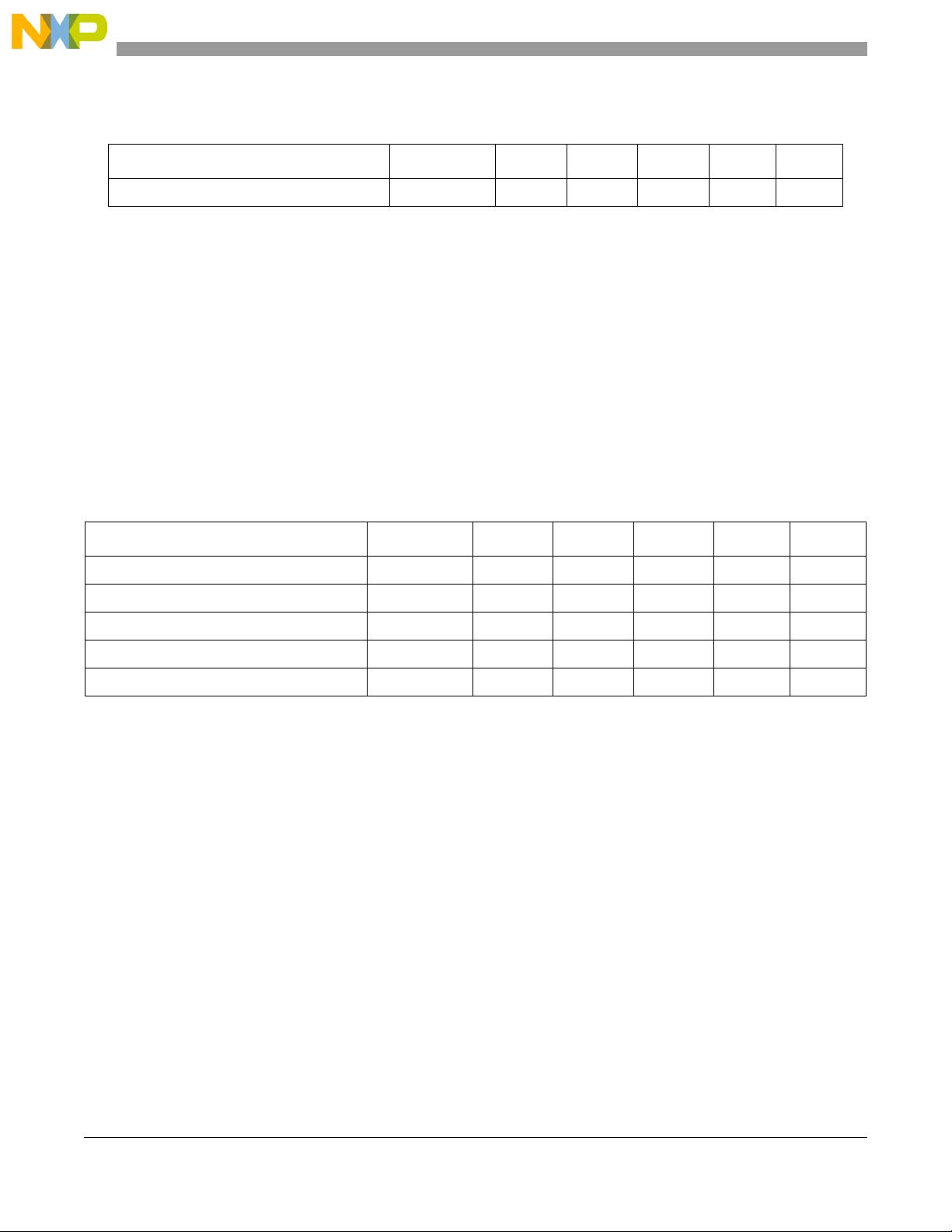

在电气特性部分,读者可以找到关于处理器工作电压、电流消耗以及与外部电路兼容性的详细数据。这有助于系统设计师确保处理器在各种工作条件下稳定运行。

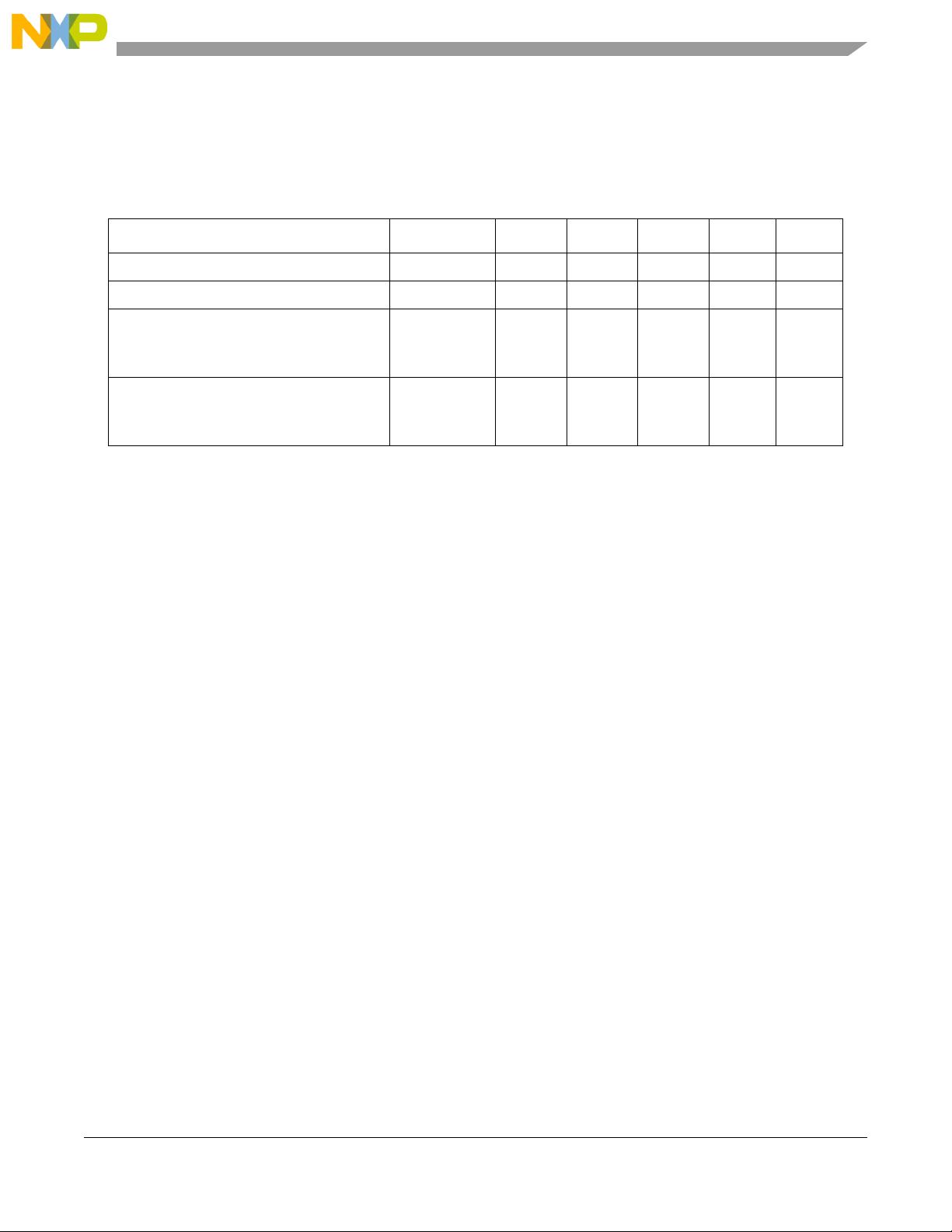

电源特性章节会列出不同电源轨的要求,包括启动顺序、电压稳定性和电流需求,这对于电源设计至关重要。输入时钟部分则讨论处理器所需的时钟源,包括时钟频率范围、抖动容限和时钟信号的布局建议。

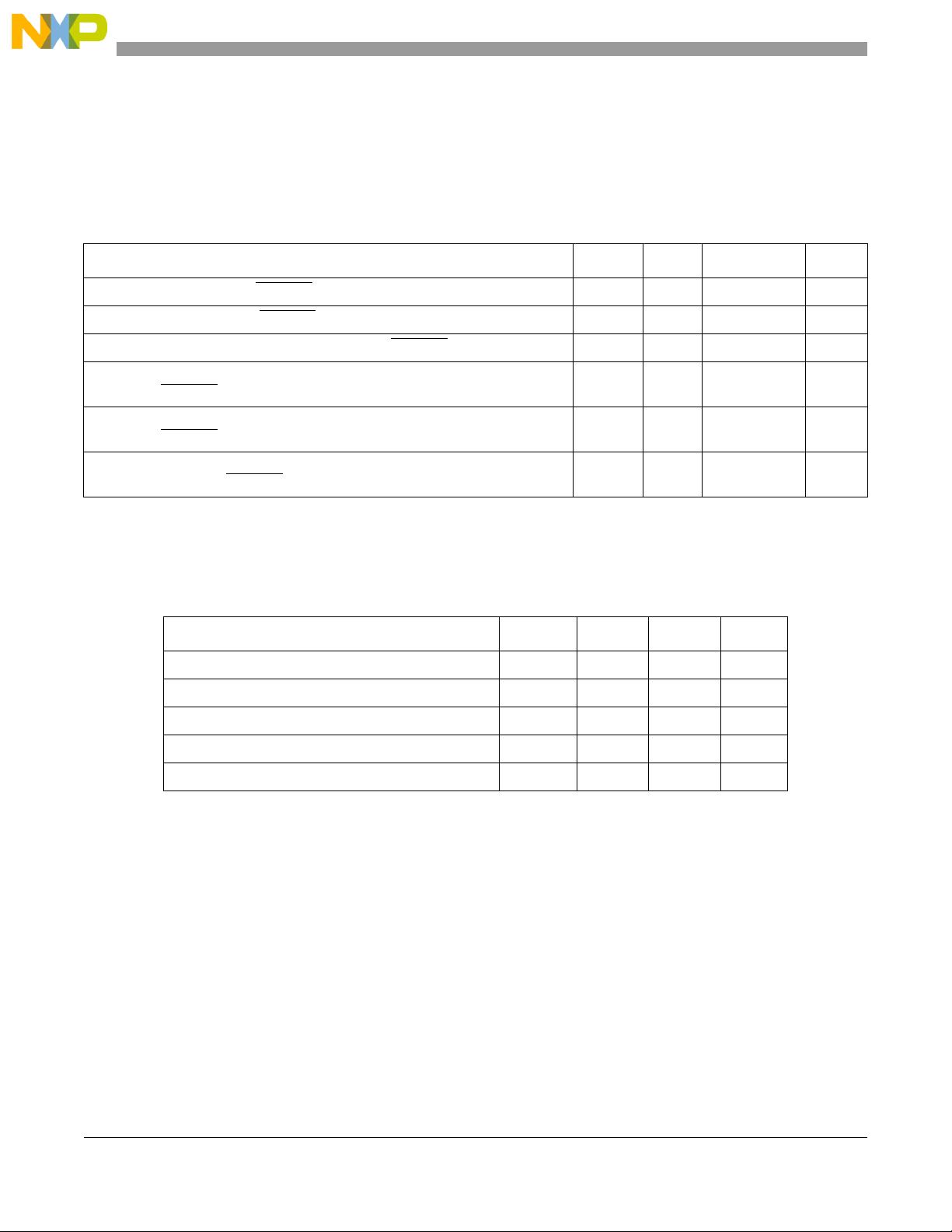

RESET初始化部分解释了如何正确复位处理器,包括复位信号的持续时间、类型和顺序,确保系统能够正确启动。DDR和DDR2 SDRAM部分将涵盖内存接口规范,包括地址和控制信号,以及内存时序参数。

DUART(双通用异步接收发送器)章节详细介绍了串行通信接口,而以太网接口和MII管理部分将阐述网络连接能力,包括物理层规格和管理接口。本地总线部分则关注处理器与其他组件的高速数据传输。

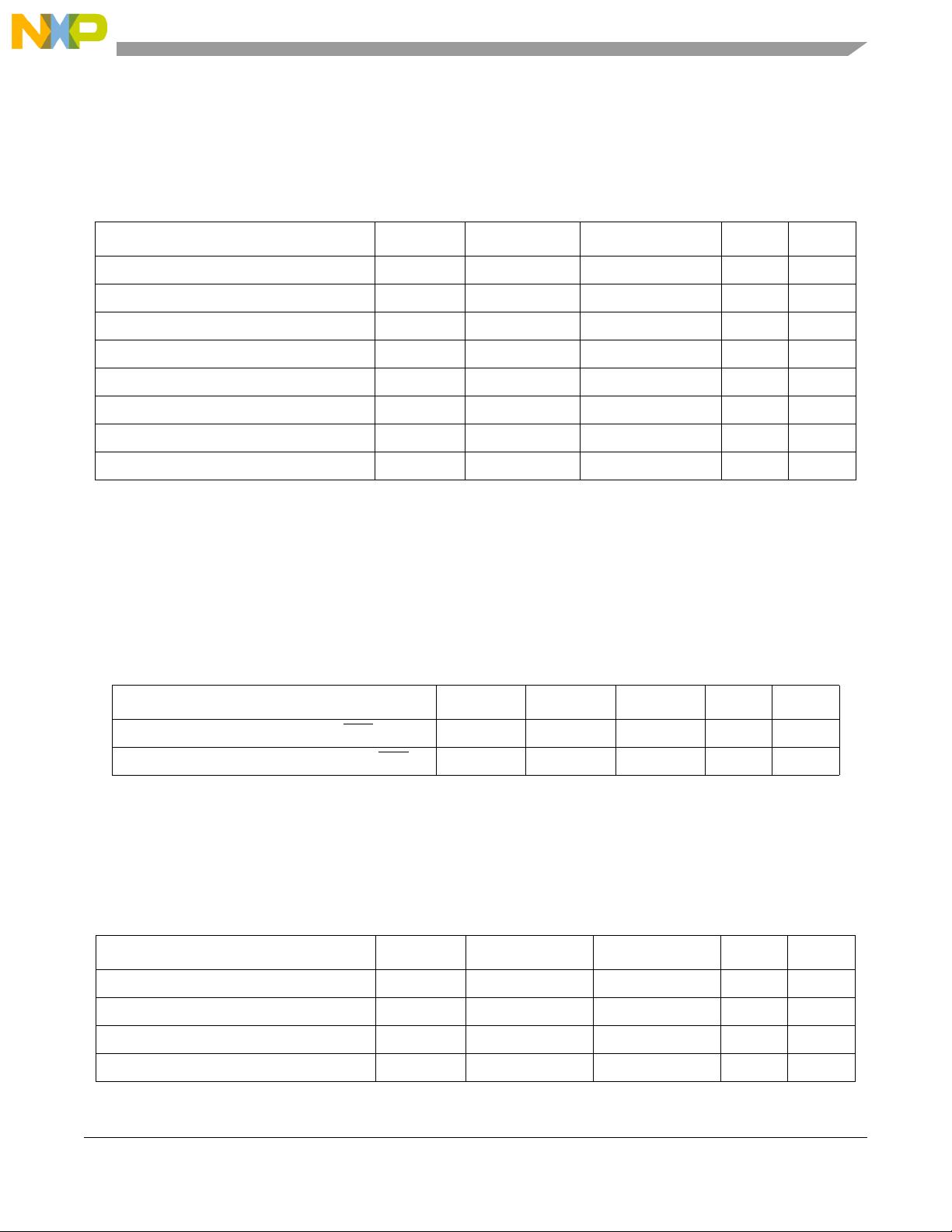

其余章节深入到PCI、高速串行接口、PCI-Express、串行快速IO等接口标准,以及定时器、中断控制器(PIC)、SPI、TDM/SI、UTOPIA/POS等通信协议。这些内容对理解处理器如何与外围设备交互至关重要。

最后,封装和管脚布局提供了物理连接的指导,时钟系统探讨了时钟生成和同步,热管理部分涉及散热设计,系统设计信息则给出实际应用中的注意事项,而订购信息则列出了可用的封装选项和订购代码。

这份技术文档是设计基于MPC8568E或MPC8567E的系统的工程师不可或缺的参考资料,它提供了从硬件接口到系统级集成的全方位信息。

135 浏览量

104 浏览量

109 浏览量

135 浏览量

2021-10-14 上传

2021-11-08 上传

109 浏览量

2023-10-30 上传

ppcust

- 粉丝: 38

- 资源: 728