超深亚微米工艺下的SoC设计:时延、耦合效应与串扰分析

版权申诉

135 浏览量

更新于2024-07-17

收藏 205KB PPT 举报

"SoC设计方法-超深亚微米工艺下以时延、耦合效应、串扰为焦点的讲解"

在当前的集成电路设计中,System-on-a-Chip(SoC)已经成为主流趋势,特别是在超深亚微米工艺环境下。SoC设计方法涉及到了诸多关键点,包括时延、耦合效应和串扰,这些都是影响SoC性能、功耗和可靠性的重要因素。

一、SoC的优点

SoC的主要优点在于其能够提供高性能、低功耗、小型化、轻量化以及低成本的解决方案。通过将处理器、嵌入式内存、可编程逻辑和各种应用特定电路组件集成在同一芯片上,SoC实现了硬件和软件的紧密耦合,大大提升了系统的整体效率。

二、SoC对EDA技术的挑战

随着SoC的发展,电子设计自动化(EDA)技术面临着前所未有的挑战。芯片规模的指数级增长导致设计复杂性的急剧增加,涵盖了多团队、多项目的设计工作。同时,设计领域中的挑战与机会并存,例如,芯片容量的增加(C1)带来了更多的设备和更高的功耗,异质集成的复杂性也随之上升。另一方面,特征尺寸的指数级减小(C2)带来了互联延迟、耦合噪声以及电磁干扰(EMI)等问题。

三、设计复杂性的双指数增长

这种复杂性的增长以双指数形式体现,即C1和C2的乘积。C1主要关注由于芯片容量增加带来的问题,如更多器件、更高功耗以及异质集成的挑战。而C2则聚焦于特征尺寸缩小带来的影响,如由于互联延迟增加、耦合噪声增大以及EMI问题的加剧。

四、生产力差距与芯片容量

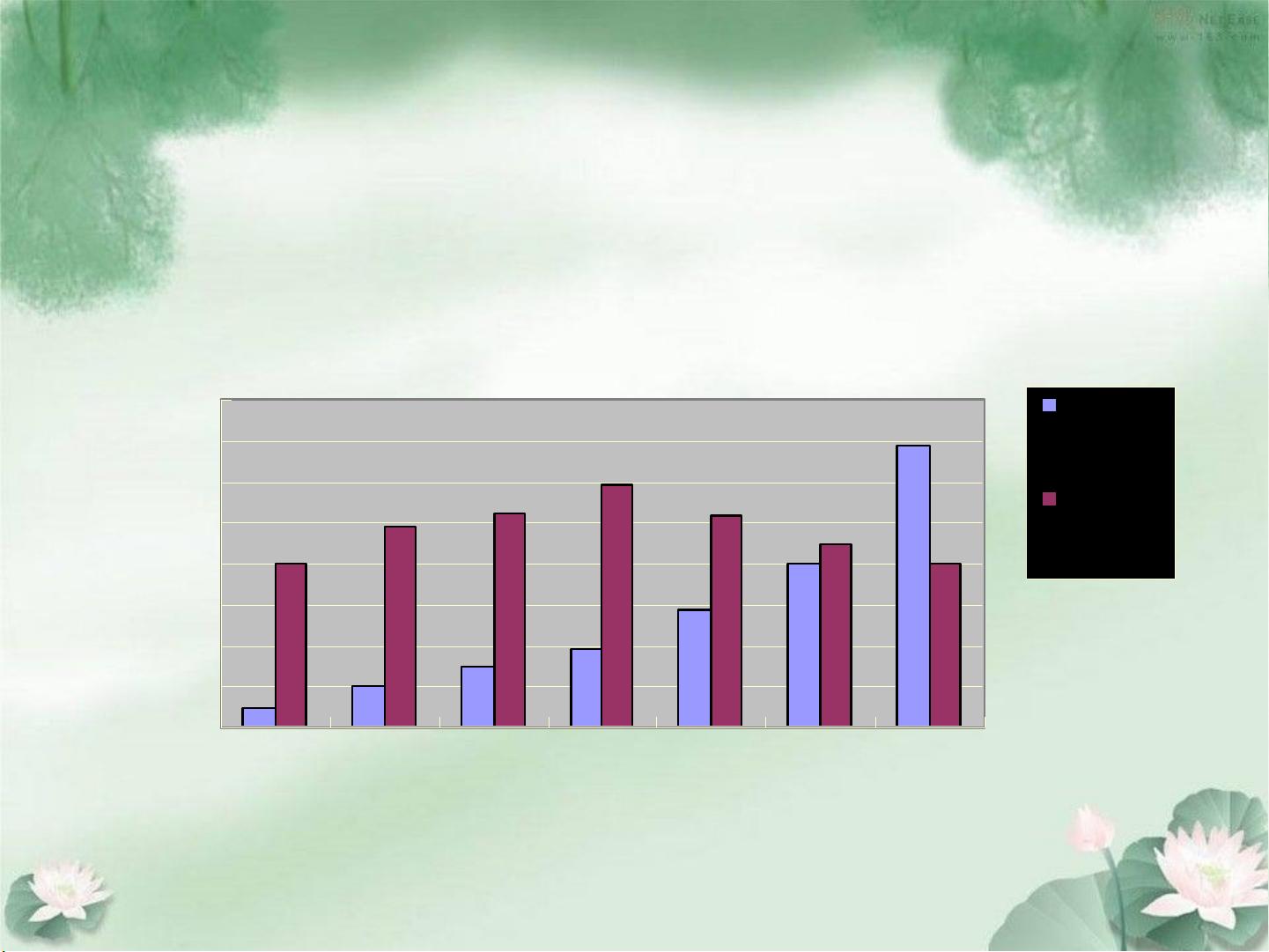

随着芯片容量的快速增长(每年约58%),设计师的生产力增长速度(每年约21%)却无法跟上,这导致了生产力差距的扩大。这意味着在设计复杂度不断提高的同时,需要找到更高效的设计方法和工具来弥补这种差距。

五、SoC的内涵与外延

SoC的核心特征是它能够在一个单一的超大规模集成电路中实现复杂系统功能。使用超深亚微米工艺技术,可以实现更高的集成度。SoC通常包含一个或多个嵌入式CPU或数字信号处理器,这些处理器可以处理复杂的计算任务,并与其他硬件模块协同工作,以实现高效的系统运行。

SoC设计在超深亚微米工艺下面临众多挑战,如时延优化、耦合效应的抑制以及串扰的管理等。为了应对这些挑战,设计师必须掌握先进的EDA工具和技术,同时在设计流程中充分考虑系统级优化,以确保SoC的性能、功耗和可靠性达到预期标准。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-08-14 上传

2019-07-22 上传

2021-09-19 上传

2019-09-07 上传

2019-09-10 上传

2019-07-22 上传

Dambulla

- 粉丝: 7

- 资源: 3万+

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新