5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

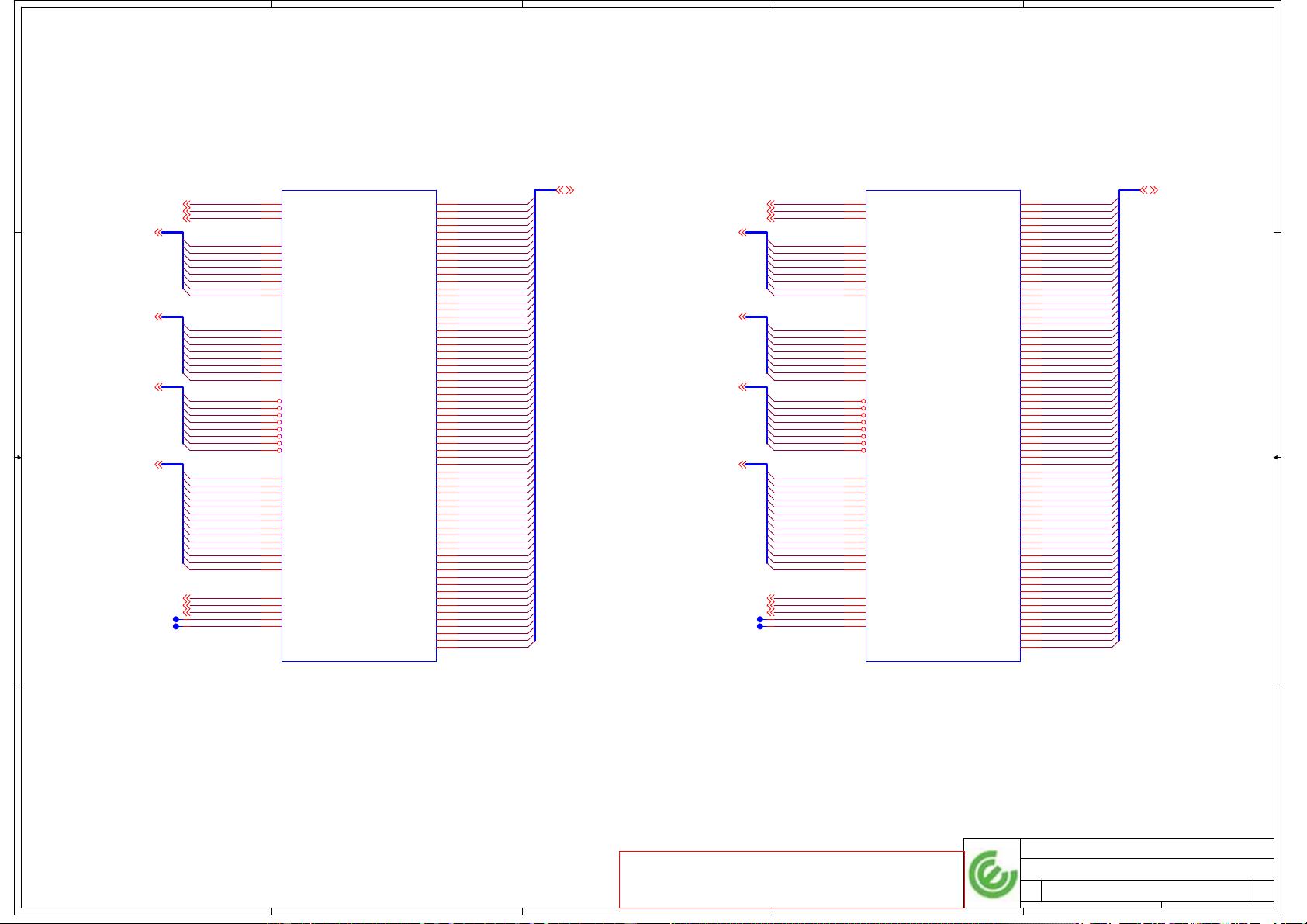

U6_AB1

U6_A6

U6_D2

VSSA_TVBG

+3VRUN_ATV

+3GPLL_R

+2.5V_CRTDAC

+2.5V_CRTDAC

VCCD_LVDS

VSSA_TVBG

+1.5V_RUN_HPLL

+1.5V_RUN_DPLLB

+1.5V_RUN

+1.5V_RUN_DPLLA

+1.5V_RUN

+1.5V_RUN+1.5V_RUN

+1.5V_RUN_MPLL

+1.05V_VCCP

+1.5V_RUN

+1.5V_RUN

+1.5V_RUN_DPLLB

+1.5V_RUN_DPLLA

+1.5V_RUN

+1.5V_RUN_MPLL

+3.3V_RUN

+1.5V_RUN_HPLL

+1.5V_RUN_3GPLL

+1.5V_RUN

+3.3V_RUN

+2.5V_RUN

+1.5V_RUN_QTVDAC

+3VRUN_TVDACA

+3VRUN_TVDACC

+3V_TVDAC

+3VRUN_ATVBG

+3.3V_RUN

+1.5V_RUN

VCCA_LVDS

+2.5V_RUN

+1.05V_VCCP

+1.5V_RUN

+3VRUN_ATVBG

+3VRUN_TVDACA

+1.5V_RUN

+1.5V_RUN

+1.5V_RUN

+1.5V_RUN_PCIE

+2.5V_RUN

+2.5V_RUN

+2.5V_RUN

+1.05V_VCCP +1.5V_RUN

+1.5V_RUN_3GPLL

+1.5V_RUN

+1.5V_RUN

VCCA_LVDS

VCCTX_LVDS

+3VRUN_TVDACB

+3VRUN_TVDACB

+3VRUN_TVDACC

+2.5V_RUN

+1.5V_RUN_TVDAC

+1.5V_RUN_TVDAC+1.5V_RUN +1.5V_RUN_QTVDAC

VCCTX_LVDS

+2.5V_RUN

Title

Size Document Number Rev

Date: Sheet

of

LA-2881P

2.0

Calistoga(4 of 6)

13 62Tuesday, December 13, 2005

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

40mA Max.

45mA Max.45mA Max.

40mA Max.

Should be placed on same side. No Vias.

W=30 mils

CRB 270uF

Route VSSACRTDAC gnd from GMCH to

decoupling cap ground lead and then

connect to the gnd plane.

CRTDAC: Route caps within

250mil of GMCH. Route FB

within 3" of Calistoga

Route VSSA_TVBG GND from GMCH to

decoupling cap ground lead and then

connect to the GND plane.

C630, C617, C611, C627,

C703, C704, C707 replace

by 0 ohm 0805 resistor

close pin A38

Note : C588, C564 No stuff for Ext. VGA.

Stuff for Int. VGA.

L54, L53 use 0_0805_5% resistor

for Int. VGA as Travis.

CRT DAC Voltge Follower Circuit - 700mV

TV DAC Voltge Follower Circuit - 700mV

close pin A6

close pin D2/AB1

NOTE: Populate D4, R54, D2 and R52 for UMA Implemetation.

NOTE:

Follow Intel Layout Guideline

toplace 4.7uF, 10uF, 22uF,

0.1uF and 22nF within 250 mils

from Calistoga.

FB

Route +2.5V_RUN from GMCH pinG41 to

decoupling cap(C567)<200mil to the edge

0.1uF should be placed < 200 mils within its pins

close pin B30/C30/A30

NOTE:

1@ is for UMA Implemetation.

3@ is for Discrete Implementation.

+3V_TVDAC

Refer to the latest Intel layout check list for Calistoga de-couping capacitors layout placement

4.7uF, 10uF and 22uF should be placed < 500 mils within its pins

0.1uF should be placed < 200 mils within its pins

22nF should be placed within its pins

10uF should be placed in cavity

C612

0.1U_0402_16V4Z~D1@

1

2

C645

22U_0805_6.3VAM~D

1

2

R634

0_0402_5%~D1@

12

+

C588

470U_D2_2.5VM~D1@

1

2

R90

0_0402_5%~D

3@

12

D2

MMBD4148-7-F_SOT23-3~D1@

1

3

2

R636

0_0603_5%~D3@

C567

0.1U_0402_16V4Z~D

1

2

R659

0_0402_5%~D3@

12

D4

MMBD4148-7-F_SOT23-3~D1@

1

3

2

C581

0.22U_0402_10V4Z~D

1

2

C568

0.1U_0402_16V4Z~D

1

2

R642

0_0603_5%~D1@

R633

0_0402_5%~D3@

12

C611

22n_0805_25V1@

1 2

3

C621

0.1U_0402_16V4Z~D1@

1

2

L55

BLM18PG181SN1_0603~D

1 2

C609

0.022U_0402_16V7K~D1@

1

2

C590

0.1U_0402_16V4Z~D

1

2

C646

22U_0805_6.3VAM~D

1

2

C708

22U_0805_6.3VAM~D

3@

1

2

R76

0_0603_5%~D 1@

1 2

C703

22n_0805_25V1@

1 2

3

C613

4.7U_0603_6.3V6M~D

@

1

2

C565

10U_0805_4VAM~D

1

2

L52

BLM21PG600SN1D_0805~D

12

L60

BLM18AG121SN1D_0603~D

12

C580

0.1U_0402_16V4Z~D

1

2

C617

22n_0805_25V1@

1 2

3

P O W E R

U6H

CALISTOGA A3_FCBGA1466~D

VCC_SYNC

H22

VCCTX_LVDS0

B30

VCCTX_LVDS1

C30

VCC3G0

AB41

VCC3G1

AJ41

VCC3G2

L41

VCC3G3

N41

VCC3G4

R41

VCC3G5

V41

VCC3G6

Y41

VCCA_3GBG

G41

VSSA_3GBG

H41

VCCA_3GPLL

AC33

VCCTX_LVDS2

A30

VCCA_LVDS

A38

VSSA_LVDS

B39

VCCA_MPLL

AF2

VCCA_TVBG

H20

VSSA_TVBG

G20

VCCA_TVDACA0

E19

VCCA_TVDACA1

F19

VCCA_TVDACB0

C20

VCCA_TVDACB1

D20

VCCA_TVDACC0

E20

VCCA_TVDACC1

F20

VCCAUX1

AF31

VCCAUX2

AE31

VCCAUX3

AC31

VCCAUX4

AL30

VCCAUX5

AK30

VCCAUX6

AJ30

VCCAUX7

AH30

VCCAUX8

AG30

VCCAUX9

AF30

VCCAUX10

AE30

VCCAUX11

AD30

VCCAUX12

AC30

VCCAUX13

AG29

VCCAUX14

AF29

VCCAUX15

AE29

VCCAUX16

AD29

VCCAUX17

AC29

VCCAUX18

AG28

VCCAUX19

AF28

VCCAUX20

AE28

VTT0

AC14

VTT1

AB14

VTT2

W14

VTT3

V14

VTT4

T14

VTT5

R14

VTT6

P14

VTT7

N14

VTT8

M14

VTT9

L14

VTT10

AD13

VTT11

AC13

VTT12

AB13

VTT13

AA13

VTT14

Y13

VTT15

W13

VTT16

V13

VTT17

U13

VTT18

T13

VTT19

R13

VTT20

N13

VTT21

M13

VTT22

L13

VTT23

AB12

VTT24

AA12

VTT25

Y12

VTT26

W12

VTT27

V12

VTT28

U12

VTT29

T12

VTT30

R12

VTT31

P12

VTT32

N12

VTT33

M12

VTT34

L12

VTT35

R11

VTT36

P11

VTT37

N11

VTT38

M11

VTT39

R10

VTT40

P10

VTT41

N10

VTT42

M10

VTT43

P9

VTT44

N9

VTT45

M9

VTT46

R8

VTT47

P8

VTT48

N8

VTT49

M8

VTT50

P7

VTT51

N7

VTT52

M7

VTT53

R6

VTT54

P6

VTT55

M6

VTT56

A6

VTT57

R5

VTT59

N5

VTT60

M5

VTT61

P4

VTT62

N4

VTT63

M4

VTT64

R3

VTT65

P3

VTT66

N3

VTT67

M3

VTT68

R2

VTT69

P2

VTT70

M2

VTT71

D2

VTT72

AB1

VTT73

R1

VTT74

P1

VTT75

N1

VTT76

M1

VCCA_CRTDAC0

E21

VCCA_CRTDAC1

F21

VSSA_CRTDAC2

G21

VCCA_DPLLA

B26

VCCA_DPLLB

C39

VCCA_HPLL

AF1

VCCD_HMPLL0

AH1

VCCD_HMPLL1

AH2

VCCD_LVDS0

A28

VCCD_LVDS1

B28

VCCD_LVDS2

C28

VCCD_TVDAC

D21

VCCDQ_TVDAC

H19

VCCHV0

A23

VCCHV1

B23

VCCHV2

B25

VCCAUX21

AH22

VCCAUX22

AJ21

VCCAUX23

AH21

VCCAUX24

AJ20

VCCAUX25

AH20

VCCAUX26

AH19

VCCAUX27

P19

VCCAUX28

P16

VCCAUX29

AH15

VCCAUX30

P15

VCCAUX31

AH14

VCCAUX32

AG14

VCCAUX33

AF14

VCCAUX34

AE14

VCCAUX35

Y14

VCCAUX36

AF13

VCCAUX37

AE13

VCCAUX38

AF12

VCCAUX39

AE12

VCCAUX40

AD12

VCCAUX0

AK31

VTT58

P5

C603

0.022U_0402_16V7K~D

1@

1

2

R670

0_0402_5%~D3@

12

R666

0_0402_5%~D3@

12

+

C147

220U_D2_4VM~D

1

2

C597

10U_0805_6.3V6M~D

1

2

C579

0.1U_0402_16V4Z~D1@

1

2

R680

0_0402_5%~D3@

12

C707

22n_0805_25V1@

1 2

3

R52

10_0603_5%~D1@

1 2

C117

10U_0805_4VAM~D1@

1

2

+

C564

470U_D2_2.5VM~D1@

1

2

R624

0.5_0805_1%~D

1 2

R89

0_0402_5%~D

1@

12

+

C649

220U_D2_4VM~D

1

2

R54

10_0603_5%~D1@

1 2

R660

0_0402_5%~D3@

1 2

L54

10U_CK2125 100M-T_20%_0805~D

12

C704

22n_0805_25V1@

1 2

3

C615

0.1U_0402_16V4Z~D1@

1

2

C626

4.7U_0603_6.3V6M~D

1

2

C571

0.01U_0402_16V7K~D1@

1

2

C148

10U_0805_4VAM~D

1

2

C99

0.1U_0402_16V4Z~D1@

1

2

C616

0.1U_0402_16V4Z~D1@

1

2

L53

10U_CK2125 100M-T_20%_0805~D

12

C610

0.1U_0402_16V4Z~D

1

2

R676

0_0402_5%~D3@

12

C600

0.022U_0402_16V7K~D

1@

1

2

C639

0.1U_0402_16V4Z~D

1

2

C105

0.1U_0402_16V4Z~D

1

2

C587

0.01U_0402_16V7K~D1@

1

2

C604

0.1U_0402_16V4Z~D

1@

1

2

L7

BLM18PG181SN1_0603~D1@

1 2

C605

10U_0805_6.3V6M~D1@

1

2

C59

0.47U_0402_10V4Z~D

1

2

C629

0.1U_0402_16V4Z~D

1@

1

2

C570

0.1U_0402_16V4Z~D

1

2

R640

0_0603_5%~D

3@

C624

0.1U_0402_16V4Z~D

1

2

R638

0_0603_5%~D1@

C149

10U_0805_4VAM~D

1

2

C129

4.7U_0603_6.3V6M~D1@

1

2

L8

BLM21PG600SN1D_0805~D

12

C572

0.1U_0402_16V4Z~D1@

1

2

R658

0_0402_5%~D3@

1 2

L59

BLM18AG121SN1D_0603~D

12

C627

22n_0805_25V1@

1 2

3

C633

0.47U_0402_10V4Z~D

1

2

C607

2.2U_0603_6.3V6K~D

1

2

L56

BLM18PG181SN1_0603~D1@

1 2

C638

0.1U_0402_16V4Z~D

1

2

C641

0.22U_0402_10V4Z~D

1

2

C630

22n_0805_25V1@

1 2

3