0.18μm CMOS工艺下高速高精度A/D转换器比较器设计与优化

168 浏览量

更新于2024-08-30

1

收藏 544KB PDF 举报

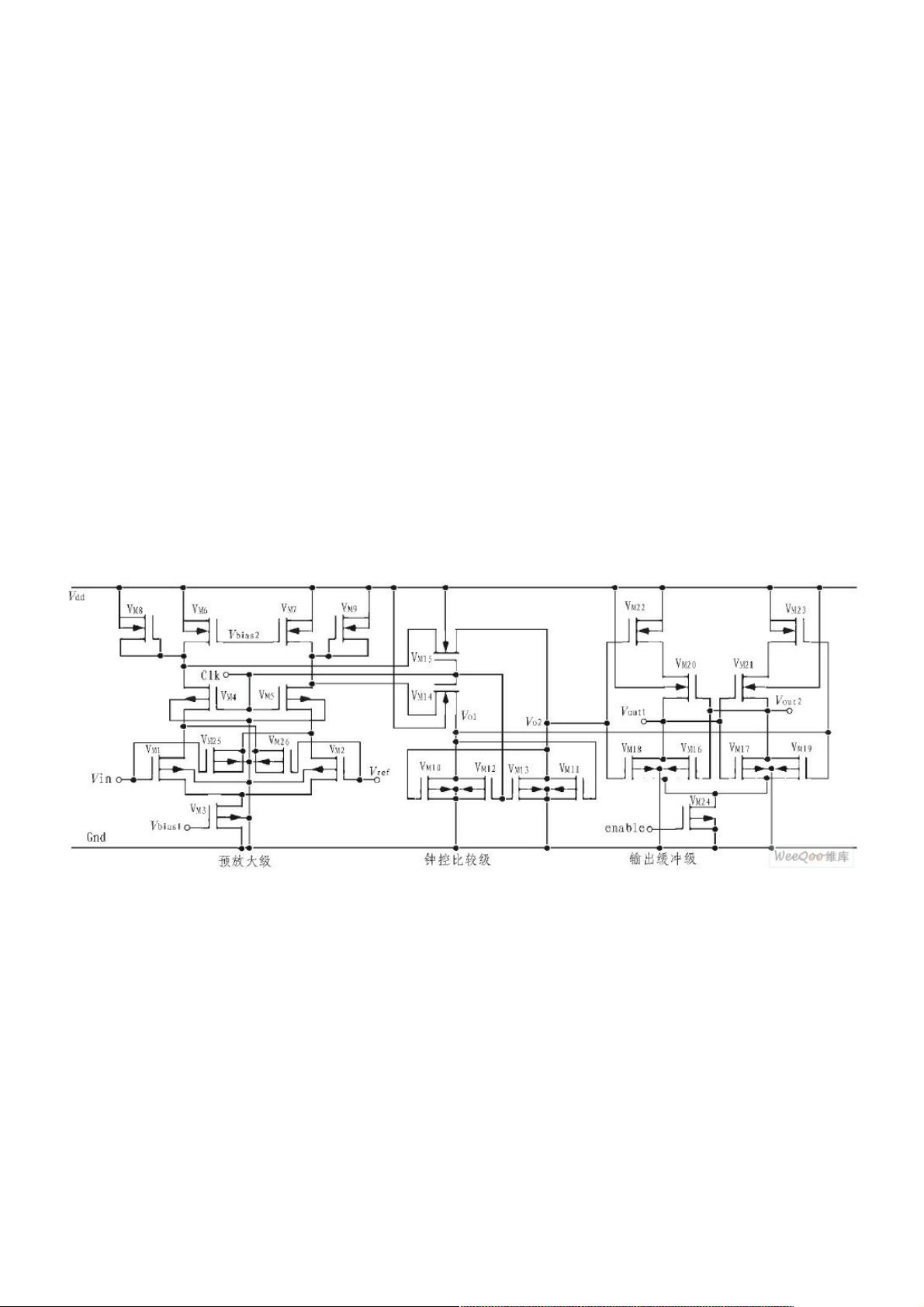

高速高钟控比较器的设计旨在提升10位高分辨率A/D转换器的性能,满足现代通信和信号处理系统对高精度和高速度的需求。设计的核心在于优化速度和回馈噪声,以实现更优秀的系统性能。

首先,采用了前置预放大器结构,这一设计的关键在于它的高比较精度。预放大器的作用是增强输入信号的幅度,使得后续的比较过程更为准确,从而减少量化误差,提高转换的可靠性。预放大器的引入减少了信号失真,确保了高分辨率的实现。

为了进一步提升速度,设计师引入了两级正反馈环路结构的比较锁存器。正反馈环路通过自我增强的方式,加快了信号的切换速度,使得比较器能够以高达300 MHz的工作频率快速响应输入信号的变化,这对于实时数据采集和处理至关重要。

在噪声控制方面,隔离技术和互补技术的应用起到了关键作用。隔离技术减少了外部噪声对内部电路的影响,而互补技术则通过使用互补对称结构,降低了电源噪声和其他形式的噪声,确保了输出的稳定性和准确性。结果表明,LSB(最小可分辨位)达到了±1 mV,这是衡量比较器噪声性能的重要指标。

整个电路设计基于TSMC 0.18 μm CMOS标准工艺,这是一种成熟的半导体制造工艺,能提供良好的集成度和性能。使用Cadence Spectre模拟器进行仿真验证,验证了设计的可行性,包括360 ps的传输延时和2.6 mW的低功耗,这些都是衡量高速比较器效率的重要参数。

最后,这种设计不仅适用于10位高精度模数转换器,也适用于模拟IP核,因为它能够提供足够的性能来支持复杂信号处理任务,如医学图像处理和高速数据变换,甚至QAM调制器等应用。通过对传统方法的改进,本文的比较器结构能够在保持高速度的同时,显著改善了噪声性能,对于提高整体系统的性能有着显著的贡献。

421 浏览量

421 浏览量

156 浏览量

250 浏览量

276 浏览量

421 浏览量

132 浏览量

276 浏览量

327 浏览量