使用ISE设计Xilinx FIR滤波器IP核及Matlab验证

需积分: 31 191 浏览量

更新于2024-09-09

收藏 469KB DOC 举报

"这篇文档介绍了如何使用Xilinx ISE 12.4设计FIR滤波器IP核,并通过Matlab进行验证。整个过程包括创建新项目、添加源代码、配置滤波器参数以及生成Verilog代码。"

在数字信号处理领域,Xilinx IP核设计FIR滤波器是一种常见的任务,用于实现硬件级别的高效滤波功能。FIR(Finite Impulse Response,有限冲激响应)滤波器因其线性相位特性、可设计灵活性以及易于硬件实现而被广泛使用。

Xilinx ISE(Integrated Software Environment)是Xilinx公司提供的一个综合设计环境,用于开发基于FPGA(Field Programmable Gate Array)的数字系统。在版本12.4中,设计FIR滤波器IP核的步骤如下:

1. **启动ISE并创建新项目**:打开ISE,选择“File” -> “New Project”,根据提示设置项目名称和保存位置,然后点击“Next” -> “Finish”。

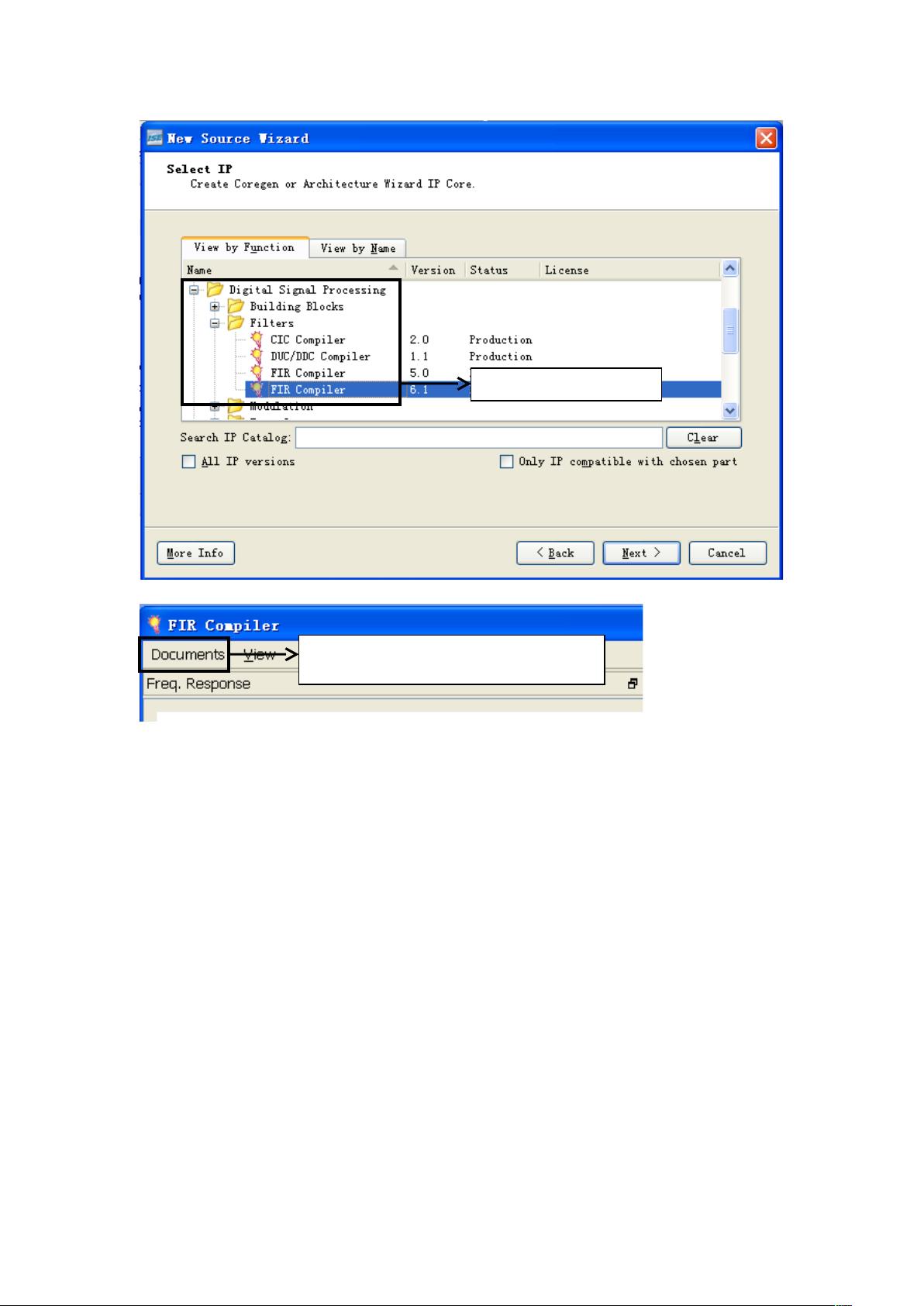

2. **添加源文件**:在设计启动视图中,右键点击空白区域,选择“New Source”。在弹出的对话框中,选择合适的文件类型,如VHDL或Verilog模块,然后点击“Next” -> “Finish”。

3. **配置FIR滤波器**:在新添加的源文件中,选择“IP Catalog”,搜索并添加FIR Filter IP核。配置滤波器的参数,如滤波器类型(低通、高通、带通等)、采样率、阶数、截止频率等。

4. **生成IP核**:完成配置后,点击“Generate”,这将生成一个定制的FIR滤波器IP核。在设计启动视图中,可以右键选择“New Source”将IP核添加到项目中。

5. **编辑Verilog代码**:生成的IP核会自动生成相应的Verilog代码,例如以下示例中的`fir`模块。这段代码定义了输入和输出接口,以及IP核内部的数据流。

```verilog

module fir (

input s_axis_data_tready,

input s_axis_data_tvalid,

output m_axis_data_tvalid,

input aclk,

output [23:0] m_axis_data_tdata,

input [15:0] s_axis_data_tdata

);

...

endmodule

```

6. **验证与仿真**:为了确认FIR滤波器的功能正确性,通常会使用Matlab等软件进行滤波器设计和性能验证。在Matlab中,可以创建理想的FIR滤波器系数,然后将这些系数导入到Xilinx IP核中,最后通过仿真比较硬件实现的结果与Matlab期望结果的一致性。

通过以上步骤,一个定制的FIR滤波器IP核就设计完成了,可以在FPGA上实现高效的数字信号处理。这种硬件实现相比纯软件实现,具有更高的速度和更低的延迟,适合实时信号处理应用。

515 浏览量

138 浏览量

2022-07-15 上传

101 浏览量

595 浏览量

668 浏览量

264 浏览量

saisai111

- 粉丝: 1

最新资源

- ckplayer5.9:具有广告功能的互联网视频播放器

- TCS Django示例应用:基础待办事项功能演示

- Idea插件GsonFormat:轻松实现JSON转实体类

- CLISP 2.49 for Windows - 多语言开发环境与调试工具

- SkyCallSetup v2.1.0.32:Skype极品网关驱动,多方通话与清晰音质

- Ansible-tahrir.zip:自动化引擎助力开放式徽章发布

- 婚纱摄影系列YFCMS伪静态功能正式上线

- Brayan Solorzano的CSS技术博客

- G2刷机工具与驱动下载指南

- Java实现QQ屏幕截图工具的设计开发

- 摩托罗拉FR68/FR6000条码SDK包使用指南

- am-grid: 使用Flexbox构建的实验性网格系统

- Reddit平台的HTML技术实现解析

- 一键获取并复制IE浏览器中所有网页链接

- 谭版C语言课本习题深度解析

- ROS节点事件传递机制:C++与Python节点的协同工作