XILINX FIR Compiler: 设计高性能FIR滤波器IP核

下载需积分: 50 | PDF格式 | 2.22MB |

更新于2024-07-20

| 186 浏览量 | 举报

"XILINX 官方FIR滤波器设计说明文档"

这篇文档是关于XILINX公司的FIR Compiler,这是一个专门用于FPGA(Field Programmable Gate Array)设计的LogiCORE IP核心。FIR Compiler为用户提供了一种通用接口,可以生成高度参数化、面积高效且高性能的FIR(Finite Impulse Response)滤波器。它支持多种FPGA系列,包括Virtex-6、Virtex-5、Virtex-4、Spartan-6以及Spartan-3系列。

FIR滤波器是一种数字信号处理技术,广泛应用于通信、音频处理、图像处理等领域,用于消除信号噪声、平滑数据或进行频谱分析。FIR Compiler的核心特性包括:

1. **高度可配置性**:用户可以根据需求调整滤波器的参数,如滤波器阶数、滤波类型、性能要求等。

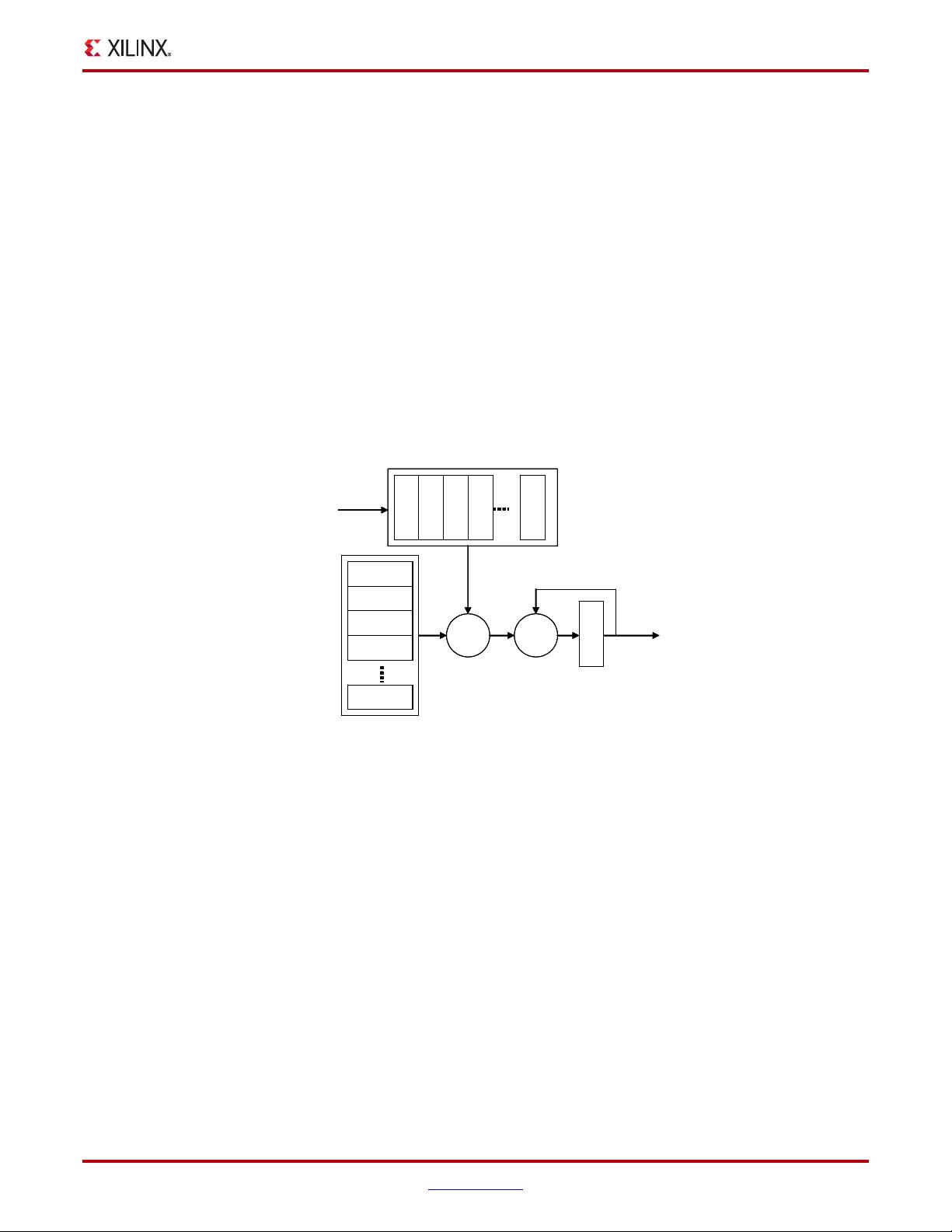

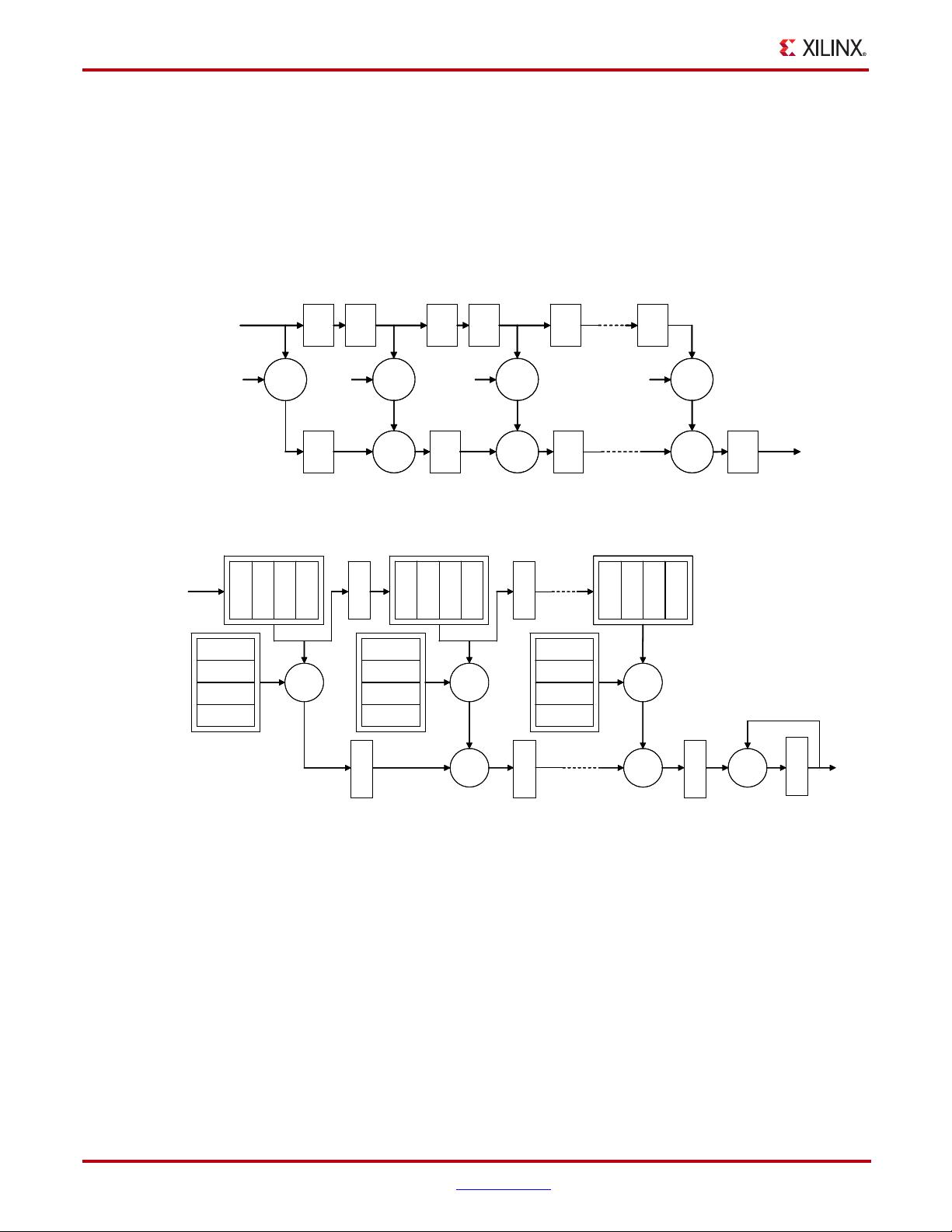

2. **架构选择**:支持两种不同的实现架构,即Multiply-Accumulate (MAC) 和 Distributed Arithmetic (DA)。MAC结构通常用于实现精确计算,而DA架构则可能在面积效率上更具优势。

3. **多种滤波器类型**:不仅可以实现标准的FIR滤波,还包括了多相解调器、多相插值器、半带滤波器、半带解调器、希尔伯特变换、多相滤波器组和插值滤波器等多种功能。

4. **高性能**:设计的目标是提供高吞吐量和低延迟,以满足实时信号处理的需求。

5. **广泛的设备支持**:不仅限于高端的Virtex系列,也兼容成本效益更高的Spartan系列,满足不同应用场合的需求。

XILINX的FIR Compiler通过提供这些特性,使得开发者能够快速、灵活地设计出满足特定性能指标的FIR滤波器,而无需从头编写底层硬件描述语言(如VHDL或Verilog)。此外,文档还可能涵盖了如何在XILINX的集成开发环境ISE(Integrated Software Environment)中使用该IP核,以及如何进行系统级的仿真和验证。

使用FIR Compiler时,用户通常需要定义滤波器的系数,这可能通过MATLAB或Simulink等高级工具生成,然后导入到FIR Compiler中。设计完成后,FIR Compiler会自动生成相应的硬件描述代码,用于在目标FPGA上实现。

XILINX的FIR Compiler是FPGA设计者手中强大的工具,它简化了复杂FIR滤波器的设计流程,提高了设计效率,同时确保了设计的性能和灵活性。对于需要在FPGA上实现高效数字信号处理的项目,这是一个不可或缺的资源。

相关推荐

liming945

- 粉丝: 0

最新资源

- CefSharp在爬虫应用中的实践技巧

- 智慧城市的废物预防:第二年研究记录

- 多功能RSS阅读器:Chrome扩展程序 RSS Reader

- 档案同步新工具:Archive-FreeFileSync软件介绍

- VC++图书借阅管理系统:源码及数据库应用教程

- GitHub Actions集成Postman: 使用Newman实现无头测试

- PSTU-labs项目深度解读与C++技术应用

- Spring 2021 HTML课堂作业:COVID中心网站开发

- _phone_to_website:构建并部署React Mobile应用_

- Java实现的控制权分配系统

- 人性化包装设计实践:论文探讨

- 安曼301d18中间软件开发技术解析

- logossim:探索开源、易于扩展的数字逻辑模拟器

- 深度Q网络(DQN)在迷宫求解中的实现与优化

- 清新风格中国烟草工作总结PPT模板下载

- 网络文化对青少年影响研究与应对策略分析